最近、 FPGA / FPGAの開発に関する多くの記事がHabrahabrに掲載されました 。 これは、同僚と他のユーザーの直接の参加の両方で起こりました。 このような記事は、この開発分野の普及に貢献しており、 ハードウェア開発全体の方向(「ハードウェア」と呼ばれる)にすでに大きな関心が寄せられていることがわかります。

この記事では、 ASICの開発の実質的に「手つかずの分野」に入り、 ASICチップでデジタルパーツ( IPブロック )を作成する興味深い側面について説明します。 この開発領域は、 FPGAよりもさらに狭くなっています。

ASIC (特定用途向け集積回路)は、特定の問題を解決するために特化した集積回路です。

私の記事では、製造されたチップで測定する前に、チップ内の単一のIPブロックの 消費電力を測定する一般的な方法を説明しています。 このような評価により、初期段階で次のことが可能になります。

- デジタルデータ処理アルゴリズムの異なるバージョンを比較します。

- 消費/デジタル損失の基準に従って、実装に最適なオプションを選択します。

- 特定のテクノロジによってリリースされたチップで作業する場合、非常に正確に数値で消費電力を推定します。

この方法では、いくつかの仮定を使用して、 HDL (デジタル回路記述言語)のアルゴリズムのいくつかの実装を非常に正確に比較できます。 私たちの場合、それはASICの最も人気のある開発言語であるVerilogになります。

複数の実装を比較するプロセスを高速化するための2つの仮定:

- IPブロックの完全な合成を行って最終的なレイヤーごとの実装を取得することはしません(消費にも影響するすべての寄生容量が含まれます)が、合成IPブロックのいわゆる理想的なワイヤ負荷モデルに制限されます 。 *絶対数のより正確な推定値は、拡張地形モードでの合成中に得られます(層状合成を使用)が、相対比較ではこれを無視できます。

- ワイヤロード合成後の「シュレッドツリー」の消費を評価して考慮することはできません。 それを評価するには、クリスタル内で完全な配線を行う必要があります。 同期回路では、動作中のユニット全体の消費に比べてかなりの数の消費が発生する可能性があります。 しかし、ブロックの異なる実装をほぼ同じトリガー領域と比較する場合、 「ブロックツリー」の消費はほぼ同じであると考えることができます。

消費量を測定するために必要なもの:

- ターゲットテクノロジのコンポーネントのライブラリ(Standard Cell Library)(130/90 / 65nm、メーカーがNDAで提供)

- 選択したコンポーネントライブラリに基づいてVerilogからネットリストを合成するプログラム

- 消費量推定プログラム

- IPブロックの動作モードをシミュレートしてログを記録するプログラム( ブロックの消費量の統計的推定値ではなく、動作モードでの消費量の正確な推定値を取得したい)

特に、 Synopsys DC(Design Compiler)を使用して消費量を合成および計算し、 Modelsimを使用して作業をシミュレートし、回路内の信号切り替えの数を記録しました。 同様のデータと結果は、他社のプログラムを使用して取得できます。

消費を得るには、 IPブロックの合成回路で1から0および0から1に切り替えられた回数と要素を知る必要があります(デジタル回路では、要素はこれら2つの状態にのみ存在できます)。 もちろん、何回何回切り替えたかの正確なデータを取得することはできませんが、統計データに基づいてそれらを計算します(この信号は全体の10%だけが切り替えられると考えます)が、消費の推定値は統計的になります。 また、比較するために、いくつかの実装の正確な推定値を取得する必要があります。 したがって、 テストベンチを使用してIPブロックの動作をシミュレートし、テストされたブロック内のすべてのスイッチング要素を記録します。

例を使用して段階ごとに評価プロセスを示します

例として、評価のために、 ADC (Analog-to-Digital Converter)の出力からデジタルデータ処理ユニットのソースコードを使用します。 そのタスクは、後続の処理のためにデジタルダウンシフト変換 (デジタル周波数ダウン変換)を実装するために、デジタル信号処理( DSP / DSP )を行うことです。 この例を使用して、 Verilog / VHDLで記述されたIPブロックの消費結果を取得できる手順を順番に説明します。 *例の一部の名前は、前述のデジタルブロックのソースコードをそのままレイアウトできないために変更されています。

さまざまなIPブロック実装のテストプロセスを自動化するために、次の3段階で順番に実行されるスクリプトを作成しました。

- ターゲットテクノロジのIPブロックの合成(この場合、 TSMC 90nmの合成、ライブラリ:典型)

- 合成された記述のシミュレーションの実行( ネットリスト )

- シミュレーションから収集されたスイッチングデータに基づく消費量の計算。

そして今、測定プロセス自体を段階的に行い、結果をコメント付きで

プロセスを自動化するために行われるように、各ステージでスクリプト内のコマンドを選択するか、コマンドに従ってそれらを連続して実行できます。

最初の段階のRun_srsスクリプト(Design Compiler):

saif_map -start

read_verilog〜/ srs / ddc_notch.v

read_verilog〜/ srs / ddc_qnt3b.v

read_verilog〜/ srs / ddc_intp.v

read_verilog〜/ srs / ddc_qsr0.v

read_verilog〜/ srs / ddc_qsr1.v

read_verilog〜/ srs / ddc_lpf0.v

read_verilog〜/ srs / ddc_qsr_lpf1.v

read_verilog〜/ srs / ddc_reg.v

read_verilog〜/ srs / ddc_top.v

current_design ddc_top

create_clock clk_ddc-ピリオド20

set_clock_uncertainty 0.15 [all_clocks]

コンパイル-gate_clock

change_names -rules verilog -hierarchy

write -format verilog -hierarchy -output ddc_top.v

write -format ddc -hierarchy -output ddc_top.ddc

report_area -hierarchy> ./log/area_ddc.rpt

出る

read_verilog〜/ srs / ddc_notch.v

read_verilog〜/ srs / ddc_qnt3b.v

read_verilog〜/ srs / ddc_intp.v

read_verilog〜/ srs / ddc_qsr0.v

read_verilog〜/ srs / ddc_qsr1.v

read_verilog〜/ srs / ddc_lpf0.v

read_verilog〜/ srs / ddc_qsr_lpf1.v

read_verilog〜/ srs / ddc_reg.v

read_verilog〜/ srs / ddc_top.v

current_design ddc_top

create_clock clk_ddc-ピリオド20

set_clock_uncertainty 0.15 [all_clocks]

コンパイル-gate_clock

change_names -rules verilog -hierarchy

write -format verilog -hierarchy -output ddc_top.v

write -format ddc -hierarchy -output ddc_top.ddc

report_area -hierarchy> ./log/area_ddc.rpt

出る

消費量計算の名前一致ログを有効にする

saif_map -start

ソースコードをコンパイルします

read_verilog ~/srs/ddc_notch.v read_verilog ~/srs/ddc_qnt3b.v read_verilog ~/srs/ddc_intp.v read_verilog ~/srs/ddc_qsr0.v read_verilog ~/srs/ddc_qsr1.v read_verilog ~/srs/ddc_lpf0.v read_verilog ~/srs/ddc_qsr_lpf1.v read_verilog ~/srs/ddc_reg.v read_verilog ~/srs/ddc_top.v current_design ddc_top

細断処理の設定( 制約 )のみを指定するだけで十分です。 そのような設定の複雑なブロックの場合は、多くを指定して、合成後の結果が期待どおりになるようにする必要があります。

create_clock clk_ddc -period 38.46 set_clock_uncertainty 0.15 [all_clocks]

gate_clockパラメーターのみでコンパイルします。これにより、合成中にブロックシャットダウン回路を自動的に挿入できます(FFがアクティブでない場合(フリップフロップ/レジスター)、 Verilogのレジスター記述に関する特定のルールに従います)。 これは、 ASICの回路のアクティブ消費を削減する最も重要な方法です)

compile -gate_clock

第2段階と第3段階の合成結果を書きます

change_names -rules verilog -hierarchy write -format verilog -hierarchy -output ddc_top.v write -format ddc -hierarchy -output ddc_top.ddc ddc_top.ddc — , . ddc_top.v — Verilog netlist

2番目のステージのvsim.doスクリプト(Modelsimでのログのシミュレーションと切り替え)

vlibの仕事

vmap work work

vlog -work work〜/ work / tsmc090.v

vlog -work work〜/ work / ddc_top.v

vlog -work work〜/ work / tb.v

vsim + notimingchecks -novopt work.tb + nowarn3017 + nowarn3722

90usを実行

power add -r tb / ddc_top / *

200usを実行

電力レポート-all -bsaif saif.saif

出る

vmap work work

vlog -work work〜/ work / tsmc090.v

vlog -work work〜/ work / ddc_top.v

vlog -work work〜/ work / tb.v

vsim + notimingchecks -novopt work.tb + nowarn3017 + nowarn3722

90usを実行

power add -r tb / ddc_top / *

200usを実行

電力レポート-all -bsaif saif.saif

出る

コンパイルしてシミュレートするライブラリを作成します

vlib work vmap work work

最初の段階で合成されたネットリスト (ddc_top.v)、シミュレーション用のTSMC 90nm要素ライブラリ(tsmc090.v)およびテストベンチ (tb)をコンパイルします。

vlog -work work ~/work/tsmc090.v vlog -work work ~/work/ddc_top.v vlog -work work ~/work/tb.v

テストベンチのVerilogコード(tb.v)

`timescale 1ps/1ps module tb; reg clk_ddc; reg rstz_ddc; reg in_valid; reg [2:0] in_i; reg [2:0] in_q; reg [2:0] i_temp; reg [2:0] q_temp; always @(posedge clk_ddc) if (~rstz_ddc) i_temp <= 'd0; else if (in_valid) i_temp <= $random % 8; always @(posedge clk_ddc) if (~rstz_ddc) q_temp <= 'd0; else if (in_valid) q_temp <= $random % 8; always @* case (i_temp) 3'd0: in_i = 4'b001; 3'd1: in_i = 4'b001; 3'd2: in_i = 4'b010; 3'd3: in_i = 4'b011; 3'd4: in_i = 4'b100; 3'd5: in_i = 4'b101; 3'd6: in_i = 4'b110; default:in_i= 4'b111; endcase always @* case (q_temp) 3'd0: in_q = 4'b001; 3'd1: in_q = 4'b001; 3'd2: in_q = 4'b010; 3'd3: in_q = 4'b011; 3'd4: in_q = 4'b100; 3'd5: in_q = 4'b101; 3'd6: in_q = 4'b110; default:in_q= 4'b111; endcase initial clk_ddc = 'd0; always #19230 clk_ddc = ~clk_ddc; //26 Mhz always @(posedge clk_ddc) if (~rstz_ddc) in_valid <= 'd0; else in_valid <= 'd1; initial begin rstz_ddc = 'd0; #80000; @(posedge clk_ddc); rstz_ddc = 'd1; @(posedge clk_ddc); @(posedge clk_ddc); #50000000; $display ($time); #50000000; $display ($time); #50000000; $display ($time); #400000000; end ddc_top ddc_top ( .clk_ddc ( clk_ddc ), .rstz_ddc ( rstz_ddc ), // APB .clk_apb ( 1'd0 ), .reg_adr ( 10'd0 ), .reg_we ( 1'd0 ), .reg_wd ( 32'd0 ), .reg_rd ( reg_rd ), .ddc_qi ( {in_q,in_i} ), .ddc_in_valid ( in_valid ), .ddc_out_i ( ), .ddc_out_q ( ), .ddc_out_valid ( ) );

最初にランダムに生成された入力データを入力し、実際の入力信号をシミュレートするモデルからのデータではないことに注意してください。 このケースでは、ノイズ下の信号のデジタル回路の消費量を測定することは同等です。 実際、実際の入力信号は「ホワイトノイズ」(ランダムジェネレーターの均一な分布)です。 正確には、限られた信号帯域幅とアナログ入力アンプの影響により理想的には「白」ではありませんが、これは一般にシミュレーションと消費測定の結果に影響しません。

正確なログ記録のために最適化せずに、 TSMCライブラリから時間関係をチェックせずにシミュレーションを開始します(特定の警告ライブラリも非表示にします)。

vsim +notimingchecks -novopt work.tb +nowarn3017 +nowarn3722

明確にするために初期初期化をスキップ

run 90us

そして、ブロック内のすべての信号のロギングを開始します

power add -r tb/ddc_top/*

動作モードで200mksのデータを収集します

run 200us

そして、収集されたデータをスイッチングアクティビティ交換形式(SAIF)形式でファイルに書き込み、3番目の段階で使用します。

power report -all -bsaif saif.saif

saifファイルのサンプルデータパーツ

テスト中に特定の内部ネットリスト信号が切り替えられた回数を示します。

(インスタンスdff_20_reg_6_ NET (フラグ(T0 0)(T1 2,000,000,000)(TX 0)(TC 0)(IG 0)) (n0(T0 100534440)(T1 99465560)(TX 0)(TC 1324)(IG 0)) (clk(T0 150002000)(T1 49998000)(TX 0)(TC 5200)(IG 0)) (xRN(T0 0)(T1 2,000,000,000)(TX 0)(TC 0)(IG 0)) (xSN(T0 0)(T1 2,000,000,000)(TX 0)(TC 0)(IG 0))

第3段階のスクリプトの実行(Design Compilerのsaifデータベースに基づいたブロック消費の測定)

read_ddc ./ddc_top.ddc

current_design ddc_top

read_saif -input ./saif.saif -instance tb / ddc_top

report_power -hierarchy -levels 1 -analysis_effort high> ./log/power_ddc.rpt

report_saif

current_design ddc_top

read_saif -input ./saif.saif -instance tb / ddc_top

report_power -hierarchy -levels 1 -analysis_effort high> ./log/power_ddc.rpt

report_saif

合成済みのネットリスト用に以前に保存したデータベースを読み取り、以前に取得したサイフを接続します

read_ddc ./ddc_top.ddc current_design ddc_top read_saif -input ./saif.saif -instance tb/ddc_top

消費電力の測定を開始し、ファイルに書き込みます

report_power -hierarchy -levels 1 -analysis_effort high > ./log/power_ddc.rpt

すべての内部信号が正しく比較され、消費の分析で考慮されていることを確認します。 また、同時に、saifファイルでスイッチング統計を見つけることができない信号はありませんでした(ターゲットライブラリの合成ネットリストではなく、ソースVerilogをシミュレートすると、信号の50%で機能します)。

report_saif

この例のこのコマンドのレポート。

-------------------------------------------------- ------------------------------

伝播されるユーザーのデフォルト

オブジェクトタイプ注釈付き(%)アクティビティ(%)アクティビティ(%)合計

-------------------------------------------------- ------------------------------

ネット2029(100.00%)0(0.00%)0(0.00%)2029

ポート655(100.00%)0(0.00%)0(0.00%)655

ピン7492(100.00%)0(0.00%)0(0.00%)7492

-------------------------------------------------- ------------------------------

そして今、あなたは1つのコマンドで3つのスクリプトすべてを連続して実行し、この例で何が起こったのかを見ることができます

dc_shell source ./run_srs ; vsim do ./vsim.do ; dc_shell source ./run

最終報告書はこちら

Library(s) Used: typical (File: ~/lib/lib90nm/typical.db) Power-specific unit information : Voltage Units = 1V Capacitance Units = 1.000000pf Time Units = 1ns Dynamic Power Units = 1mW (derived from V,C,T units) Leakage Power Units = 1pW -------------------------------------------------------------------------------- Switch Int Leak Total Hierarchy Power Power Power Power % -------------------------------------------------------------------------------- ddc_top 6.60e-02 0.315 1.10e+08 0.491 100.0 r313 (ddc_top_DW01_inc_0) 0.000 0.000 1.40e+05 1.40e-04 0.0 ddc_reg (ddc_reg) 0.000 1.27e-03 3.78e+06 5.06e-03 1.0 ddc_intp (ddc_intp) 8.41e-03 3.34e-02 5.75e+06 4.76e-02 9.7 ddc_qnt3b (ddc_qnt3b) 2.59e-03 9.17e-03 2.20e+06 1.40e-02 2.8 ddc_qsr_lpf1(ddc_qsr_lpf1) 2.44e-02 0.110 1.54e+07 0.150 30.4 ddc_notch3 (ddc_notch_1) 1.75e-03 8.81e-03 1.05e+07 2.11e-02 4.3 ddc_notch2 (ddc_notch_2) 1.69e-03 8.81e-03 1.05e+07 2.10e-02 4.3 ddc_notch1 (ddc_notch_3) 1.69e-03 8.81e-03 1.05e+07 2.10e-02 4.3 ddc_notch0 (ddc_notch_0) 2.16e-03 9.98e-03 1.05e+07 2.27e-02 4.6 ddc_qsr1 (ddc_qsr1) 1.46e-03 2.98e-03 4.32e+05 4.86e-03 1.0 ddc_lpf0_q (ddc_lpf0_1) 9.79e-03 5.75e-02 3.80e+06 7.11e-02 14.5 ddc_lpf0_i (ddc_lpf0_0) 1.06e-02 6.05e-02 3.90e+06 7.50e-02 15.3 ddc_qsr0 (ddc_qsr0) 1.33e-03 2.68e-03 2.34e+05 4.24e-03 0.9

総消費量は3つの要素で構成されます。

- セル漏れ電力 -漏れ電流。 生産技術(90/65 / 28nm)および回路の動作条件(温度/電圧)に依存する静的コンポーネント。 計算値はブロック面積に比例します。

- セル内部電力 -ライブラリコンポーネントの入力/出力の状態が変化したときに発生する電流( セル -例:論理「または」ORX2、DFFトリガー)。 動的コンポーネント。

- 正味スイッチング電力 - スイッチング時のコンポーネントの出力容量の再充電に関連する電流。 動的コンポーネント。

この例では、26 MHzのクロッキングで、デジタル処理ユニットがアクティブモードで90 nmで491μAを消費するという結果が得られました。

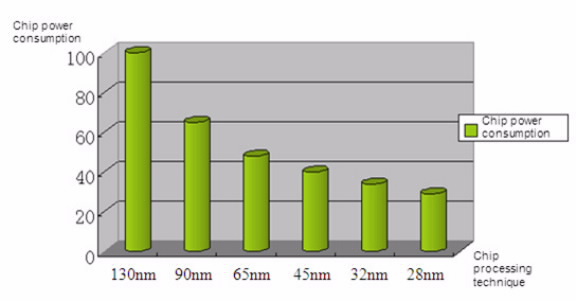

次の記事では、FPGAに実装された同じIPブロックの消費量を分析できます。 このため、 アルテラ/ザイリンクス/ Microsemiの各メーカーは、CAD(コンピューター支援設計)システムの一部として特殊なプログラムを用意しています。 特に、アルテラにはPowerPlay Power Analysisと呼ばれるこの部分があり、これによりFPGAについて上記のプロセスを大幅に自動化できます。 FPGAの IPブロックを「プログラム」する機能には、消費量が大幅に増加するという形で明確なマイナス要素があることがよく知られています。 ASIC 90nmと28nmテクノロジーを使用した最新のFPGAで同じIPブロックの実装を比較すると、消費量の差は数十倍に達する可能性があります。