おそらく、この記事を読んだ後、トランジスタに同じサイズのラジエーターを置く必要はないでしょう。

この記事の翻訳。

翻訳者からの小さな魅力:

まず、この翻訳では、用語の翻訳に重大な問題が発生する可能性があります。電気工学と回路を十分に扱っていませんでしたが、まだ何かを知っています。 また、すべてを可能な限り明確に翻訳しようとしたため、ブートストラップ、MOSトランジスタなどの概念は使用しませんでした。 第二に、スペルミスが間違いを犯しにくい場合(エラーを示すワープロへの称賛)、句読点の間違いは非常に簡単です。

そして、これらの2つの点について、できる限りコメントをお願いします。

次に、この記事のトピックについて詳しく説明します。MK、Arduino、<名前の挿入>、および回路自体の設計、さらにはエンジン接続回路の詳細については説明していません。 通常、次のようになります。

-エンジンを取ります

-コンポーネントを取ります

-コンポーネントとエンジンを接続します

-...

-利益!1!

ただし、L239xを介してPWMモーターを一方向に単純にねじるよりも複雑な回路を構築するには、通常、フルブリッジ(またはHブリッジ)、電界効果トランジスタ(またはMOSFET)、およびそれらのドライバーの知識が必要です。 何も制限がない場合、pチャンネルとnチャンネルのトランジスターをフルブリッジに使用できますが、エンジンが十分に強力な場合、pチャンネルトランジスターを多数のラジエーターで吊るす必要があり、クーラーを追加する必要がありますが、完全に破棄する場合は、その後、他のタイプの冷却を試すか、回路でnチャネルトランジスタのみを使用できます。 しかし、nチャネルトランジスタには小さな問題があります。「良い方法で」それらを開くことは時々非常に困難です。

だから私は正しいアウトラインを得るのに役立つ何かを探していました、そして、Syed Tahmid Mahbubという名前の若い男性のためのブログ記事を見つけました。 この記事を共有することにしました。

そして、これらの2つの点について、できる限りコメントをお願いします。

次に、この記事のトピックについて詳しく説明します。MK、Arduino、<名前の挿入>、および回路自体の設計、さらにはエンジン接続回路の詳細については説明していません。 通常、次のようになります。

-エンジンを取ります

-コンポーネントを取ります

-コンポーネントとエンジンを接続します

-...

-利益!1!

ただし、L239xを介してPWMモーターを一方向に単純にねじるよりも複雑な回路を構築するには、通常、フルブリッジ(またはHブリッジ)、電界効果トランジスタ(またはMOSFET)、およびそれらのドライバーの知識が必要です。 何も制限がない場合、pチャンネルとnチャンネルのトランジスターをフルブリッジに使用できますが、エンジンが十分に強力な場合、pチャンネルトランジスターを多数のラジエーターで吊るす必要があり、クーラーを追加する必要がありますが、完全に破棄する場合は、その後、他のタイプの冷却を試すか、回路でnチャネルトランジスタのみを使用できます。 しかし、nチャネルトランジスタには小さな問題があります。「良い方法で」それらを開くことは時々非常に困難です。

だから私は正しいアウトラインを得るのに役立つ何かを探していました、そして、Syed Tahmid Mahbubという名前の若い男性のためのブログ記事を見つけました。 この記事を共有することにしました。

多くの場合、トップレベルスイッチとして電界効果トランジスタを使用する必要があります。 また、多くの状況で、電界効果トランジスタを上位レベルと下位レベルの両方のキーとして使用する必要があります。 たとえば、ブリッジ回路。 部分ブリッジ回路には、1つの上位レベルMOSFETと1つの下位レベルMOSFETがあります。 フルブリッジ設計では、2つの上位レベルMOSFETと2つの下位レベルMOSFETがあります。 このような状況では、高レベルと低レベルの両方のドライバーを一緒に使用する必要があります。 このような場合に電界効果トランジスタを制御する最も一般的な方法は、MOSFETの下位レベルと上位レベルのドライバキーを使用することです。 間違いなく、最も人気のあるドライバーチップはIR2110です。 そして、この記事/教科書でそれについてお話します。

IR WebサイトからIR2110のドキュメントをダウンロードできます。 ダウンロードリンクはこちら: http : //www.irf.com/product-info/datasheets/data/ir2110.pdf

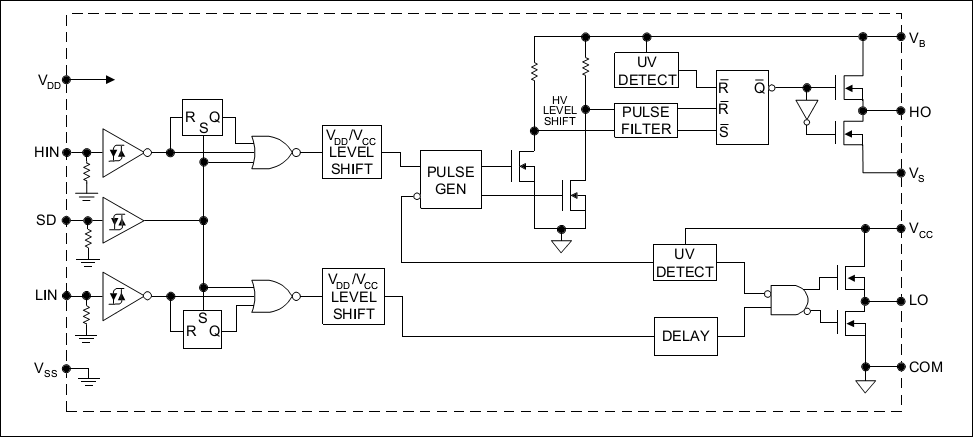

まず、ブロック図と、連絡先の説明と場所を見てみましょう。

図1-IR2110の機能ブロック図

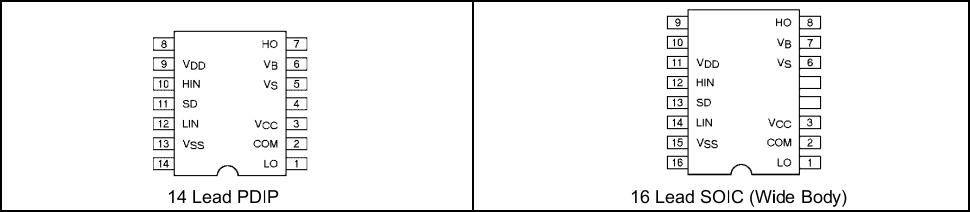

図2-IR2110のピン配列

図3-IR2110ピンの説明

また、IR2110は、出力実装用の14ピンPDIPと表面実装用の16ピンSOICの2つのケースで利用できることにも言及する価値があります。

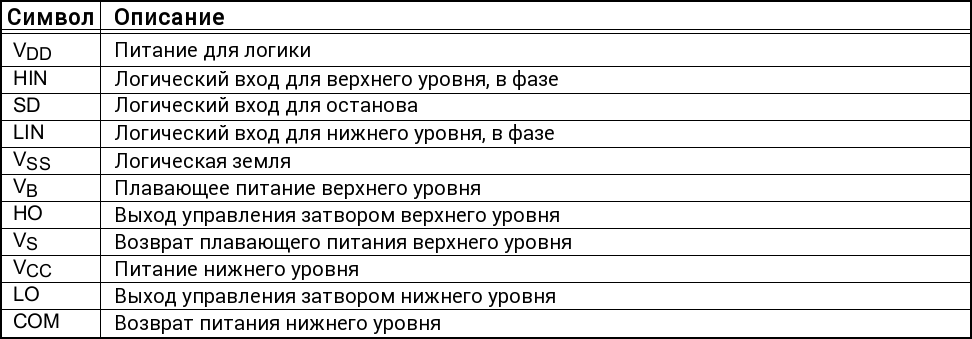

次に、さまざまな連絡先について説明します。

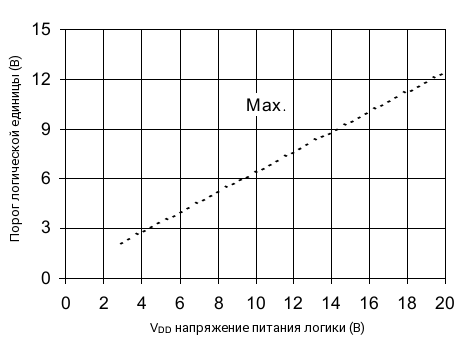

VCCは低レベルの電源で、10V〜20Vの範囲である必要があります。 VDDはIR2110の論理電源であり、+ 3V〜+ 20V(VSSに対して)でなければなりません。 使用することを選択した実際の電圧は、入力信号の電圧レベルによって異なります。 スケジュールは次のとおりです。

図4-論理1の電力依存性

通常、+ 5VのVDDが使用されます。 VDD = + 5Vの場合、ロジック1の入力しきい値は3Vよりわずかに高くなります。 したがって、電圧がVDD = + 5Vの場合、IR2110を使用して、入力「1」が3(一部)ボルトより高いときに負荷を制御できます。 これは、ほとんどの回路が通常約5Vの電力を持っているため、IR2110をほとんどすべての回路に使用できることを意味します。 マイクロコントローラーを使用する場合、出力電圧は4Vより高くなります(結局、マイクロコントローラーの電源電圧はVDD = + 5Vであることが非常に多いためです)。 SG3525またはTL494または別のPWMコントローラーを使用する場合、おそらく10Vを超える電圧で電力を供給しなければなりません。つまり、論理ユニットの出力には8Vを超える電圧が発生します。 したがって、IR2110はほぼどこでも使用できます。

マイクロコントローラまたは3.3V出力を生成するチップ(dsPIC33など)を使用する場合、VDDを約+ 4Vに下げることもできます。 IR2110を使用して回路を設計する際、IR2110のVDDが+ 4V未満に選択された場合、回路が適切に動作しないことがあることに気付きました。 したがって、+ 4V未満のVDDを使用することはお勧めしません。 ほとんどの回路では、信号レベルの電圧が「1」として4V未満ではないため、VDD = + 5Vを使用します。

回路内の何らかの理由で論理「1」の信号レベルの電圧が3V未満の場合、レベルコンバーター/レベルトランスレーターを使用する必要があります。電圧を許容範囲まで上げます。 このような状況では、4Vまたは5Vに上げて、IR2110 VDD = + 5Vを使用することをお勧めします。

次に、VSSとCOMについて説明します。 VSSはロジックのランドです。 COMは「低レベルリターン」です。基本的に、ドライバーの低レベルアースです。 それらは独立しているように見えるかもしれませんが、ドライバー出力とドライバー信号ロジックを分離することはおそらく可能であると考えるかもしれません。 しかし、それは間違っているでしょう。 内部的には接続されていませんが、IR2110は非絶縁ドライバーです。つまり、VSSとCOMの両方をグランドに接続する必要があります。

HINとLINは論理入力です。 HINの高信号は、上位キーを制御することを意味します。つまり、HOで高レベル出力が実行されます。 HINの低信号は、高レベルMOSFETを無効にすることを意味します。つまり、低レベル出力はHOにあります。 HOへの出口は、高低にかかわらず、地面との関係ではなく、VSとの関係で考慮されます。 VCC、VB、およびVSを使用したアンプ回路(ダイオード+コンデンサ)が、MOSFETを制御するためのフローティング電源をどのように提供するかについては、すぐに説明します。 VSはフローティングパワーリターンです。 高いレベルでは、VSに対するHOのレベルはVBのレベルに等しくなります。 低レベルでは、HOのレベルはVSに対してVSにほぼ等しく、実質的にゼロです。

高いLIN信号は、低いキーを制御することを意味します。つまり、LOで高レベル出力が実行されます。 低LIN信号は、低レベルMOSFETを無効にすることを意味します。つまり、低レベル出力はLOにあります。 LOへの出口は比較的陸地と見なされます。 信号が高い場合、LOのレベルは、VSS、実際にはグランドと比較して、VCCのレベルと同じです。 信号が低い場合、LOのレベルはVSSのレベルと同じで、VSSを基準にして実際はゼロです。

SDは停止制御として使用されます。 レベルが低い場合、IR2110はオンになります-停止機能は無効になります。 このピンがハイのとき、出力がオフになり、IR2110制御が無効になります。

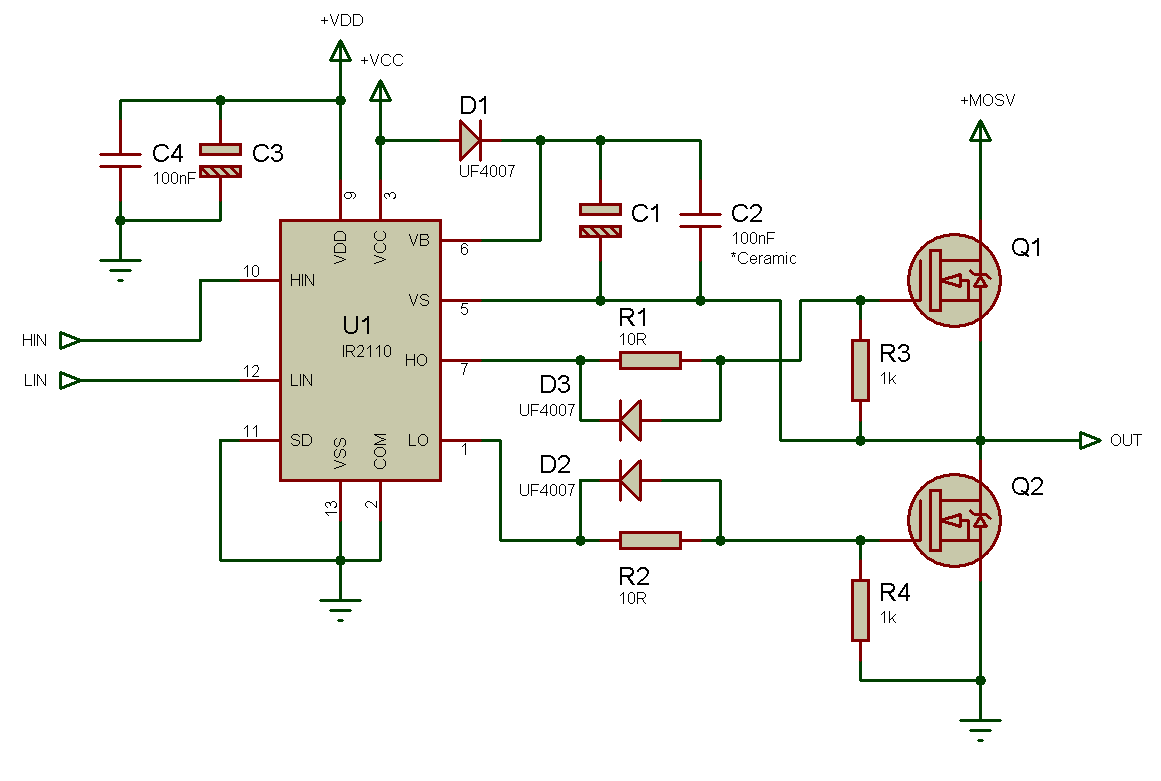

ここで、MOSFETを上下キーとして制御するためのIR2110の頻繁な構成(ハーフブリッジ回路)を見てみましょう。

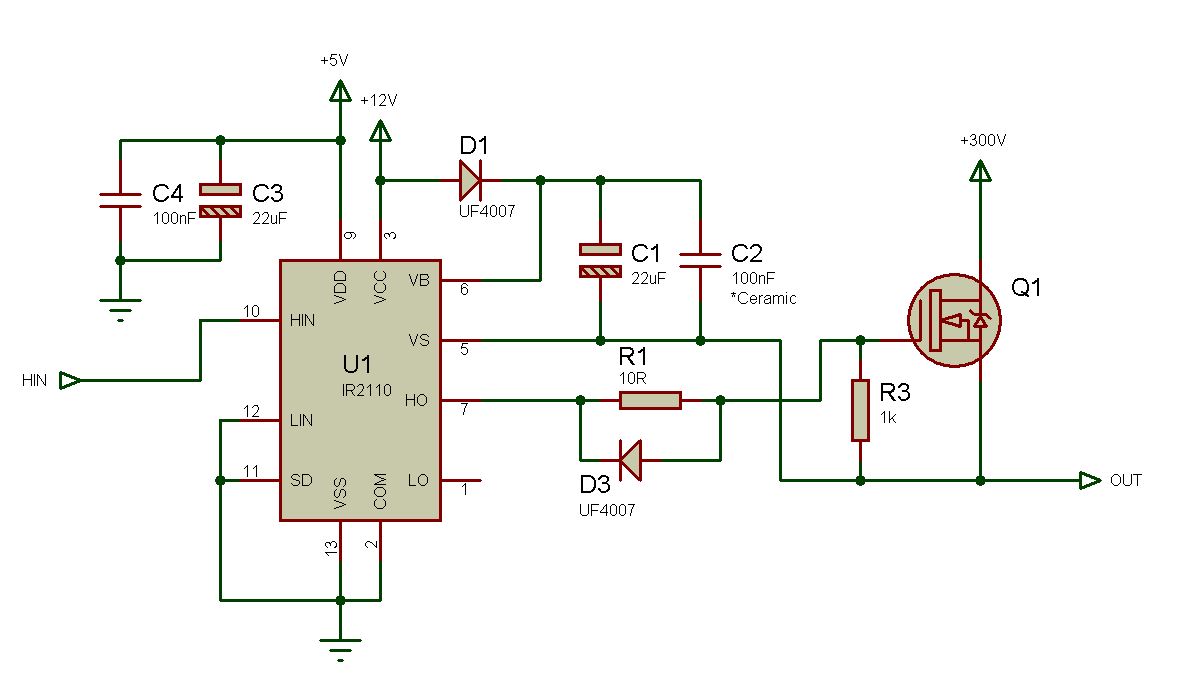

図5-ハーフブリッジを制御するIR2110の基本回路

D1、C1、C2とIR2110が増幅回路を形成します。 LIN = 1でQ2がオンになると、1つのダイオードが+ VCCより下にあるため、C1とC2がVBレベルに充電されます。 LIN = 0およびHIN = 1の場合、C1およびC2の電荷を使用して、ソースレベルQ1を超える電圧(この場合はVB)を追加し、トップキー構成のQ1を制御します。 Q1に必要な電荷を供給するのに十分であるように、C1で十分に大きな容量を選択する必要があります。これにより、Q1が常にオンになります。 また、充電プロセスには時間がかかり、MOSFETをオンに維持するのに十分な電圧レベルにならないため、C1の容量が大きすぎないようにする必要があります。 電源を入れたときに時間がかかるほど、必要な容量が大きくなります。 したがって、周波数を低くするには、C1の容量を大きくする必要があります。 デューティサイクルを大きくするには、より大きなC1容量が必要です。 もちろん、容量を計算するための公式がありますが、このためには多くのパラメータを知る必要があり、それらのいくつかは、たとえばコンデンサの漏れ電流を知らない場合があります。 したがって、おおよその容量を評価しました。 50Hzなどの低周波数では、47uFから68uFの容量を使用します。 30〜50kHzなどの高周波では、4.7uF〜22uFの容量を使用します。 電解コンデンサを使用しているため、このコンデンサと並列にセラミックコンデンサを使用する必要があります。 増幅コンデンサがタンタルの場合、セラミックコンデンサはオプションです。

D2とD3はMOSFETゲートを迅速に放電し、ゲート抵抗をバイパスしてトリップ時間を短縮します。 R1とR2は電流制限ゲート抵抗です。

+ MOSVは最大500Vです。

+ VCCは干渉を受けずにソースから供給される必要があります。 フィルタリングのために、+ VCCからグランドにフィルタリングおよび絶縁コンデンサを取り付ける必要があります。

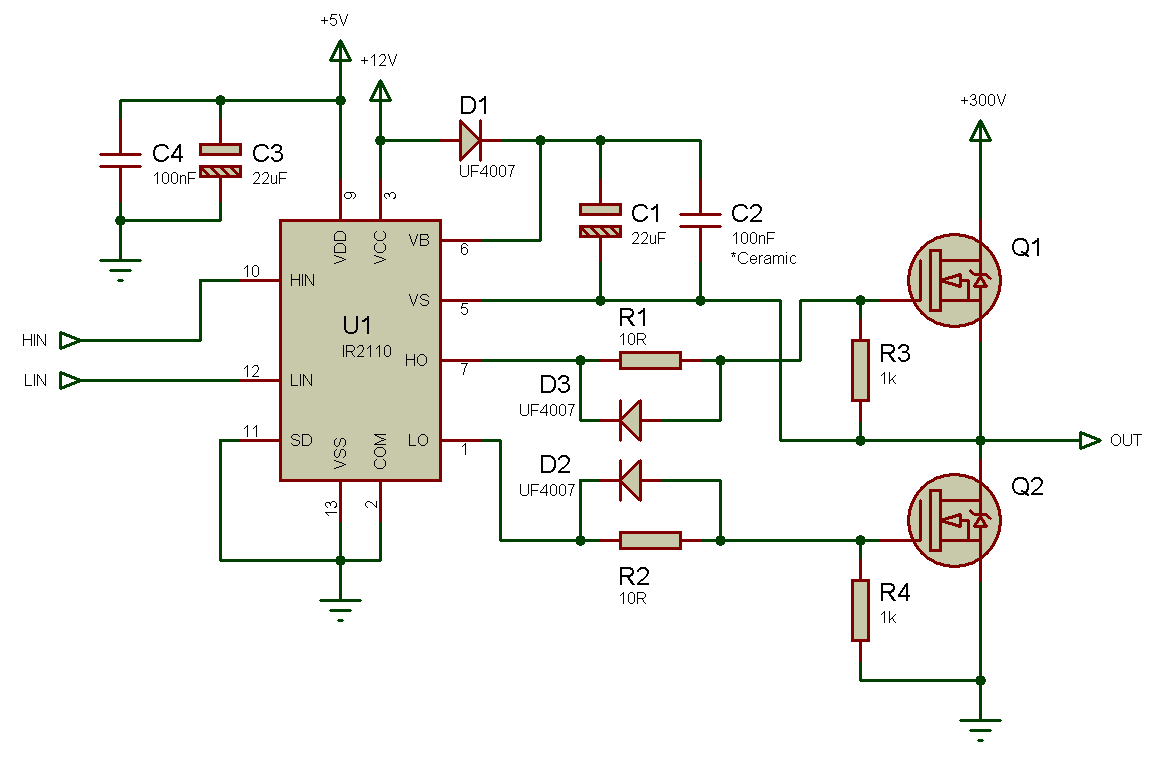

次に、IR2110を使用したいくつかの回路例を見てみましょう。

図6-高電圧ハーフブリッジ用のIR2110を使用したスキーム

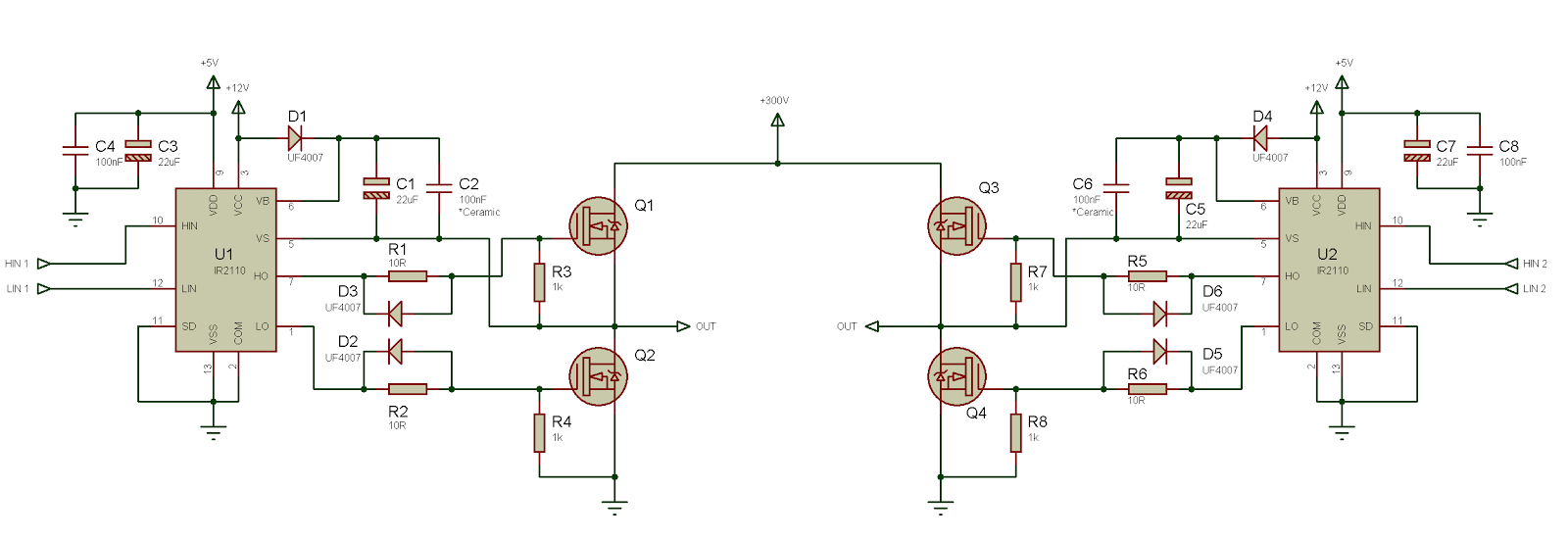

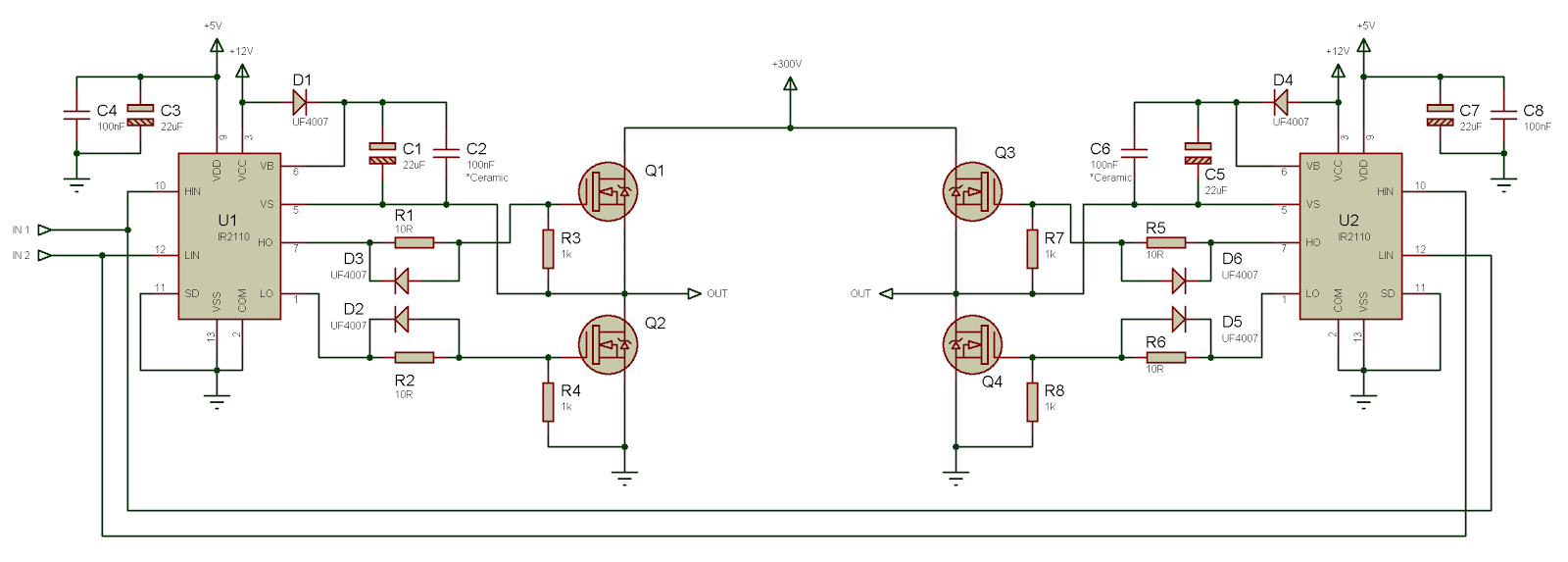

図7-独立したキー管理を備えた高電圧フルブリッジのIR2110の図(クリック可能)

図7では、フルブリッジの制御にIR2110が使用されています。 複雑なことは何もありませんが、これで理解できたと思います。 ここでかなり一般的な簡略化を適用することもできます。HIN1をLIN2に接続し、HIN2をLIN1に接続します。これにより、4ではなく2つの入力信号のみを使用して4つのキーすべてを制御できます。これを図8に示します。

図8-2つの入力を備えたキー管理を備えた高電圧フルブリッジのIR2110によるスキーム(クリック可能)

図9-高電圧トップレベルドライバーとしてIR2110を使用した図

図9では、IR2110がトップレベルドライバーとして使用されています。 回路は非常にシンプルで、上記と同じ機能を備えています。 考慮する必要があるものがあります-下位レベルのキーがなくなったため、OUTからグランドに接続された負荷が必要です。 そうしないと、アンプのコンデンサが充電できなくなります。

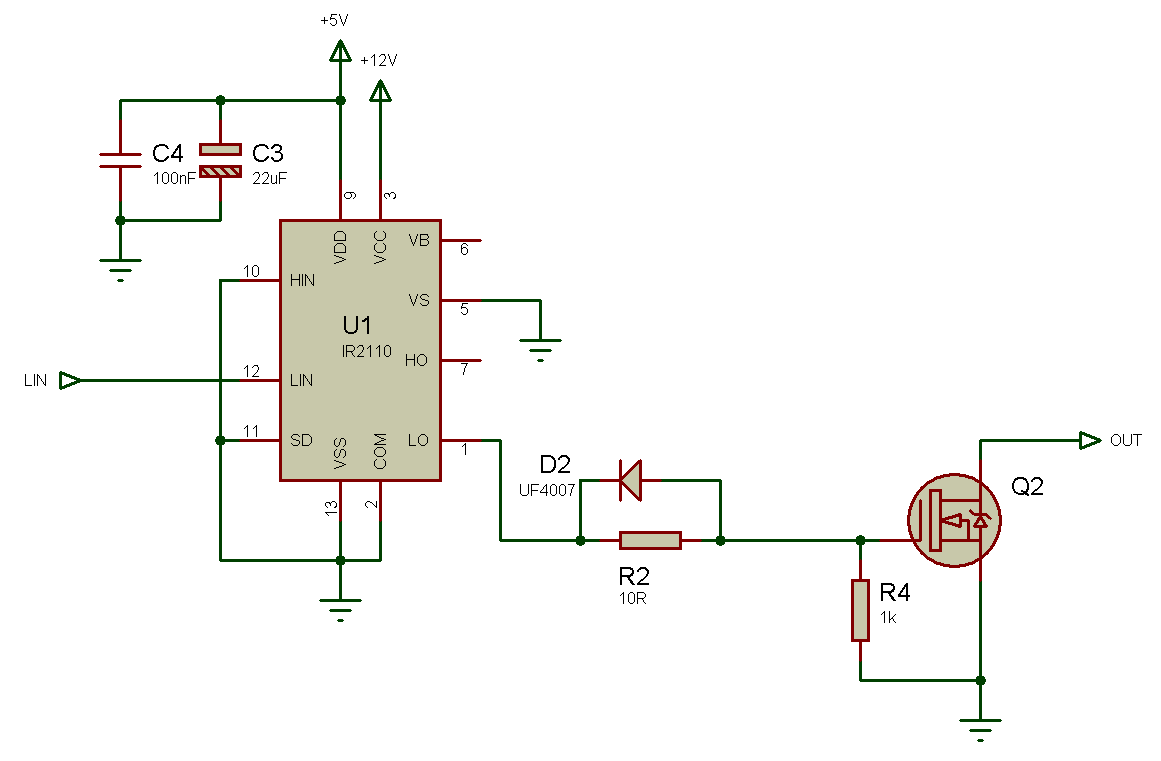

図10-下位レベルのドライバーとしてIR2110を使用した図

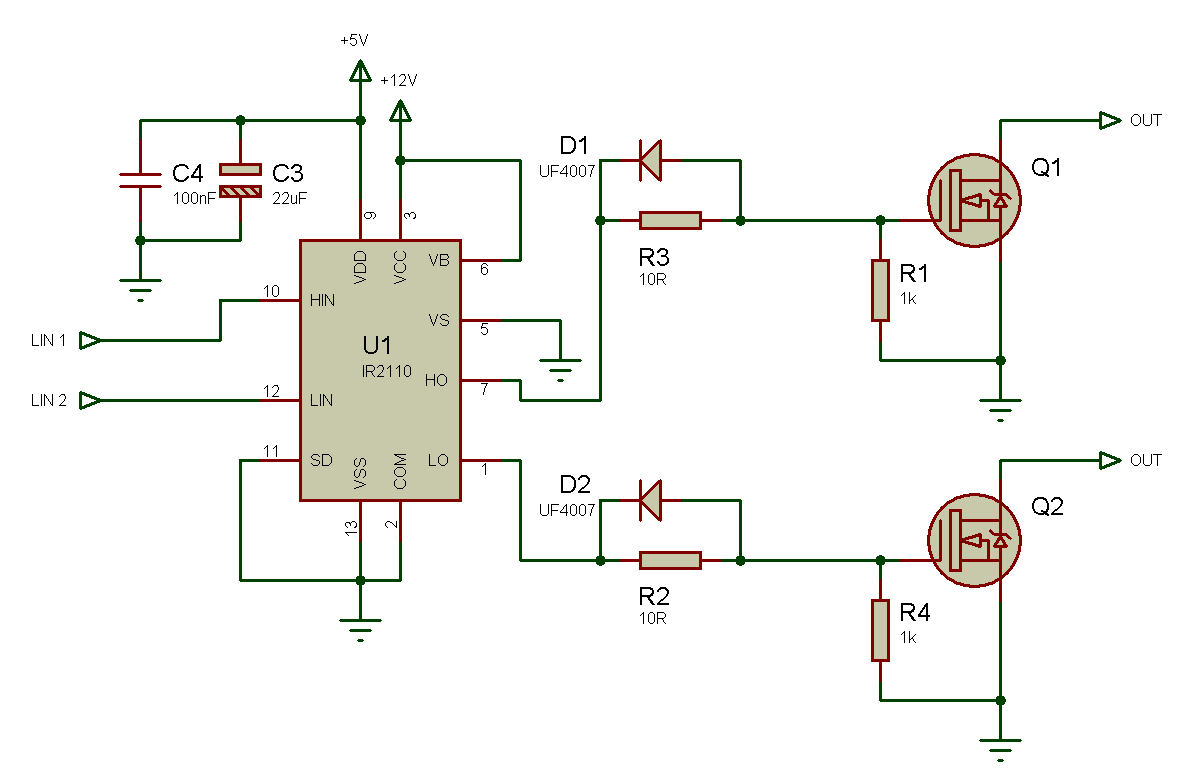

図11-デュアル低レベルドライバーとしてIR2110を使用した図

IR2110に問題があり、すべてが絶えずクラッシュ、燃焼、または爆発する場合は、もちろん、すべてを慎重に設計したのに、ゲートソース抵抗を使用していないためです。 ゲートウェイソースの抵抗について決して忘れないでください 。 興味がある場合は、ここでの私の経験について読むことができます(抵抗器が損傷を防ぐ理由も説明します): http : //tahmidmc.blogspot.com/2012/10/magic-of-knowledge.html

さらに読むには、これをお勧めします: http : //www.irf.com/technical-info/appnotes/an-978.pdf

多くのフォーラムで、人々がIR2110の回路設計に苦労しているのを見ました。 また、自信を持って一貫して成功するドライバー回路をIR2110で構築する前に、多くの困難を抱えていました。 IR2110のアプリケーションと使用方法を非常に慎重に説明し、途中ですべてを説明し、多数の例を使用してみました。これがIR2110での取り組みに役立つことを願っています。