多かれ少なかれ適切かつ深刻なプロジェクトの時期が来たとき、それぞれより多くの問題があり、私はグーグルをより集中的に使い始め、私の質問への答えを探し始めました。 ここで、「タイミング分析」や「設計上の制約」などのひどいフレーズが出くわすようになりました。読んで少し洞察を得たとき、非常に重要なものを見逃していたことに気付きました。 最初はこれらの未知の構成要素を恐れてパニックに陥りました。結局、最初のプロジェクトはそれらがなくても正常に動作しました。周波数は数十MHzしかなかったからです。 しかし、より高い周波数とより複雑なプロジェクトになると、徹底的な一時的な分析と最適化なしにはできません。 人々とやり取りしたとき、私たちの開発者全員がこれらのプロセスに十分に精通しているわけではないことに驚いたのですが、これはおそらくロシア語でのドキュメントと説明が非常に少ないためです。 そのため、Microsemiのツール(おそらくActel)を使用して、作業中に蓄積したものをFPGAと共有することにしました。 この投稿は、完全に正確であると主張するものではなく、棚に知識を置き、おそらく誰かが同じことをするのを助けたいという願望の結果です。 すべてのコメントと提案を歓迎します。

同期回路と基本的な定義

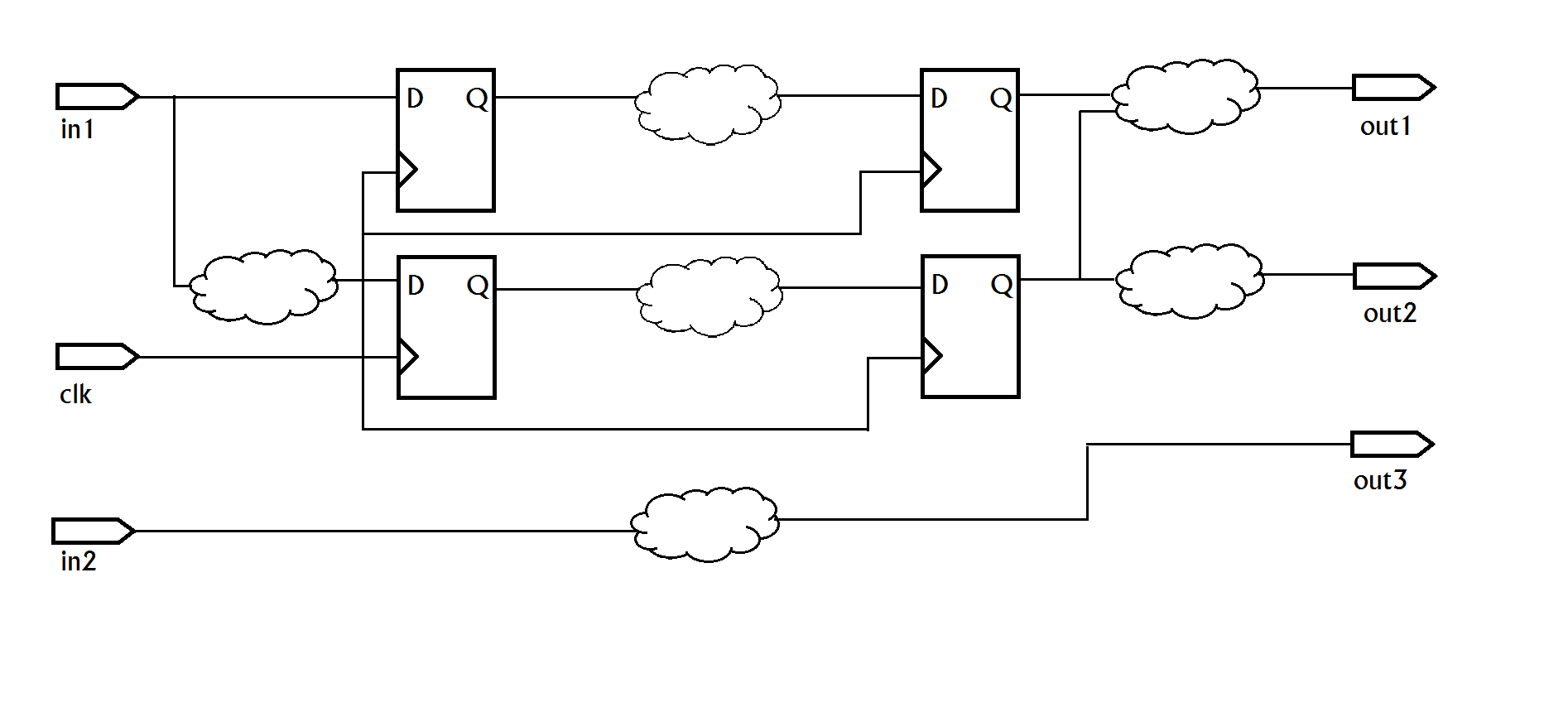

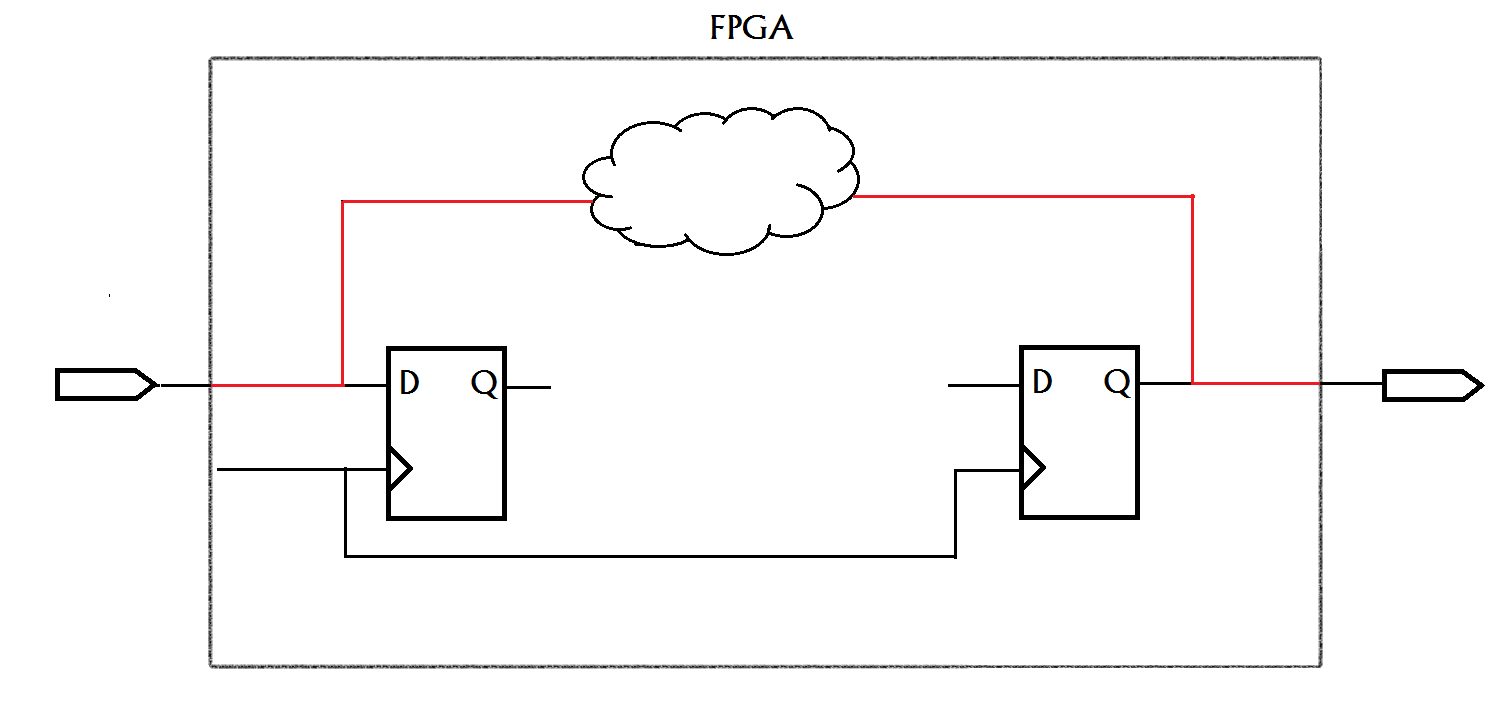

したがって、原則として、同期回路を扱っています。 このようなスキームは、次の要素で構成されています。

- I / Oポート

- 順次要素(トリガー);

- 組み合わせ論理(ゲート)。

これらの要素の接続は、動作中にデバイスを通過する信号パスを構成します。 実際、私はすでに重要な概念- パスを概説しました。 デバイスのパフォーマンス、特に最大クロック周波数、プロジェクトの主な要件の1つ、開発者がこれまで長い間苦労してきたことを決定するだけです。

信号は、マイクロ回路の入力端子から移動を開始し、順次および組み合わせ要素を通過して、出力端子に到達します。 クロックソース(CLK)は、クロック信号のエッジ(ほとんどの場合、エッジに沿って)で入力の状態を記憶する回路のすべてのトリガーをクロックします。 トリガー間(および入力/出力ポート間)は組み合わせロジックです。 信号パスには2種類の遅延があります。

- 要素の遅延(セル遅延);

- 伝播遅延;

通常、それらの比率は50/50です。つまり、組み合わせ回路の野生のパスは、次のバルブの入力からその出力までの遅延と通信回線に沿った信号の伝播との間で半分に分割されます。 回路の最大遅延は、 クリティカルパス 、つまり最長パスに対応します。これは、デバイスの最長期間とそれに応じた最大周波数を決定します。 ここでは、いくつかの基本的な概念を考慮する必要があります。

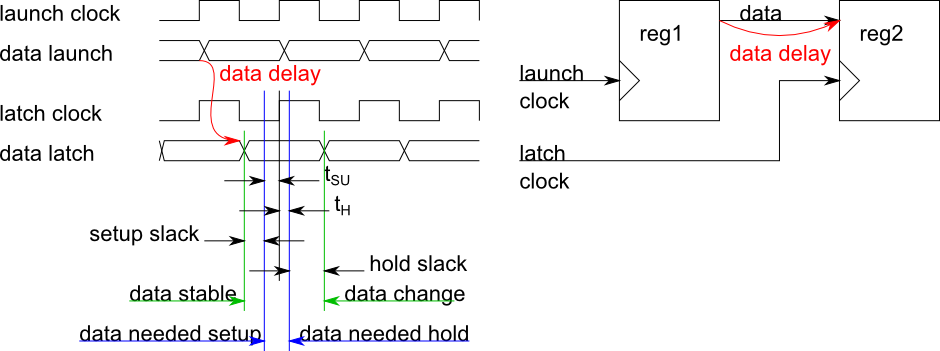

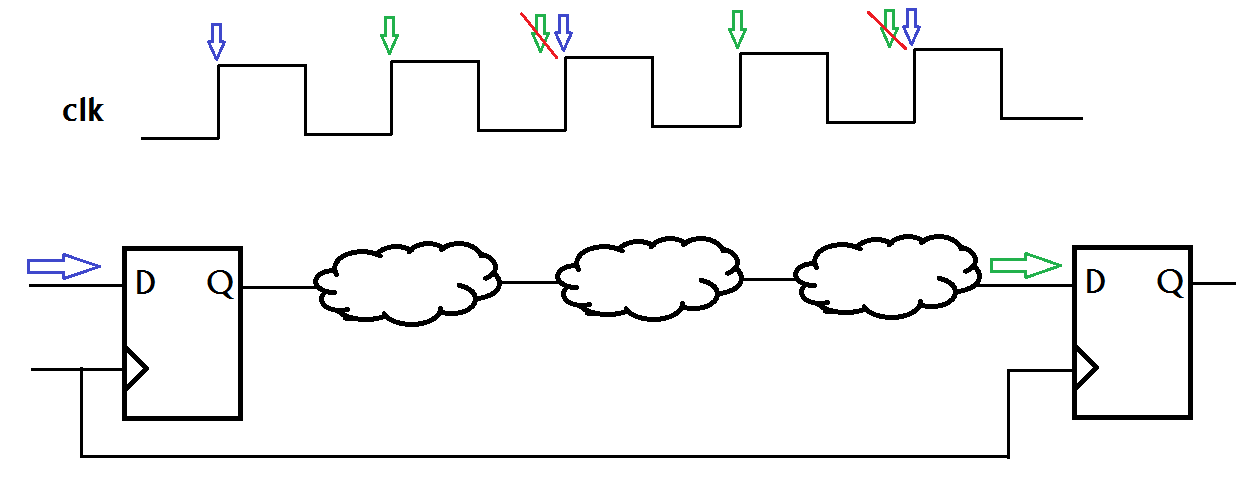

当然、信号を送信するとき、相互作用の2つの側面-ソースとレシーバーが明らかに表示されます。 これらはパスの終点です。 エンドポイントは、I / Oポートおよびトリガーにすることができます。 トリガーについて詳しく見てみましょう。 この例では、1つのクロック信号によってクロックが供給され、1つのトリガーの出力Qから2番目のトリガーの入力Dへのパスが実行されます。 クロック信号は1つだけですが、この例では2つの名前を付けます。

- 起動クロック-フロントに沿って、トリガー1の出力Qに新しいデータが到着します。

- ラッチクロック-前面では、トリガー2は現在入力Dにあるものを記憶します。

データは上記の要因による遅延で配信されるため、トリガー2の入力Dの信号はすぐには現れません。 これにより、次の特性が得られます。

- セットアップ時間(t su )-信号を受信機のフロントclkに設定する時間。

- 保持時間(t h )-受信機のフロントclkの後に信号を保持する時間。

- Slackは、 t suおよびt h の時間マージンを決定します。

t suとt hは一種の廊下を形成し、そのロッドはフロントラッチクロックです。 これで、レシーバーの入力Dでの信号の要件は単純になりました。このコリドー内で変更されるべきではありません。 つまり、理想的なケースでは、左の境界のかなり前に確立し、右の境界の少し後に値を新しい値に変更します。 これと同じタイムリザーブはSlackと呼ばれます。 Slackが正の数である場合、すべてが整然としており、データは必要な時間にレシーバー入力に到着し、負の場合-指定されたパスが時間特性を満たさない、つまり、データが必要な時間間隔外に入力に到着するため、デバイスは正しく動作しません。

実際、ここから困難が始まります。 数十個のトリガーを使用するトレーニングスキームではなく、グラフィックRTLモデルを表示するときに頭痛の種となる複雑なHDL記述がある場合、パフォーマンスが大幅に低下するような長いパスの可能性が大幅に増加します。 このプロセスを制御し、IDEにプロジェクトの一時的な特性に対する希望を伝えるために、後者にはいくつかの便利なツールが含まれています。

タイミング制約の設定

開発者は、新しいデバイスの設計を開始する前に、このデバイスの要件とパフォーマンスに関する可能な限り完全な情報を入手する必要があります。 まず第一に、これらはこのシステムの時間的特性です。 そして、それらが彼自身に知られているとき、あなたはこれを設計ツールに報告する必要があり、それから時間の制約または時間の 制約が救いに来ます。 時間の制約-これは、プロジェクトの時間的特性の要件に関する情報であり、理解可能な言語環境で規定されます。これは、ほとんどの場合Synopsis Design Constraints、SDCです。 これは、Tclに基づくFPGAの一時的な(およびそれだけではない)制限を記述するための事実上の標準です。Tclは、偶然にも、機器の開発を自動化するために広く使用されています。

これらの説明は* .sdcファイルに配置され、プロジェクトに添付されます。 このファイルの消費者は、開発者の要件を満たすようにクリスタルを繁殖しようとするあらゆる種類のオプティマイザーと、後で説明する一時的なアナライザーです。 Sdcファイルは複雑ではありません。実際には、引数とその値を持つコマンドの列挙です。 説明では、たとえば、1つのコマンドを複数の行に配置するために、特殊文字を含むTcl構文を使用できます(また使用する必要があります)。

そこで、いくつかの基本的なコマンドをリストし、それらが何を説明しているかを把握します。 最初のチームであり、絶対にあらゆるデザインに不可欠なものです。

create_clock -name name -period period_value [-waveform edge_list] source

このコマンドを使用して、回路内のクロック信号を特定し、その特性を説明します。

制約名

-name name

期間

-period period_value

デューティ(デフォルト2)、角括弧はオプションの引数を示します

[-waveform edge_list]

信号ソース(ピン、ポート)

source

クロック信号に関するCADツールの知識は最も重要です。これがないと、分析や最適化について話すことができないためです。 さらに、コマンドset_clock_latency、set_clock_uncertaintyなどを使用してクロック信号に関する情報をさらに絞り込むことができますが、環境で設定されたデフォルト値に依存して、ここではこれを考慮しません。 例として:

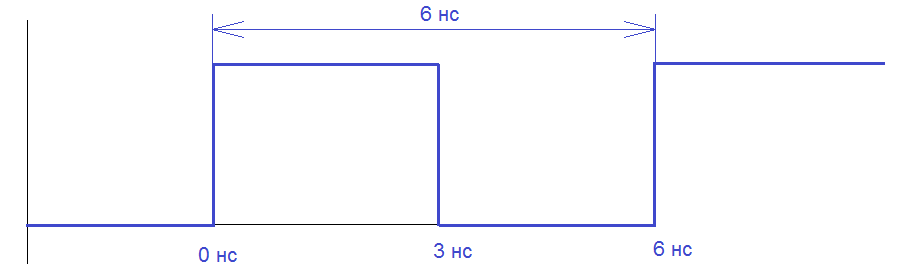

create_clock -name {my_clock} –period 6 –waveform {0 3} {CLK}

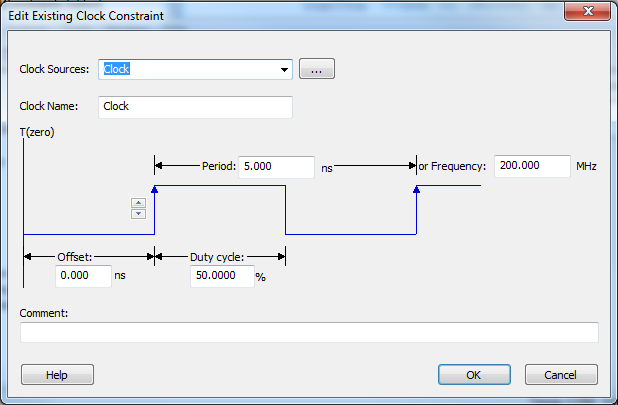

このコマンドは、6 nsの周期でクロック信号を作成します。この期間内でエッジは0 nsになり、3番目に減少します。

クロック信号に関連する別の便利なコマンド:

create_generated_clock -name {name -source reference_pin [-divide_by divide_factor] [-multiply_by multiply_factor] [-invert] source

通常、フェーズロックループ(PLL)スキームでチップ内部で生成されるクロック信号を記述します。 実際、ほとんどの部分の引数は、元の信号のソース、除算および乗算係数、信号の反転など、PLLで指定された設定を繰り返します。 PLLはどこでも使用されるため、これも重要なコマンドであり、一般的です。

実際の制限と設計要件を設定するチームに移りましょう。 コマンドの最初のペア:

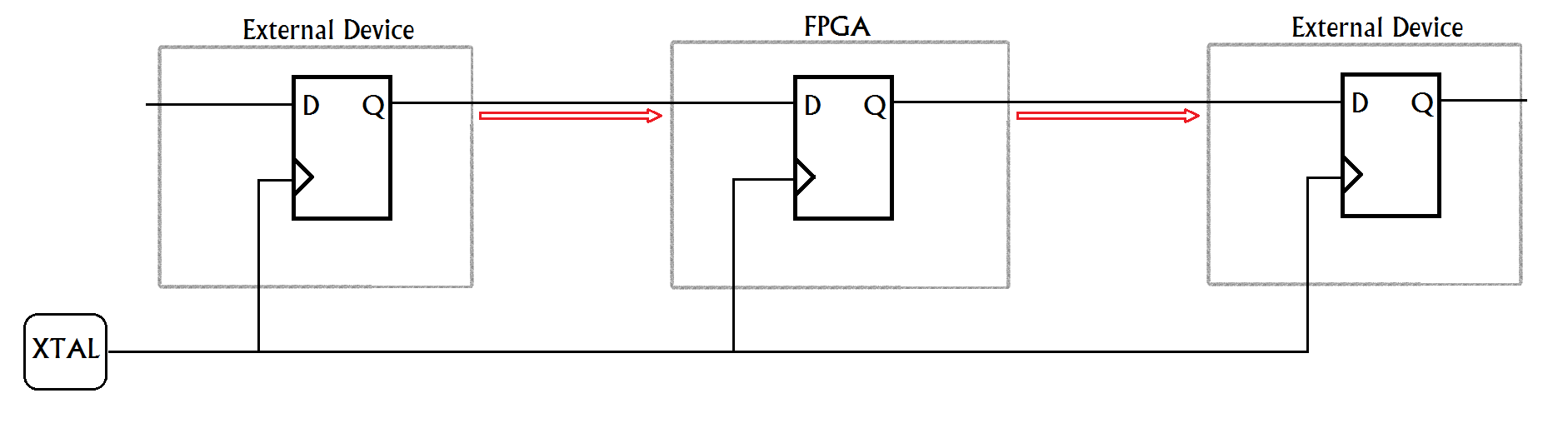

set_input_delay delay_value -clock clock_ref [–max] [–min] [–clock_fall] input_list set_output_delay delay_value -clock clock_ref [–max] [–min] [–clock_fall] output_list

デザインが外部デバイスと相互作用する場合の重要な制限(これは常に当てはまります)。 クロック信号を基準にして、FPGAの外部の信号(入力または出力)の遅延を設定します。 他のデバイスとの相互作用では、これらの両方が機能する時間的特性を考慮する必要があります。 たとえば、FPGA、データを交換するデバイス、クロックジェネレーターがあります。これは、クロックパルスの共通ソースとして機能します。 時間分析と追跡を効果的に行うために、信号がどのように送られてきて、どのようにそれを出すことができるかを知っておくといいでしょう。 通常、このような情報は製品の対応するデータシートに記載されているため、タスクは通常、ドキュメントを表示し、特性を* .sdcファイルにコピーすることになります。

引数については、ここでは簡単です。ナノ秒単位の遅延値、クロック信号は、オプションで遅延が最大か最小かを示し、バインディングが減少していることを示し、最後の1つは適用するポートのリストです。

次のコマンドペアは、それぞれ内部パスの最小遅延と最大遅延を設定します。

set_min_delay delay_value [-from from_list] [-to to_list] set_max_delay delay_value [-from from_list] [-to to_list]

ここでも、引数は単純です-ナノ秒単位の遅延値、開始点、終了点。 通常、このような制限は、チップ入力から出力までの純粋な組み合わせパスに適用されます。 これは、少なくとも1つのエンドポイントが同期エレメントである場合、set_input_delayおよびset_output_delayおよびcreate_clock制約を考慮に入れます。 また、複数のクロックドメインを持つ回路にも使用でき、それらの間の信頼できる遷移を提供します。

パスを決定するのに役立つ2つのコマンドで一時定数の検討を終了します。このコマンドの通過には複数のクロックサイクルと偽のパスが必要です。 ここで、これらのパスが何であるかを伝えるために再び後退する必要があります。

マルチサイクルパスは、エンドポイントがトリガーであり、通過するデータが宛先に到達するまでに複数のクロック周期を必要とするパスです。 このようなパスを特定することは非常に重要です。デフォルトでは、すべての最適化ツールはスキームをシングルサイクルと見なします。つまり、すべてのトリガートリガータイプのパスを1クロックサイクルにしようとします。 たとえば、ソースは、クロック周波数の2倍低い周波数のデータを生成します。 その後、各メジャーでデータをキャッチすることは意味をなさないため、このパスはマルチサイクルとしてマークされ、パスを通過する信号には2つのメジャーを保持する特権が与えられます。 これが行われない場合、ツールはこのパスを最適化しようとしますが、他のツールは1クロックサイクルの経過を必要とするだけです。

Flase path-物理的には存在しますが、そのような経路である偽の経路ですが、たとえば、デバイスの動作中に信号が通過しない場合など、最適化および一時分析のプロセスからそれらを除外する理由があります。 簡単な例:4ビットのカウンターがありますが、カウントする必要があるのは9だけです。そうすると、カウンターは常にリセットされます。 しかし、数値が大きくなると、大幅に遅延するパスが含まれることがわかりました。 それらは存在しますが、実際には必要ありません。 このようなパスはfalseパスとしてマークされているため、最適化と時間分析から除外されます。 マルチサイクルの例のように、すべてをそのままにすると、これらのパスは最適化され、残りのパスの結果がすべて得られます。

上記のパスを飼いならすためのコマンド:

set_multicycle_path ncycles [-from from_list] [–through through_list] [-to to_list] set_false_path [-from from_list] [-through through_list] [-to to_list]

両方のコマンドで、引数はエンドポイントを示し、マルチサイクルの場合、パスの通過のために信号に与えられるティックの数を示します。

そこで、時間制限を設定し、プロジェクトの時間特性の要件を説明できるコマンドのいくつかを調べました。 それらの正しい割り当てと注意深さは、FPGAデバイスの開発の成功の鍵ですが、非現実的な要件が記述されている場合は追跡および除去が困難な重大な困難とエラーを同様に作成する可能性があります。 もちろん、上記は海での低下に過ぎませんが、将来の研究のための最初のアイデアと基礎も提供します。 これらのコマンドとそのキーの詳細については、たとえば[2]を参照してください 。 次に、実用的な部分に移り、Microsemi / Actel FPGAの設計ツールであるLibero SoC環境での時間分析の様子を見てみましょう。

Libero SoC SmartTimeの時間分析

要件を作成し、時間制限を導入します-これはそれほど悪くありません。 この時点で、一時的分析とメガヘルツの闘いの長く複雑なプロセスが始まります。 プロジェクトの複雑さが多少なりとも適切な場合、最初の結果は達成できません。 したがって、要件を修正し、制限ファイルを変更し、プロジェクト自体を変更する必要があります。 たとえば、FPGAを同じものに変更できますが、スピードグレードは大きくなります。 しかし、変更せずに、どのチップがプロジェクトのニーズを満たすかをすぐに理解するために、静的時間分析ツールがあります。

現在、 タイムアナライザー(タイミングアナライザー)はすべての最新のCAD設計機器に含まれています。 開発者は、このプログラムを使用して、FPGAをフラッシュして実物大のサンプルでテストする前に、生まれたばかりの(またはおそらく100回再コンパイルされた)デバイスの能力に彼の願望が対応しているかどうかを知ることができます。 最新のCADシステムでは、便利なグラフィカルインターフェイスがあり、すぐにマスターできます。

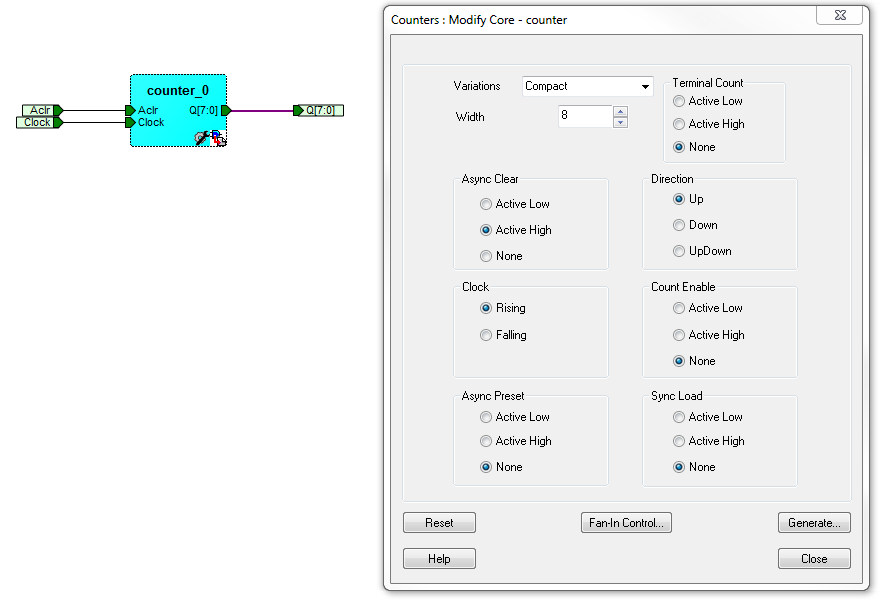

Libero SoC SmartTimeに含まれる例を使用したタイムアナライザーを検討してください。 これを行うには、Libero SoC環境のカウンターを使用して、FPGA用の古典的なhello worldプロジェクトのバリエーションを作成し、その例を使用してタイムアナライザーで許可される内容を把握します。

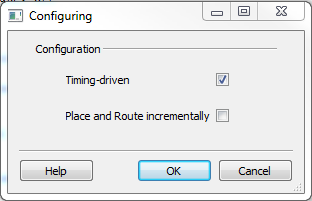

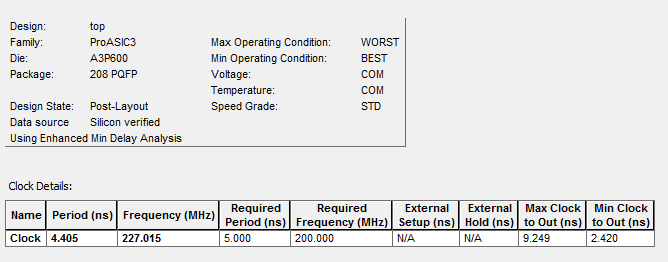

PQ 208パッケージの標準スピードグレードのシンプルな第3世代Microsemi FPGAチップであるProASIC3 A3P600がプロジェクトで選択されました。 同時に、配置配線設定で、時間特性の最適化基準を選択する必要があります(タイミング駆動型)。

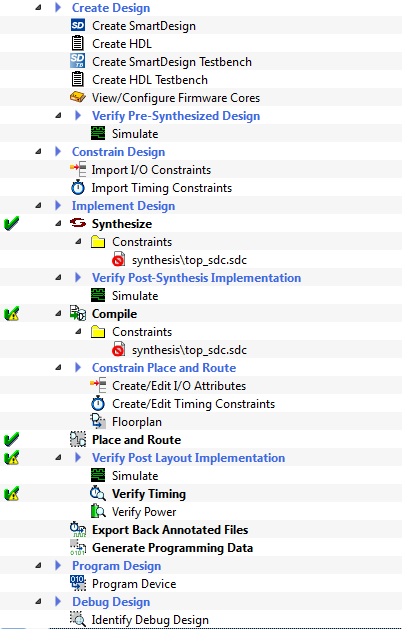

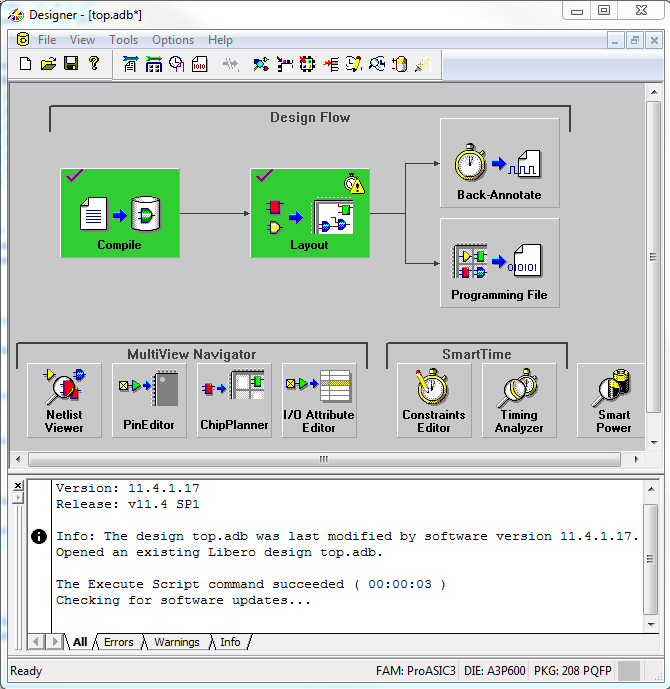

その後、Designerツールにアクセスできるようになります。Designerツールには、時間制限と時間分析を管理するためのシェルSmartTimeが含まれています。 Constraints EditorとTiming Analyzerの2つのサブシステムで表されます。

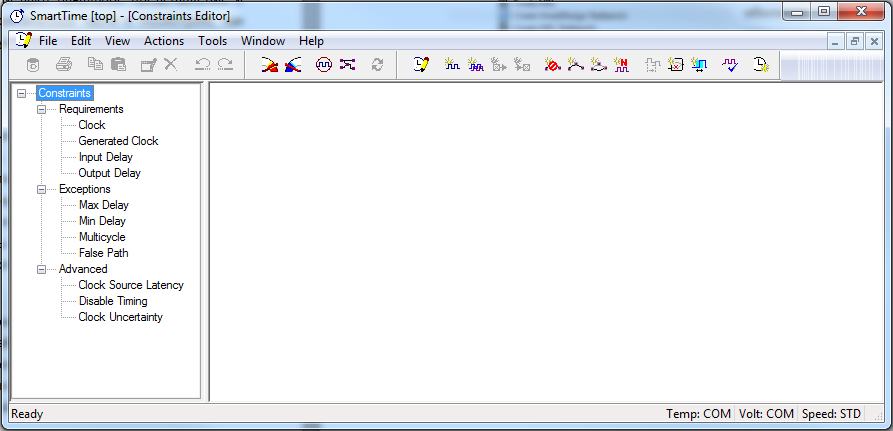

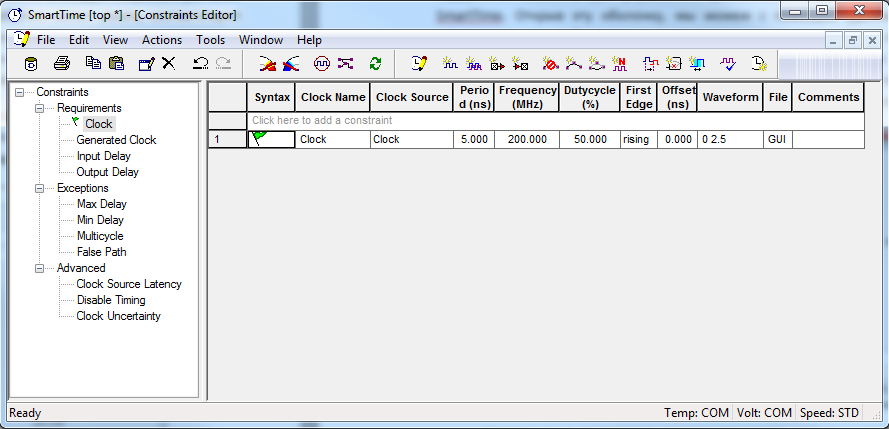

Constraints Editorを開くと、便利なグラフィカルインターフェイスを使用して、上記の要件と制限を設定し、* .sdcファイルをエクスポートできます。 やってみましょう。 上で示したように、最初の、そして確かに必要な定数は、必要な特性を持つクロック信号の作成です。 そのようなものは1つしかありません。それを説明するには、[アクション]-> [制約]-> [時計]のメニューに従ってください。

信号の発信元のピンを示し、プロジェクトが200 MHzで動作する必要があると想像します。 [OK]をクリックすると、エディターでシュレッドがどのように表示されるかがわかります。

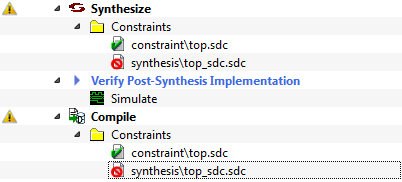

変更を有効にするには、[ファイル]-> [コミット]をクリックし、Designerウィンドウから[ファイル]-> [エクスポート]-> [制約ファイル]で制限ファイルをエクスポートします。 デフォルトでは、プロジェクトのルートにある制約フォルダーに配置されます。 デザインフローに戻って、表示されたtop.sdcファイルをSynthesizeおよびCompileサブパラグラフで使用されているものとしてマークし、開きます。

################################################################################ # SDC WRITER VERSION "3.1"; # DESIGN "top"; # Timing constraints scenario: "Primary"; # DATE "Mon Feb 16 10:48:26 2015"; # VENDOR "Actel"; # PROGRAM "Microsemi Libero Software Release v11.4 SP1"; # VERSION "11.4.1.17" Copyright (C) 1989-2014 Actel Corp. ################################################################################ set sdc_version 1.7 ######## Clock Constraints ######## create_clock -name { Clock } -period 5.000 -waveform { 0.000 2.500 } { Clock } ######## Generated Clock Constraints ######## ######## Clock Source Latency Constraints ######### ######## Input Delay Constraints ######## ######## Output Delay Constraints ######## ######## Delay Constraints ######## ######## Delay Constraints ######## ######## Multicycle Constraints ######## ######## False Path Constraints ######## ######## Output load Constraints ######## ######## Disable Timing Constraints ######### ######## Clock Uncertainty Constraints #########

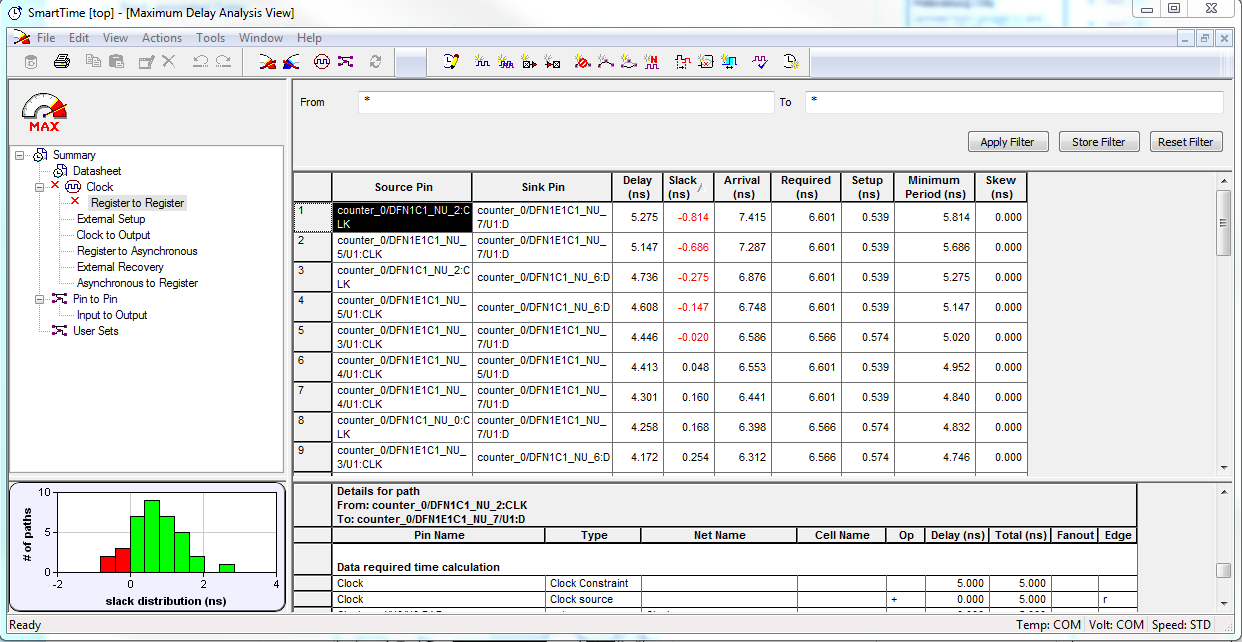

create_clockが存在する特別にフォーマットされたファイルがあり、残りのフィールドは空です(設定されている場合、対応するコマンドがある場合があります)。 さて、デザインフローを再度実行して、タイミングを確認します。 Designerを再度開き、2番目のサブシステム-Timing Analyzerを起動します。 デフォルトでは、最大遅延分析ビューが開きます。つまり、最悪の場合の条件に基づいて計算された時間遅延です。 結果を見てみましょう。

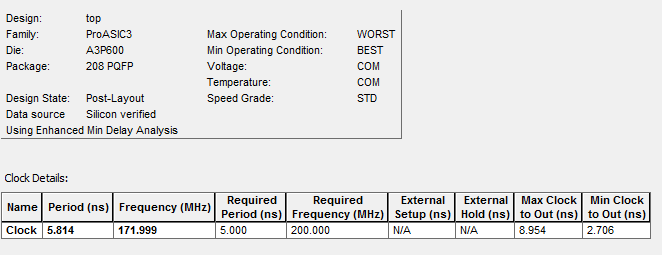

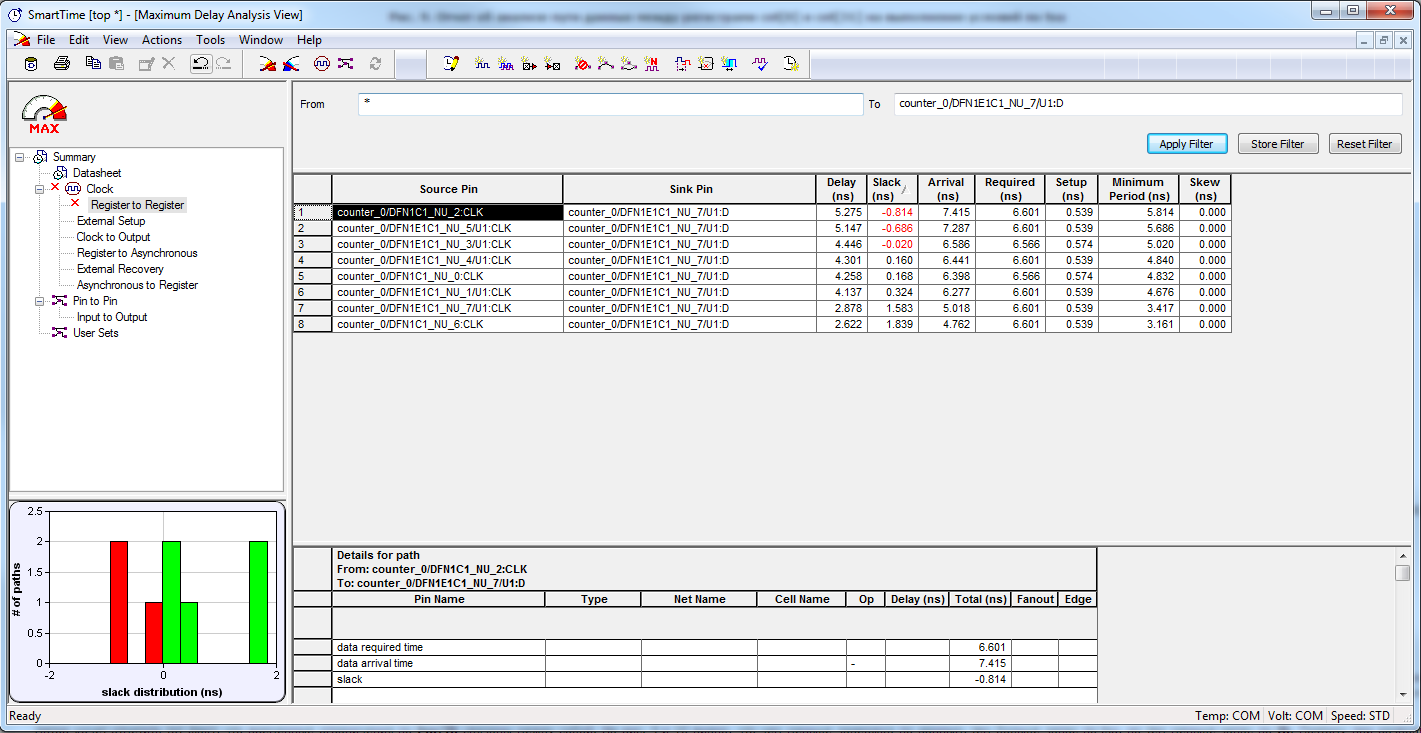

多くの人が長い間反射神経を発達させてきました:赤い色は悪いです。 例外はありますが、この場合は例外です。 Register-to-Registerサブ項目に進みましょう。このサブ項目には、表形式で作成された単一のクロックドメインのトリガー間のパスに関する情報が含まれています。 そのような方法でいくつかの悪い結果があり、負のスラックが現れ、トリガー受信機への信号到着時間が計算された最大許容値よりも長くなります。 これが何を脅かすかは、投稿の冒頭の理論部分で説明されています。 幸いなことに、ここですべてがそれほど悪くはありません-否定的な結果を示したパスは5つだけです。 Slack分布は、ウィンドウの左下のヒストグラムに表示されます。 始めましょう。 まず、設定した条件を思い出して、アナライザーが言ったことを確認します。

わくわくし、このプロジェクトでは200 MHzが172 MHz f maxに下げられました。 次に、悪い方法の1つを詳しく見てみましょう。これをダブルクリックします。

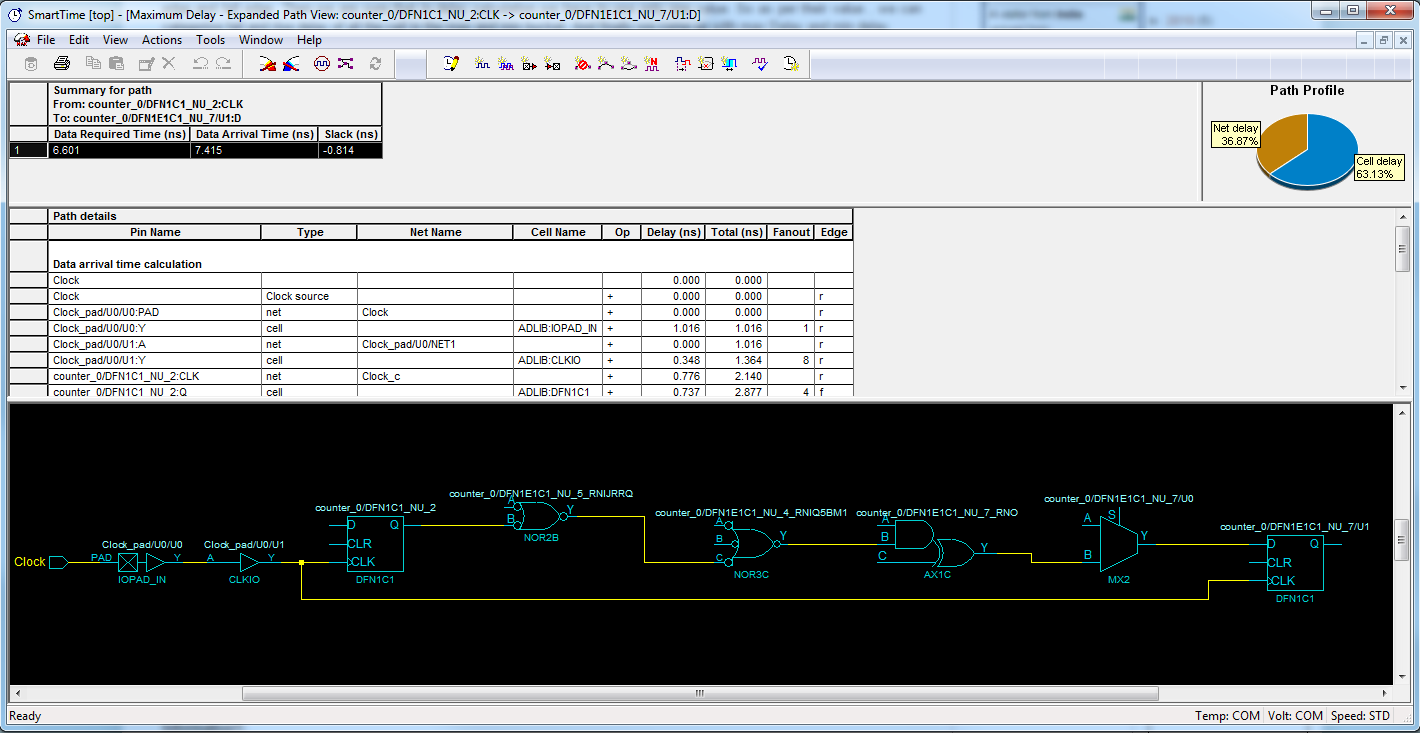

詳細なパス情報が開きます。 メロンの到着に必要な時間(データ必要時間)、データが実際に到着する時間(データ到着時間)、および時間の余裕(スラック)に関する情報が表示されます。 同時に、信号がどこでどの程度遅延するかを詳細に示す表の形式で、およびソーストリガーとレシーバートリガー間の接続のイメージの形式で、パスが開かれます。 このツールは、必要なデータの計算方法も示します。 右上隅には、バルブの遅延と接続ラインの遅延の比率を示す円グラフも表示されます。

結果を分析すると、カウンターの2番目のカテゴリーのトリガーから7番目のカテゴリーのトリガーへの途中の組み合わせチェーンのゲートの遅延は、回路全体が指定された周波数で動作することを許可しないと結論付けます。 組み合わせパスが長すぎて複雑であり、データが適切なタイミングで到着する時間がありません。Slackには負の値があります。 この状況は明らかな理由で上位の数字で発生します-1に落ち着くために、7番目の数字は他のすべてが既にインストールされていることを確認する必要があり、それに応じて8つのパスがあります(フィードバックを含むすべての数字から)。それらのいくつかは受け入れられないでしょう。

したがって、わずかなパスのために、デザインは適切な周波数で機能しません。 それは残念です。 これに対処する方法は? 同期回路のパフォーマンスを向上させる最も一般的な方法は、プロセスをステージに分割することによってトリガー間の大量の組み合わせロジックを排除することです。これはパイプライン処理と呼ばれます。 一般的な場合、このアプローチでは、入力データストリームは通常どおりに到着し、パイプラインのいくつかのステージを通過し、パイプラインの深さに応じてしばらくして出力に表示されます。 深さ、つまりステップ数は、パフォーマンス要件に基づいて選択されます。

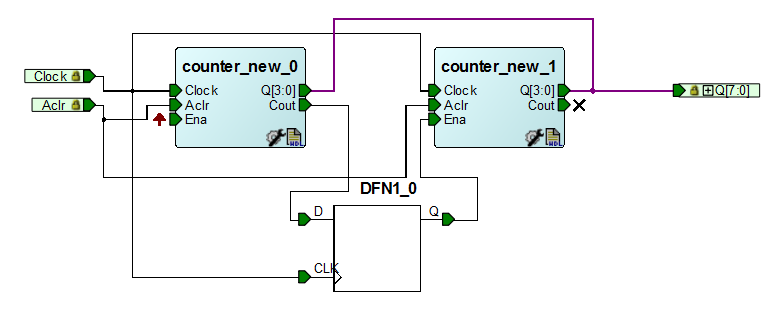

プロジェクトに戻り、設定された目標を達成するためにこのアプローチを適用してみましょう。 1つの8ビットタイマーを2つの4ビットタイマーに分割し、転送出力とクロックイネーブル入力を追加します。 Dトリガーを介して、最初のタイマーの転送出力を2番目のタイマーのクロックイネーブル入力に接続します。 2段階のコンベアを取得します。最初のタイマーは最下位ビットを表し、2番目のタイマーは上位ビットを表します。

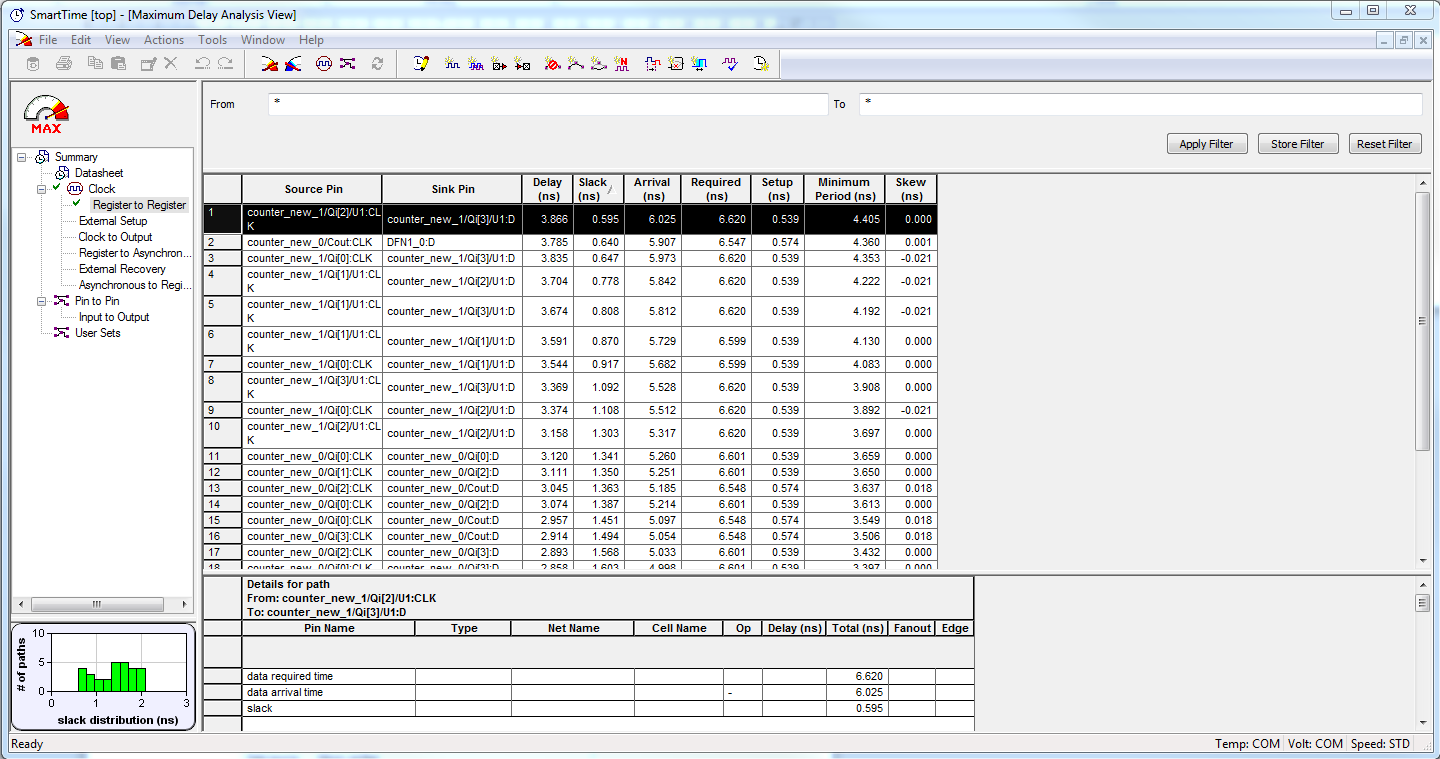

コンパイルを開始してSmartTimeに進みます。 出来上がり。 負のSlackはなくなり、エラーはなくなり、周波数は227 MHzに上昇しました。これは必要以上に大きい値です。

そのため、パイプライン技術を適用して、172 MHzから227 MHzのカウンターでプロジェクトの周波数をオーバークロックしましたが、使用されている水晶のように機能は完全に保持されていました。

おわりに

もちろん、非常に単純なケースを検討しましたが、これは実際のプロジェクトや実際の最適化プロセスとはまったく異なり、一時的なアナライザーのウィンドウで頭が赤くなり始め、プロジェクトのデバッグに数日かかります。 例がもう少し複雑になると、多数の新しい質問が表示されます。 マルチサイクルパスとフォールスパスを効果的にキャッチする方法は? 複数のクロックドメインをどうするか どういうわけか、いくつかの要素の配線を修正し、それらの時間的特性を修正できますか?

しかし、これは初心者がこの難しいタスクをマスターするための良い出発点です。 そして、もちろん、自分の手で同じことをして、より複雑なプロジェクトを最適化することを試みる価値があります。

参照:

1. www.microsemi.com 、 actel.ru-マニュアルを含むMicrosemiの公式ウェブサイト、公式ディストリビューターのウェブサイト(ロシア語の情報)

2. www.microsemi.com/index.php?option=com_docman&task=doc_download&gid=131597-制約について。

3. www.vlsi-expert.com/p/static-timing-analysis.html-静的時間分析について。

4. vhdlguru.blogspot.ru/2011/01/what-is-pipelining-explanation-with.html-パイプライン処理について。

5. www.microsemi.com/index.php?option=com_docman&task=doc_download&gid=130940-SmartTimeガイド。