FPGAを10年以上使用していたとき、たまたま4つの異なるメーカーの製品を使用していました。 このような多様性により、開発プロセスの一般的な機能と特定の企業に固有の機能の両方に思わず注意を向けることになります。 そして今、数ヶ月前、私は突然、カリフォルニアの小さな野心的な会社によって生産された新しいFPGAファミリーを知るユニークな機会を得ました。 私は最年少のFPGAメーカーであるAkroniks(Achronix)とそのFPGA Speedster22i HD1000について話しています。

創業(2004年)以来、この若い会社は、独自のアーキテクチャと独自の機能を備えたHI-End FPGAを開発することができました。 さらに、同社はすべてのFPGAメーカーの中でインテルコーポレーションと戦略的提携を結んだ最初の企業であり、それ以来、インテルの最先端の技術拠点で独自のマイクロ回路(図からわかるようにサイズが「マイクロ」をはるかに超えています)を製造していますアメリカに直接。 現在、Speedsterシリーズは3D Tri-Gate 22nmテクノロジーで利用できます。 近い将来、シリーズ開発プログラムは14nmおよび10nmの技術プロセスへの移行を提供します(Intelの工場で習得されるため)。

このレビュー記事では、一方で、Speedster FPGAで動作するために使用される製品を簡単に説明し、他方で、非常にシンプルだが実際に完成したプロジェクトの例を使用して、これらの製品での私の経験(感情を含む)について説明します。 だから...

鉄と開発ツール

おそらく、今日の仕事でSpeedster22i FPGAに慣れる唯一の方法は、Speedster22i HD1000開発キットデバッグキットを購入することです(ギフト、レンタル、リースとして受け取る)。 配達を待つ過程で準備作業が行われました。水冷、32GB RAM、2台のモニターを備えた強力なコンピューターが購入されました。 開発ツールを入手するには、Achronix Webサイト(http://www.achronix.com/company/contact-us.html)に登録し、ユーザーアカウントを取得する必要がありました。 ユーザーアカウントにより、作業に必要なソフトウェア、デモおよびリンクデザインが含まれるサイトエリアへのアクセスが許可されます。 それらの違いは何ですか? リファレンスデザインにはFPGAのソースコードが付属していますが、通常、デモデザインにはFPGAのブートファイルしか含まれていません。

登録の確認には数日かかり、ユーザー名とパスワードを含む手紙を受け取って終了しました。 その後、必要なツールをダウンロードすることが可能になりました-ACEと呼ばれるAchronix独自のシェルとSynplifyシンセサイザー。 ただし、これらのプログラムが機能するためには、ライセンスファイルも必要です。 これを行うには、別のフォームに記入し、ネットワークカードのMACアドレスを指定します。 ライセンスファイルは電子メールで送信されます。 それらの接続も問題を引き起こしませんでした。さらに、このプロセスの詳細はドキュメントに記載されています。 コンピューターにWindowsがインストールされていますが、Red Hat Linux用の開発ツールも利用できます。

ボードが到着するまでの残りの時間は、FPGA Speedster22i HD1000のアーキテクチャの研究、設計ツールの習得、および単純な設計の作成に費やされました。

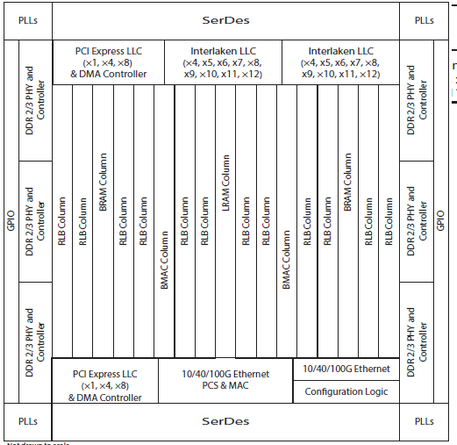

Speedster22iシリーズの何がおもしろいですか? 他社製品との違いは何ですか? FPGA Speedster22iには独自の「ハイライト」があります-高速通信タスクに焦点を当てたハードウェアIPコア。 Achronix FPGAコアはまだ競合状態にありません。 コアの命名法:DDR-3-6個、PCI Express Gen1 / 2/3 x1、x4、x8-2個、最大100GのイーサネットMAC-2個、Interlaken-2個。合計スループットは400以上Gb / s。もちろん、Speedster22iシリーズのFPGAをHI-ENDとして分類できます。

それ以外の場合、構造で検討中のFPGAは、他のメーカーの製品と大差ありません:論理クラスター(4入力LUTに基づく)、ブロックメモリ、分散メモリ、および強力な56ビット乗算器を含む算術ブロックで構成されています。 これらはすべて、最も複雑な機能を実現するのに十分な量で利用できます。 速度特性も印象的です。たとえば、メモリの最大動作周波数は750 MHzです。 Speedster22iシリーズのFPGAの主な特徴を以下の表に示します。

| パラメータ | HD680 | HD1000 | HD1500 |

| ハードウェアコントローラーを含むロジックスコープ(有効なLUTセル) | 660,000 | 1045000 | 1725000 |

| プログラマブルロジックボリューム(LUT) | 400,000 | 700,000 | 1,100,000 |

| BRAMモジュールの数 | 600 | 1026 | 1728 |

| LRAMモジュールの数 | 4320 | 6156 | 10368 |

| 80キロビットBRAMのボリューム(合計Kビット) | 48000 | 82080 | 138240 |

| 640ビットLRAM容量(合計Kbps) | 2765 | 3940 | 6636 |

| 乗算器(28×28) | 240 | 756 | 864 |

| 回線数SerDes 12.75 GB / s(ギガビット/ s) | 40 | 64 | 48 |

| 行数SerDes 28 gb / s(ギガビット/ s) | - | - | 16 |

| イーサネットハードウェアコントローラー(MACレイヤー)10/40/100ギガビット/秒 | 2 | 2 | 4 |

| Interlaken LLCコントローラー | 1 | 2 | 4 |

| PCI Express LLCコントローラー | 1 | 2 | 2 |

| DDR2 / DDR3コントローラー | 4 | 6 | 6 |

| PLL番号 | 16 | 16 | 16 |

| ピン数、ケースFBGA2601 52.5×52.5(12G、28G、GPIO) | - | 64,0,960 | 48.16.960 |

| ピン数、ケースFBGA1936 45×45(12G、28G、GPIO) | 40,0,684 | 40,0,684 | 20,4,684 |

| ピン数、ケースFBGA1520 40×40(12G、28G、GPIO) | 18,0,684 | - | - |

最低限必要な開発ツールのセットには、ACEシェルとSynplifyシンセサイザーの2つのプログラムが含まれています。 自社開発-ACEシェルには、配置および配線、コアの構成、ロードおよびデバッグのための機能が含まれています。 シンセサイザーとして、SynopsysのSynplifyプログラムが使用されます。 単一の統合環境ではなく、一連の個別のプログラムを使用するアプローチは、中小企業に一般的です。 初心者の開発者にとってはあまり便利ではありませんが、経験豊富なエンジニアにとっては、各ステージの実行の柔軟性と品質が向上します。 より深い統合が必要な場合、たとえば、MentorGraphicsのHDLデザイナーシェルを使用して、必要なすべてのソフトウェアツールを組み合わせることができます。

指定されたプログラムにシミュレータプログラムを追加することをお勧めします。 Achronixパッケージには、最も一般的なシミュレーションプログラム用のライブラリが含まれていますが、これらのプログラム自体はパッケージに含まれておらず、個別に購入されます。

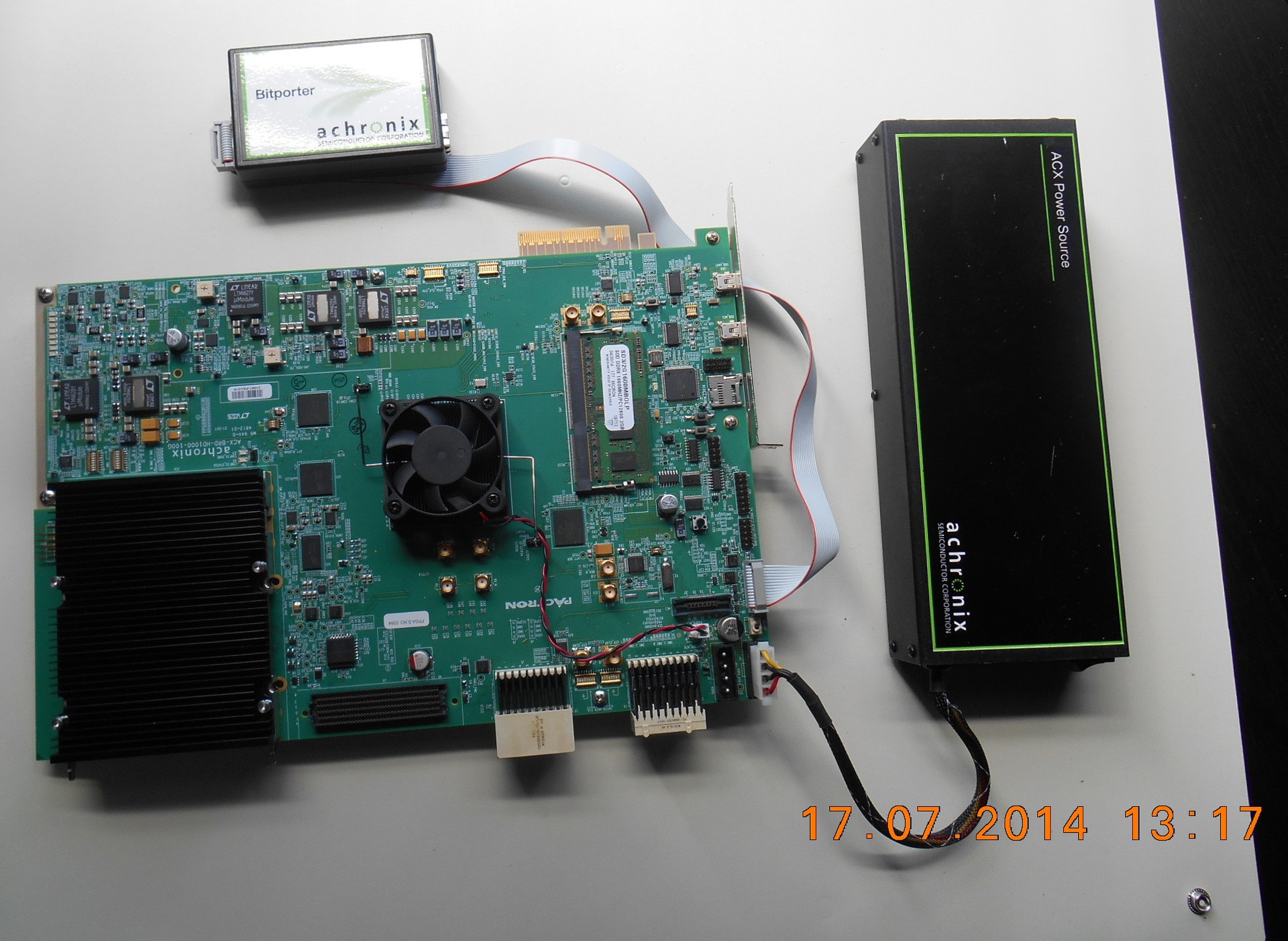

そして最後に、待望の支払いが私たちのオフィスに到着しました!

興奮して手が震えます(そして、ボードの価格が安価な輸入クロスオーバーの価格のようになったら心配しないでください!)、ボードを開梱し、その「通常の」場所に移しました-私のデスクトップの帯電防止ラグに、興味を持って調べました。

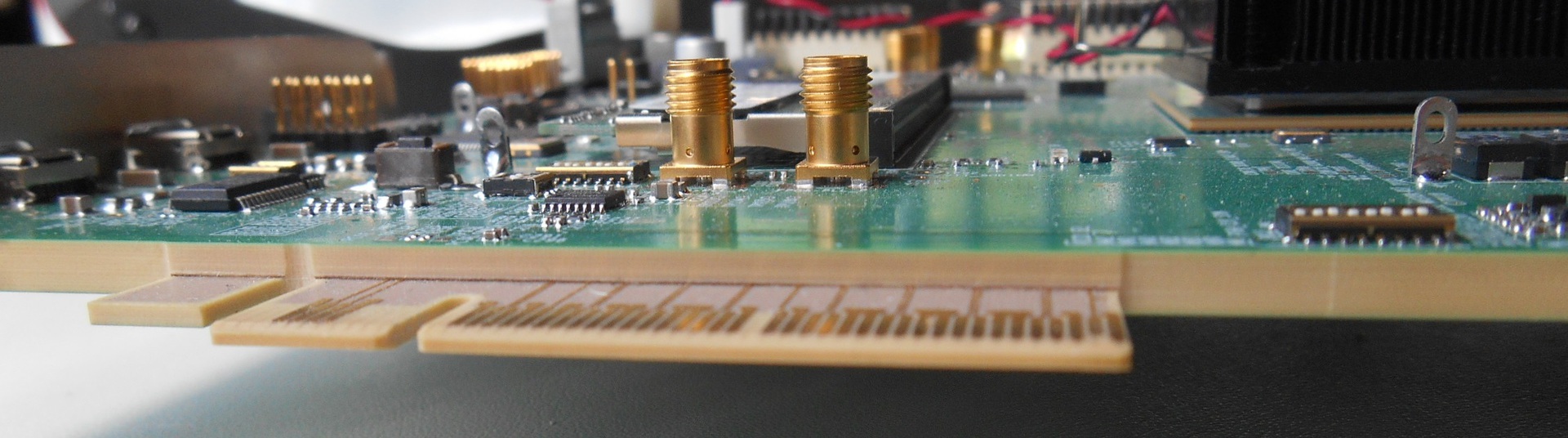

ご覧のとおり、ボード自体は複雑で多機能な製品です。 電気回路だけでも90ページかかります! したがって、ボードが開発とデバッグを可能にすることは驚くことではありません。たとえば、CFPモジュール用のコネクタがあるイーサネット100Gネットワーク用の機器を作成するためのユニークなプロジェクトという言葉を恐れていません(上の写真の左下隅にある「黒い四角」) 2つのInterlakenインターフェイスがAirMaxコネクタにルーティングされます。

プリント回路基板の厚さに最も感銘を受けました。 いくつのレイヤーがありますか? 20? 30? 40? 問題は未解決のままでした。

ボードにはPCIエクスプレスコネクタ(Gen 3 x8、64 Gb / s)があり、コンピューターの一部として周辺機器として動作できます。 合わせて、次のようになります。

パッケージには、ローダーおよびデバッガーとして機能するJTAGケーブルが含まれています。 このケーブルの機能は、USBポートまたはイーサネット経由で機能することです。 後者の場合、デバイスへのリモートアクセスを整理できます。 イーサネット経由で作業する場合、外部電源が必要です(付属)。 パッケージには、ボード自体の強力な電源と2GBのDGB-3 RAMモジュールも含まれています。

ヘルスチェック

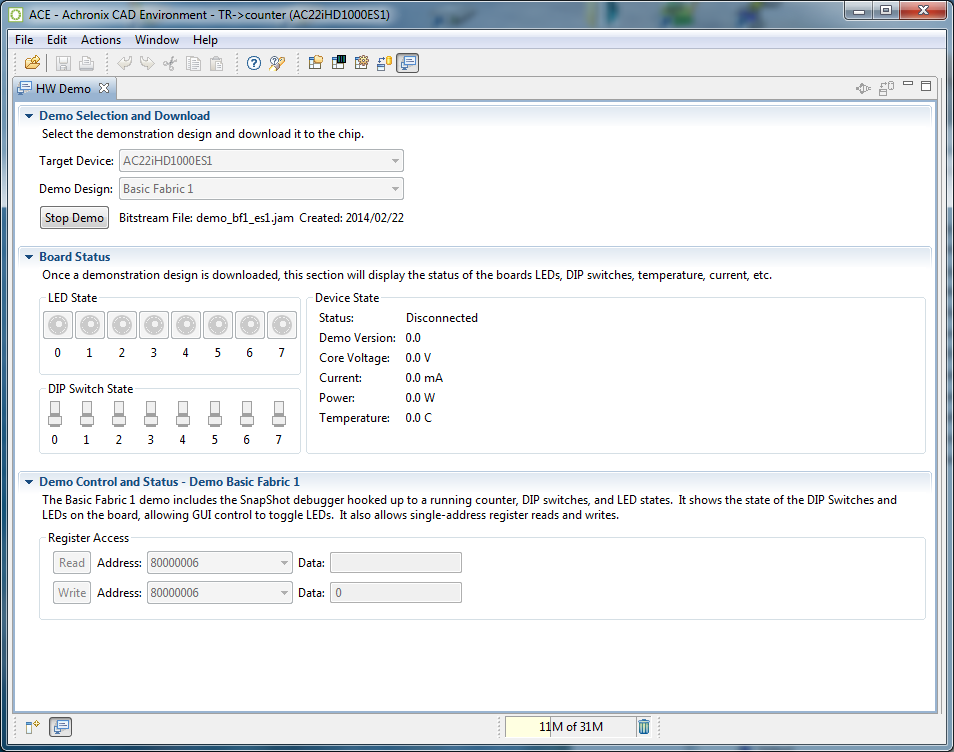

ボードが機能していることを確認するのは非常に簡単であることが判明しました。 テストはすでにACEシェルに組み込まれています。 そのため、実際には、チェック全体が1つのボタンを押してテストファームウェアをダウンロードすることになります。 その後、スイッチを操作してLEDをオン/オフし、内部メモリブロックをテストできます。 ボードはUSBケーブルでコンピューターに接続する必要があります。

開発

そして今-Achronix FPGAの最初のプロジェクトをどのように行ったかについて。 そのため、最も単純なオプションが選択されました-LEDへの高位ビットの出力を備えたカウンター。 もちろん、このような単純なプロジェクトは専門家を感心させるものではありませんが、FPGA Achronixを使用して設計ルートを習得するために使用される開発ツールの基本機能を学習できます。 今後の出版物では、ハードウェアコアの構成と使用、ARMプロセッサコアを使用したチップ上でのシステムの実装など、より複雑なことについて話す予定です。

プロジェクト構造

少なくとも3つのサブディレクトリを含む個別のディレクトリに配置する各プロジェクト:

- Src-ソース用

- Syn-合成用

- TR-実装用

シンセサイザはそこに置かれたファイルをワイプできるため、Synディレクトリに余分なものを残さない方が良いことが実践的に示されています。 したがって、ソーステキスト(Verilogで作業することを好む)をSrcディレクトリに保存し、すべてのスクリプトをTRディレクトリに保存します。

ソースコード

モジュールのソースコードは完全に簡単です。

module counter #( parameter CNT_WIDTH = 32 ) // 8 <= CNT_WIDTH ( input wire clk, input wire rstn, output wire [7:0] leds ); wire rst; reg [CNT_WIDTH-1:0] cnt; assign rst = ~rstn; always @(posedge clk or posedge rst) if (rst) cnt <= 'h0; else cnt <= cnt+1; assign leds[7:0] = cnt[CNT_WIDTH-1: CNT_WIDTH-8]; endmodule

ただし、デモボードに実装するには、少し変更する必要があります。

まず、クロックソースを選択して適切に接続する必要があります。 ボードにはそれらのいくつかがあります。 調査後、差動出力を持つ100 MHzの周波数のソースが選択されました。 そのため、入力クロック回路に差動バッファを追加する必要がありました。

第二に、プロセスの内部信号を見たいです。 すべてのFPGAメーカーにはこのような機会があり、Achronix FPGAでも利用できます。 内部信号アナライザーはSnapShotと呼ばれます。 競合他社とは異なり、SnapShotコンポーネントは設計で明示的に記述する必要があります。 これは最初は不便でしたが、このアプローチの利点を理解しました。 この利点は、あなたがしていることを完全に制御することにあります。 さらに、このアプローチにより、監視対象イベントを記録するためのトリガーを非常に柔軟に構成できます。

そのため、最終バージョンでは、差動クロック入力とそのバッファ、および内部信号を調べるためのShapShotコンポーネントがあります。 最終Verilogテキスト:

`define USE_SNAPSHOT module counter #( parameter CNT_WIDTH = 30 ) // 8 <= CNT_WIDTH <= MNTR_WIDTH ( `ifdef USE_SNAPSHOT input wire tck, input wire trstn, input wire tms, input wire tdi, output wire tdo, `endif input wire clk_p, input wire clk_n, input wire rstn, output wire [7:0] leds ); //********************************************** wire clk; wire rst; reg [CNT_WIDTH-1:0] cnt; assign rst = ~rstn; IPAD_DIFF #( .odt("on"), .termination("100") ) synth_clk_pad ( .pad(clk_p), .padn(clk_n), .dout(clk) ); always @(posedge clk or posedge rst) if (rst) cnt <= 'h0; else cnt <= cnt+1; assign leds[7:0] = cnt[CNT_WIDTH-1: CNT_WIDTH-8]; //********************************************* `ifdef USE_SNAPSHOT localparam MNTR_WIDTH = 36; wire [MNTR_WIDTH: 0] ss_zeroes; ///// Signals going to trigger-detector block to do pattern matching wire ss_clk; wire [MNTR_WIDTH-1 :0] ss_monitor_ch; /// Signals monitored in Snapshot wire [MNTR_WIDTH-1: 0] ss_trigger_ch; ///// Signals going to trigger-detector block to do pattern matching wire ss_rstn_out; ///// Active low user reset signal. wire ss_Arm; ///// Indicates Snapshot activity. wire [MNTR_WIDTH-1:0] ss_Stimuli; ///// User specified values for 3rd trigger pattern value assign ss_clk = clk; assign ss_zeroes = {MNTR_WIDTH+1{1'b0}}; //// //////// Now Snapshot macro block instantiation /////// ACX_SNAPSHOT #(.MNTR_WIDTH(MNTR_WIDTH) ) snapshot_0 ( .tck ( tck ), .tms ( tms ), .trstn ( trstn ), .tdi ( tdi ), .tdo ( tdo ), .usr_clk ( ss_clk ), .Monitor_ch ( ss_monitor_ch ), .trigger_ch ( ss_trigger_ch ), .Rstn_out ( ss_rstn_out ), .Arm ( ss_Arm ), .Stimuli ( ss_Stimuli ) ); assign ss_monitor_ch = { ss_zeroes[MNTR_WIDTH-1: CNT_WIDTH], cnt[CNT_WIDTH-1:0] }; assign ss_trigger_ch = ss_monitor_ch; `endif //********************************************** endmodule

合成

Synplifyシンセサイザーを機能させるには、ソーステキストとエレメントライブラリへのリンクに加えて、定数ファイル(通常は拡張子.sdcが必要)が必要です。 このような単純な設計には必要ありませんが、指定することをお勧めします。 このような単純なケースでは、クロック信号とそのパラメーターの名前を指定するだけです。

# synplify_constraints.sdc set_hierarchy_separator {/} create_clock clk_p -period 10 create_clock tck -period 40 set_clock_groups -asynchronous -group { tck } -group { clk_p }

次に、Synplifyのプロジェクトを作成し、合成に必要なファイルとライブラリを指定して、プロセスを開始します。 すべてが正しく行われると、拡張子が.vmaの出力ファイルが取得されます。 (FPGA設計の「達人」は、Synplifyのメイン出力フォーマットがedifであることを示している場合があります。ただし、ACEは、.vma拡張子を持つVerilogネットリストのみを受け入れます)。

実装

実際に、実装プロセスは標準スキームに従って実行されます。

- ACE用のプロジェクトの作成

- プロジェクトの合成結果ファイルを指定します(拡張子は.vma)

- 制約を定義する

- 実装プロセスを開始します

- FPGAにアップロードするファイルを取得します

実装するには、2つの定数ファイルを準備する必要があります。ブロックの定義とピンの指定です。 それらの内容を表に示します。

# Ace_constraints.pdc create_clock clk_p -period 10 create_clock tck -period 40 set_clock_groups -asynchronous -group { tck } -group { clk_p } # io_preplacement.pdc set_placement -batch -fixed {p:clk_p} {b:P19} set_placement -batch -fixed {p:clk_n} {b:P18} set_placement -batch -fixed {p:rstn} {b:P17} set_placement -batch -fixed {p:leds[0]} {b:AE47} set_placement -batch -fixed {p:leds[1]} {b:AJ46} set_placement -batch -fixed {p:leds[2]} {b:AC46} set_placement -batch -fixed {p:leds[3]} {b:AF47} set_placement -batch -fixed {p:leds[4]} {b:AF46} set_placement -batch -fixed {p:leds[5]} {b:AJ47} set_placement -batch -fixed {p:leds[6]} {b:AG46} set_placement -batch -fixed {p:leds[7]} {b:AE46}

コンピューターでの実装フェーズは次のとおりです。

設計の読み込みとデバッグ

前の手順で作成したファームウェアファイルをダウンロードするには、[ダウンロード]ウィンドウに移動し、[プログラムの実行]ボタンをクリックして、数分待ちます。

ダウンロードが完了すると、FPGAはすぐに動作を開始し、ボード上のLEDが点滅する楽しい行を観察できます。

SnapShotモジュールに接続された内部信号を表示するには、「スナップショットデバッガー」ウィンドウを開く必要があります。 このウィンドウでは、キャプチャトリガーモードおよびその他のパラメーターを構成できます。 分析は「Arm」ボタンで開始され、その後トリガー状態の追跡が開始されます。 トリガーを設定すると、登録された信号の一時的な図が画面に表示されます(わずかな遅延があります)。

結論と結論

短時間で、AchronixはHI-ENDセグメントの興味深い競争力のあるFPGAとその開発ツールを作成することができました。 彼らと働く技術は、平均的な資格の専門家でさえ問題を引き起こしません。 Achronix製品はすでにロシアで入手可能です。

参照資料

- ロシア駐在員事務所のウェブサイト(「ハイスループット VLSI研究所」)、URL: www.achronix.ru

- ウィキペディア、Acronix企業の記事、URL: en.wikipedia.org/wiki/Achronix

- Speedster22i HDファミリ、データシート、URL: www.achronix.com/wp-content/uploads/docs/Speedster22iHD_FPGA_Family_DS004.pdf

- 開発者キットユーザーガイド:Speedster22i HD1000開発キットユーザーガイド、URL: www.achronix.com/wp-content/uploads/docs/Speedster22i_DevelopmentKit_User_Guide_UG034.pdf

- SnapShot Debuggerユーザーガイド: www.achronix.com/wp-content/uploads/docs/Speedster22i_Snapshot_User_Guide_UG016.pdf

- デバッグボードの電気回路図:22iHD1000_Development_Board_Schematic.pdf

- Achronix社のWebサイト(英語)、URL: www.acronix.com