はじめに

1985年、電子機器メーカーのグループ-JTAG(Joint Test Action Group)が設立されました。 テストの問題を解決するために、1990年に業界標準であるIEEE Std 1149.1-1990仕様(IEEE標準テストアクセスポートおよびバウンダリスキャンアーキテクチャ)が提案されました。 同じ年に、IntelはJTAG-80486を搭載した最初のプロセッサを発表しました。それ以来、標準は絶えず更新されており、現時点では2013年から最新バージョンがリリースされています。

「そして、テストでこれらの問題は何ですか?」、あなたは尋ねます。 じゃあ! オシロスコープを使用して超小型回路の出力にジャンプするのは、特に3つ以上ある場合はそれほど楽しくありません! この規格により、4線式シリアルインターフェイスを使用してピン(より正確には、特別なI / Oブロック)へのアクセスを提供する最新のチップに特別なアーキテクチャを組み込むことにより、生活を大幅に簡素化できます。 このアーキテクチャにより、状態を制御できるだけでなく、管理することもできます。 したがって、物理的な接触を伴うかさばるプローブを使用せずに、回路基板レベルでデジタル超小型回路またはデバイスをデバッグする段階の魅力をすべて享受できます。

この規格は、インサーキットプログラミングとデバッグプログラムの両方、およびパッケージ化された回路での作業に使用されます。 また、ボードへの超小型回路のはんだ付けの品質、ボードとブロックのボード間およびラック取り付けのチェックにも使用されます。 また、不注意にモバイルデバイスを復元してくれた彼にも感謝する必要があります。

そして、それはどのように機能しますか?

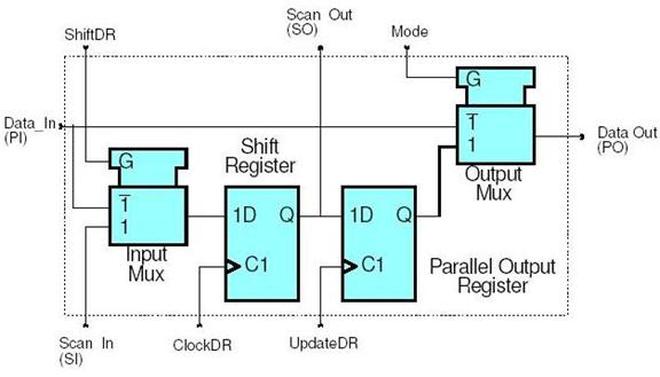

バウンダリスキャンメカニズムは、マイクロ回路の端子とコアの間に接続されたシフトレジスタ(バウンダリスキャン)と、このレジスタを適切なタイミングで接続するマルチプレクサにのみ囲まれています。 それぞれの特定の結論は、いわゆる「セル」に対応しています。

セルには、バウンダリスキャンレジスタとデータ選択マルチプレクサの1つのトリガーが含まれます。 セルは、マイクロサーキットおよびインターフェイスコマンドの出力に応じて、異なるタイプにすることができます。 特定のチップのメーカーによって異なります。 製造業者は規格に厳密に準拠していないため、多くの変更が離婚しています。

図は、セルの種類の1つを示しています。 PI、PO-パラレル入力および出力、SI、SO-シリアル。

信号はマルチプレクサを介してマイクロサーキットレジスタに送られ、マイクロサーキットピンの状態(INTEST命令)と外部からシフトレジスタに送られるデータ(EXTEST命令)の両方を読み取ることができます。 さまざまな指示とその機能は、メーカーの要望から再び変わりますが、いわゆる必須があります:

- EXTESTは、電子コンポーネントの動作接点に論理値を設定することにより、テスト対象コンポーネントに直接関連する外部回路をチェックできるようにする命令です。

- INTEST-命令は、チップ内、つまりカーネルの入力で論理値を設定し、それによってそれをチェックする機能を提供します。

- SAMPLE_PRELOAD-静的モードで電子要素のコアをテストし、出力バッファーの境界で論理レベルの値を設定できます。

- BYPASS-バウンダリスキャンレジスタが1つのトリガーに「崩壊」する命令。 同時に、入力(TDI)から出力(TDO)へのデータは、インターフェイスクロック周波数(TCK)の1クロックサイクルの遅延で送信されます。 このモードを使用すると、連続して長く結合されたチェーンを整理するときに、シリアルインターフェイスの機能を効果的に使用できます。

- IDCODE-命令は、デバイスのメーカー、モデル、およびバージョンの識別子とともに、組み込みの32ビットレジスタの値を出力します。

インターフェイス信号線

前述のように、JTAGインターフェイスには次の信号線があります。

- TDI-テストデータ入力-データ入力信号。データはTCKの立ち上がりエッジに沿ってシフトされます。

- TDO-テストデータ出力-TCKのトレーリングエッジで進められるJTAGシリアルデータ出力は、データが送信されていないときは3番目の状態-Z-である必要があります。

- TMS-テストモード選択-TAPの制御信号-コントローラー。

- TRST-テストリセット-は常に存在するとは限りません。TMS= 1をしばらく保持することでリセットを達成できるため、アクティブな信号レベルは0です。

- TCK-テストクロック-クロック周波数。

JTAG-同期インターフェース。信号はクロックパルスのリーディングエッジで受信され、最下位ビットが前方に、TAPコントローラーShift-DR \ Shift-IRの状態でのみ受信されます。 出力は後縁にプッシュされます。

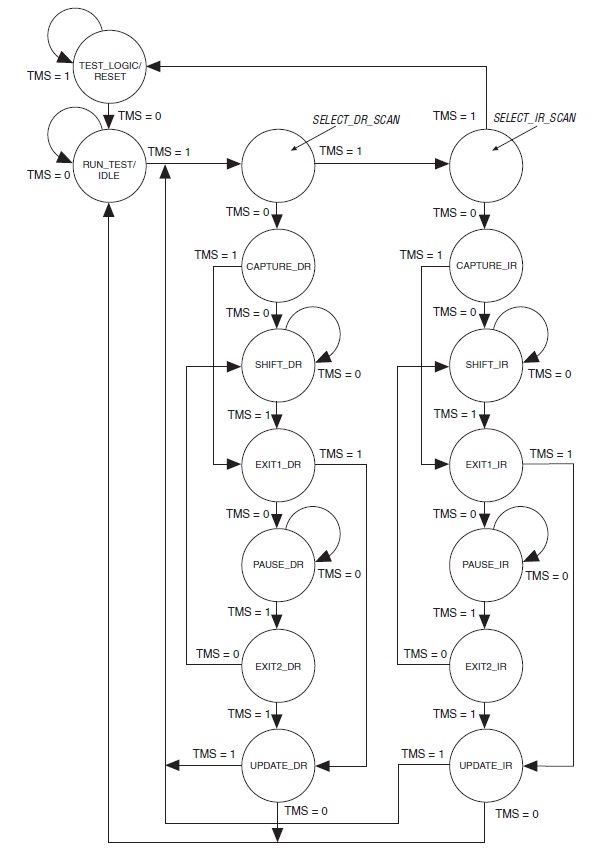

TAP-コントローラー

JTAGの中核、つまり作業を制御するマシンに到達しました。 実際に、すべてが存在します。 マシンには16の状態があります。 インターフェイスは、TMS信号を介してマシンに作用することにより制御されます。 遷移は、TCK信号の立ち上がりエッジで発生します。 データの読み取りと書き込みは同時に行われます。 以下は、アルテラのマイクロ回路のドキュメントから取得した作業の図です。

TAPモードを制御するオートマトンの遷移図

変換チャートの状態:

- Test-Logic-Reset-初期状態。

- 実行テスト/アイドル-テストの実行時または次の待機時のコントローラーの遷移状態

- チーム

- Select-IR、Select-DR-コマンドとデータのテストが実行される後の状態。

- Capture-IR、Capture-DR-コマンド、データの受信状態。

- Shift-IR、Shift-DR-コマンド、データのステータスをシフトします。

- Exit1-IR、Exit2-IR-コマンドの操作モードを終了します。

- Exit1-DR、Exit2-DR-データモードを終了します。

- Pause-IR、Pause-DR-一時停止状態。

- Update-IR、Update-DR-出力レジスタのデータを上書きする状態。

スイッチをオンにした後のマシンの初期状態は、テストロジックリセットです。 TMS信号が「log.1」に設定されている限り、マシンの状態は変更されません。 この状態では、デフォルトでIDCODEまたはBYPASSステートメントが選択されています。

リセット信号TRSTはオプションであるため、マシンを元の状態にリセットするには、次の手順を使用します。 TMS入力に高レベルの信号を供給し、少なくとも5 TCKクロックサイクル保持する必要があります。 ホストによってTMS信号が低レベルに設定されると、マシンはRun-Test / Idle状態(何も起こらないアクティブ状態)になります。 通常、この状態からSelect-IR状態に切り替えて、新しい命令をコントローラーにロードできます。 ただし、TMS信号の入力がホストからの信号ではなく、低レベルノイズの影響を受ける場合、前の場合のように、マシンはRun-Test / Idle状態に切り替わります。 短期的な干渉(同期周波数の1周期以下の期間)がなくなると、マシンは3クロックサイクル(テストロジックリセット)後に再び元の状態に戻ります。

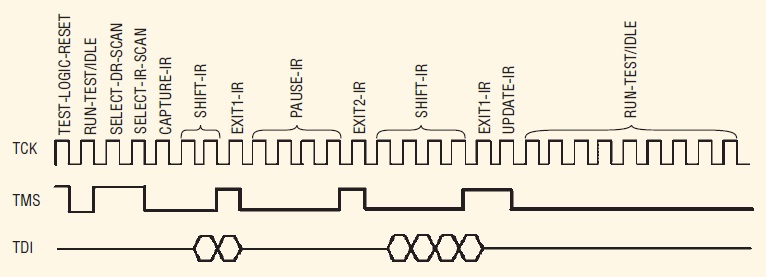

新しいコマンドをコントローラーにロードするには、マシンをRun-Test / Idle状態からSelect-IR、Capture-IR、Shift-IR状態に移行する必要があります。 次に、新しいコマンドをデータチェーンに「プッシュ」し、Exit1-IR、Update-IRの状態を介してマシンをRun-Test / Idleに転送する必要があります。 データを操作するロジックは同じです。 Shift-IR \ DR状態からの移行中に高レベルの信号が情報の最後のビットとともに提供されることに留意する必要があります。

コマンドをロードするための遷移中の信号図

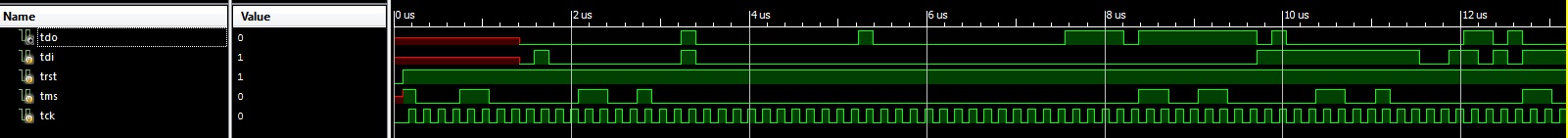

専用のCADソフトウェアを使用してVerilogでJTAGコードを記述する場合、結果の図は次のようになります。

Dropboxリンク、フルサイズの画像

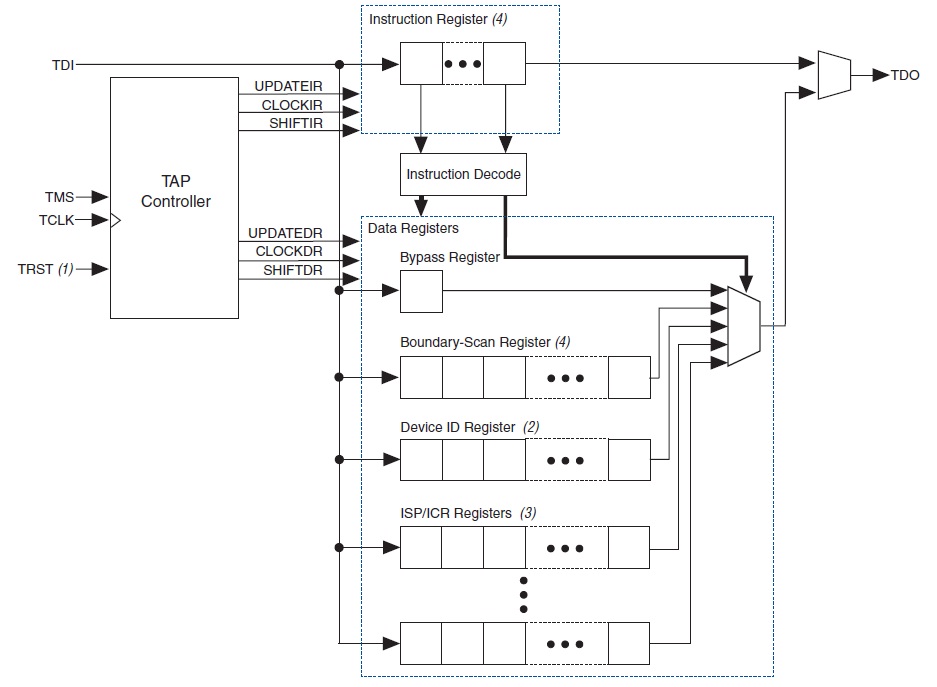

最後に、JTAGデバイスの完全なブロック図を表示できます。完全に理解する必要があります。

...そして結論として...

チップ、ボード、またはデバイスでJTAGとエッジスキャンテクノロジーを使用すると、価値が高まり、プロジェクトの開発時間が長くなります。 しかし、それにもかかわらず、これらのコストはテスト中に簡単に返済され、製品ライフサイクルの各段階で提供されます。 生産テストツールとして最初に開発されたものは、生産開始前、大量生産中、および生産後、つまりエンドユーザーによる運用段階で使用されます。 設計者は、直接境界テストに加えて、JTAGテクノロジーを使用して(実装されているコンポーネントで)自己テスト(BIST)を実行し、デバイスレジスタまたはプログラムROMチップに内部値をロードします。 設計段階で開発および使用されたテストは、最終検査中に製品をチェックするためのコストと時間をさらに削減するために、生産に移すことができます。エラー検索と診断におけるテスト製品の「カバレッジ」を改善し、テスト時間を短縮しながらテストパフォーマンスを改善しました。

製品の動作中に境界スキャンを使用すると、一定のプラスの効果も得られます。 動作障害は、温度、湿度、および振動の上昇によって引き起こされる構造的な障害が原因でよく発生します。 バウンダリスキャンを使用すると、技術者は面倒な調査やボードの製造元への返却をせずに、コンポーネントのレベルまで構造エラーがないか製品をすばやくチェックできます。

参照:

Wiki

アルテラデバイスのバウンダリスキャン

オフ IEEE 1149.1ワーキンググループページ

1149.1-2013-テストアクセスポートおよびバウンダリスキャンアーキテクチャのIEEE標準

JTAGテストに関するHabroの良い記事

KeviのEEVblog JTAG Issue

この記事では、雑誌「Modern Electronics」第2号2007年のデータを使用しました。