FPGAでの実装におけるNintendo Entertainment System(NES)ゲームコンソールのプロジェクトについてお話したいと思います。 ソビエト後の空間では、彼女はデンディとして知られています。

ビデオと懐かしさを見たい人のために、猫の下でお願いします。

私の年齢のほとんどの人はこのゲーム機をよく覚えていると思います。 彼女は私と一緒でした。 90年代には私たちの家族にはあまりお金がなかったので、ダンディさえもいませんでしたが、スーバーの完全に中国のクローンでした。 何度も修理しなければならない頻繁に壊れるジョイスティックを除いて、彼は苦情なしで働いたと言わなければなりません。 もちろん、短い期間の後、私は誘惑に抵抗することができず、接頭辞を解体しました。 ヒートシンクなしで取り付けられたRF変調器とLM7805の電源の2つのプリント回路基板で作成され、非常に高温でした。2つ目のプロセッサボードは、残念ながらシングルチップで作成されました-ドロップ。 私が覚えている限りでは、クオーツ、1対のコンデンサー、それにカートリッジコネクタしかありませんでした。 当時、情報を見つけることは非常に難しく、ダンディがどのプロセッサを実行しているかさえ知りませんでした。 NESを隣人、つまりアマチュア無線との「個別の」実装で見たのは一度だけです。

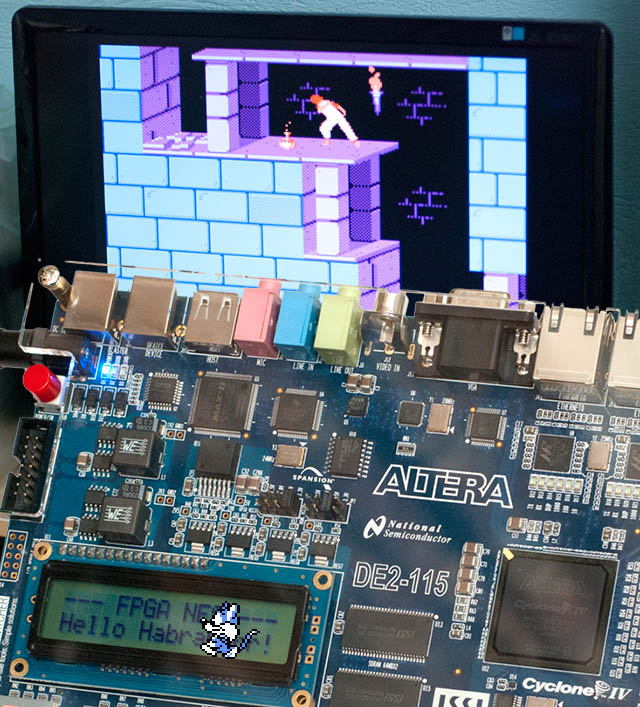

6か月少し前に、eBay STM32デバッグボードを注文し、比較的安価なアルテラCyclone II FPGAを見て、二度と考えずに注文しました。 一般的に、おなじみの電子技術者のフォーラムと意見から判断すると、FPGAのテーマは依然としてアクセス不能とそれを操作する複雑さのハローに包まれています。 私も、このエラーに一度「誘惑され」、FPGAトピックに十分な注意を払っていませんでした。 FPGAに一目loveれしました! マイクロコントローラに従事していた普通のアマチュア無線愛好家にはアクセスできず、物事は突然現実になりました。 たとえば、SDRAMを使用した本格的な作業では、ラップトップマトリックスをLVDSインターフェイスに接続します(そして、その周波数は単にキラーです)。 食欲が高まり、NESプロジェクトに使用されるアルテラDE2-115ボードを購入しました。 今、私は10年前にFPGAのトピックを扱っていないことを非常に残念に思っています。私の間違いを繰り返さないでください。FPGAは楽しくて、まったく難しくありません!

LEDを点滅させた(ちなみに、同じSTM32とは異なり、周辺機器を大量に設定する必要がありますが、FPGAではわいせつです)モニターとサウンドでもっと真剣に取り組むことにしました。

これは何のためですか? 彼らが言うように、ただの楽しみのために。 もちろん、これはすでに非常に古いプラットフォームであり、FPGAで再作成する特別な理由はないと言う人もいるかもしれませんが、個人的には、このプロジェクトに取り組み、最終結果を見るのはとても良かったです。 これは、私がそう言うかもしれない場合、子供の頃からおもちゃを誤って見つけて復元する方法です。

さらに、職場での感覚によると、ハードウェアの実装はソフトウェアシミュレータとは大きく異なります。 これはもちろん、心理的影響でもありますが、FPGAのNESはタイミングをより正確に「キープ」します。ソフトウェア実装では、GPU操作アルゴリズムを最適化する試みによって引き起こされる微妙な遅延やビデオアーティファクトはありません。

ネットワーク上のロシア語では、たとえば、 ここで NESアーキテクチャの説明を見つけることができます。

原則として、説明はかなり良いですが、PPUレジスターはその記事で非常に表面的に説明されているため、それを使用して動作するエミュレーターを作成することはできません-非常に重要な点は省略されます。

この記事では、アーキテクチャと各制御レジスタについて詳しく説明しませんが、エミュレーターの実装で発生する可能性のある問題を指摘し、プロジェクトに適用したソリューションについて説明します。

以下は、ニンテンドーファミコンの電気回路図です。

nesdev.comからの画像

A203(U6)プロセッサのコアは、8ビットマイクロプロセッサMOS Technology 6502に基づいています。6502を備えた1つのチップには、DMAコントローラとオーディオプロセッサがあります。

チップ74LS139(U3)には、CPUアドレスデコーダーが実装されています。 アドレスバスは16ビットであるため、プロセッサは最大64 KBをアドレス指定できます。 アドレス空間は次のように配布されます。

グラフィックプロセッサ(PPU)2C02-U5チップ。 PPUピンを節約するために、アドレスバスの下位8ビットはデータバスと多重化されるため、メモリアクセスに2クロックサイクルを費やします。 アドレス逆多重化には、U2チップ-レジスタラッチ74LS373(IR22のアナログ)が使用されます。

1ビデオページを保存するには、1 KBのメモリが必要です(背景画像は8x8ピクセルのブロック(タイル)で構成され、32タイルの30行が画面に配置されます)。 PPUアーキテクチャは4つのビデオページの使用を提供しますが、2KBのビデオメモリ(U4チップ)のみがNES自体にインストールされます。必要に応じて、2KBが欠落しているため、4ページすべてをカートリッジに配置する必要があります(ページリフレクションとPPUアドレススペースについては後述します)。 正直なところ、エンジニアとしての私にとっては、少しワイルドに見えます。 セットトップボックスの開発中に、カートリッジのコストを増やすことを犠牲にして、マーケティング上の理由とより安価なセットトップボックスのためにそのような手段が取られたことは明らかです。 当時の4 KB SRAMのコストはわかりませんが、おそらくこのために、4ページを使用するゲームはあまりありません。

マスタオシレータはトランジスタQ2、Q3で作成され、NTSCバージョンでは21.47727 MHz、PALでは26.6017 MHzの周波数を生成します。 CPUコアは約1.79 MHzの周波数で動作し、PPUピクセル周波数はCPU周波数の3倍であり、およそ5.37 MHzに等しくなります。 ジェネレーターの比較的高い周波数-24.47727 MHzは、コンポジットビデオ信号のカラー情報をエンコードし、カラーサブキャリアの「フラッシュ」を生成するために必要です。

カートリッジエミュレーション

最初は、元のNESカートリッジを見つけて使用したかったのですが、成功しませんでした。カートリッジをエミュレートする必要があるため、これは良いことです。 最も単純なバージョンでは、カートリッジは2つのROMチップ(CPUプログラムメモリ(PRG ROM)とPPU文字ジェネレータメモリ(CHR ROM))のみです。この場合、PRG ROMの最大容量は32 KB、CHR ROMは8 KBです。 スーパーマリオブラザーズ1、ロードランナー、ポパイなどのシンプルなゲームを実行できます。 もちろん、32 KBは多かれ少なかれ深刻なゲームには非常に小さいため、特別なソリューション(マッパー)を使用してメモリバンクを切り替え、利用可能なボリュームを数メガバイトに拡張できます。 マッパーには多くのオプションがあります。たとえば、74シリーズのディスクリートロジックの両方にあります。たとえば、UxROMマッパーは74HC161カウンター上に構築され、ラッチと74HC32-4 ORエレメントの両方、およびMMC3などの特殊なASICソリューションを使用します。 これで、プロジェクトはこれら2つのマッパーのみを実装します。 MMC3は偶然選ばれませんでした。みんなのお気に入りのゲームの大部分がリリースされたからです。

平均カートリッジサイズは約256 KBです。1MBを超えるボリュームのカートリッジは非常にまれです。 DE2-115には、2 MBのSRAM(1M x 16)と128 MBのSDRAMがあります。 私は

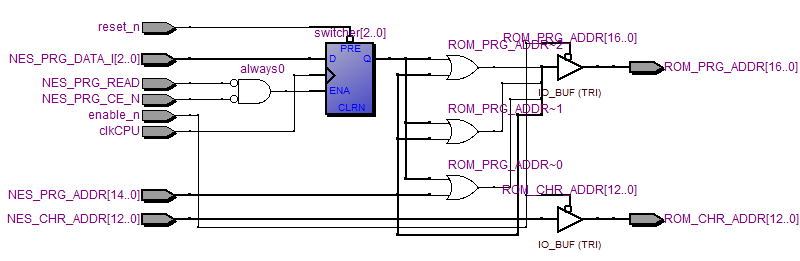

この図は、カートリッジエミュレーションユニットを示しています。

ユニットは、4ビットアドレスバスと8ビットデータバスでNios IIプロセッサに接続されます。 ブロックコントローラーには、NESの状態を制御できる7つの制御レジスタがあります-一時停止、ハードウェアリセットの実行、ビデオページのリフレクションのオプションの設定、マッパーのタイプ、アドレスバスPRGおよびCHR ROMの解像度。 イメージをダウンロードするには、ブート領域(CHRまたはPRG)を選択し、アドレスをリセットするコマンドがあります。 次のバイトが書き込まれた後、アドレスは自動的にインクリメントされます。

アドレスバスはPPUとCPUで共通であるため、マルチプレクサユニットは高い周波数で動作します。私の場合は32.22 MHz-PPU周波数の6倍です。 さらに、個別のアドレスバスがMMC3およびUxROMが実装されているマッパーのブロックに移動し、アクティブなマッパーの選択により制御レジスタの状態が設定されます。 必要に応じて、他のマッパーのサポートを追加するのは非常に簡単です。

たとえば、UxROM実装は次のようになります。

元のNESでは、ハードウェアの観点から、カートリッジがキャラクタージェネレーターROMの代わりにRAMをインストールし、プログラム実行中に初期化してPPUレジスタを介して書き込むことを妨げるものはありません。 このようなカートリッジとゲーム、たとえば、Contra、Castlevania、およびUxROM上の他の多くのゲームが存在します。 このアプローチには利点があります。たとえば、キャラクタージェネレーターアイコンの一部をプログラムで合成できます。また、キャラクタージェネレーターのコンテンツを圧縮形式で保存し、CHR RAMで解凍することができます。これにより、カートリッジのスペースを大幅に節約できます。

すでにRAMを使用してCHRを保存しているため、この機能がデフォルトであることがわかりました。

入る

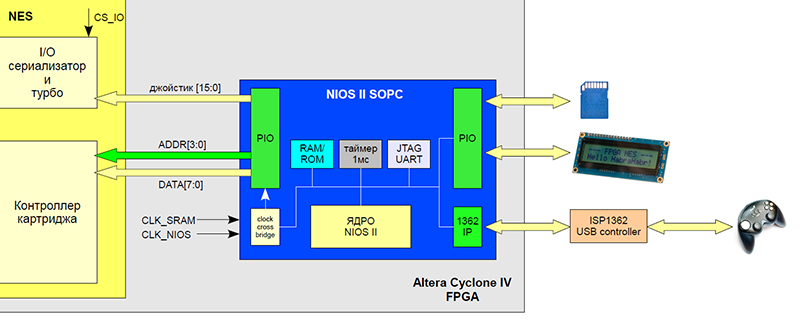

入力デバイスはUSBジョイスティックを使用します。 USBメンテナンスもNios IIプロセッサによって実行されます。

すべてのジョイスティックボタンの状態は1つの単語にまとめられ、パラレルバスを介してシリアライザーブロックに入ります。 アドレス0x4016で記録するNESプロセッサはストローブパルスを生成し、ステータスバイト(8ボタン)がシフトレジスタにロードされます。 さらに、0x4016(最初のジョイスティックの場合)および0x4017(2番目の場合)にアクセスすると、次のボタンの状態がシフトされ、読み取られます。 元のNESの「Turbo」ボタンはジョイスティック自体に実装され、A / Bボタンを頻繁に押すことをシミュレートします。つまり、NESは実際に「Turbo A」または「A」のどちらのボタンが押されるかを区別しません。 プロジェクトでは、この機能はシリアライザーブロックで実行され、周波数は約20 Hzです。

PPU

機能的に、PPUはバックグラウンドレンダリングユニットとスプライトレンダリングユニットに分割できます。

ソフトウェアエミュレーターについて話す場合、レンダリングアルゴリズム自体は単純ですが、CPUとPPUが同期して動作するという事実により、正しいソフトウェアエミュレーターを作成することは非常に難しいタスクであることに注意してください。 より正確には、額にPPUソフトウェアエミュレータを実装するのは非常に簡単ですが、そのような実装は多くのリソースを消費し、最適に動作しません。 画面上にタイルの配列があり、文字ジェネレーターがあれば、フレーム全体、または少なくともその一部を描画できると最初に考えるのはプログラマーだと思います。 もちろん描画できますが、ここではPPUとCPUの同期動作に関する問題が始まります。 グラフィックエフェクトを作成するために、CPUはフレームのレンダリングプロセスでPPU制御レジスタを直接変更し、フレーム中に複数回、キャラクタージェネレーターのメモリバンクを切り替えることができます。 そのようなアクションは、垂直および水平の両方のギャップ、固定領域、あらゆる種類の静的情報の出力で画面をスクロールすることで実装されます。 したがって、CPUがPPU制御レジスターでアクションを実行する時点を正確に知るには、各CPUコマンドが実行されるサイクル数まで、これらのポイントを考慮する必要があります。

このような機能により、一部のソフトウェアエミュレーターは、特にPPUの機能を標準外で使用するゲームで視覚的なアーティファクトを引き起こします。

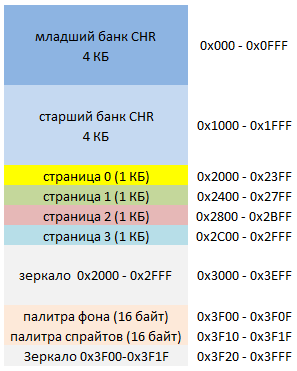

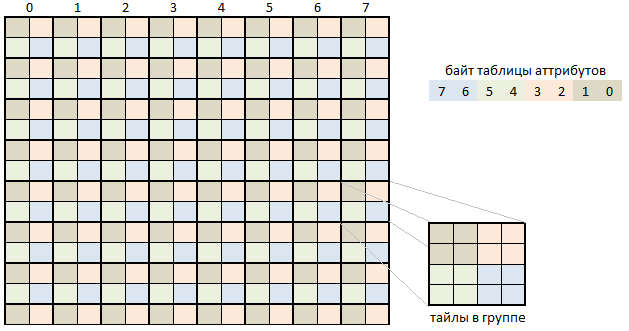

PPUアドレス空間は次のように配布されます。

ビデオページは、たとえば、水平スクロールまたは垂直スクロールを使用して、2ページのコンテンツが画面に一度に表示され、対角線が4つになるように配置されます。 ページレイアウトと座標を図に示します。

上記で書いたように、NES自体のページメモリの下には2 KBのRAMがあります。 したがって、不足しているメモリがカートリッジにインストールされていない場合、ページの反映が適用されます。 垂直、2番目のページがゼロを反映し、3番目-最初のページ、および水平-最初のページがゼロ、3番目-2番目を反映します。

FPGAプロジェクトで2 KBを節約しても意味がないため、4 KBのすべてがビデオメモリに割り当てられます。 ハードウェアリフレクションは非常に簡単に実装されます-アドレスバスでの垂直リフレクションの場合、RAMがPPUから切り離され、11番目のビットラインがゼロに接続され、垂直の場合、11番目と10番目のビットが交換され、最も古いラインもゼロに接続されます:

一部のマッパーは、アドレスバスラインを切り替えることでページリフレクションオプションを動的に変更できます。 たとえば、スーパーマリオブラザーズというゲームです。 2、ゲームの開始時に落下するとき、水平反射が使用され、垂直に切り替わります。

PPUレジスタ

PPU 8との対話には、レジスタが使用されます(CPUのアドレス空間を意味します)。

レジスタ0x2000(書き込み専用)

このレジスタは、PPUのステータスを監視します。たとえば、スプライトのサイズ(8x8または8x16)、ビデオメモリページ、およびNMI割り込みを生成する許可を設定します。

レジスタ0x2001(書き込み専用)

Registerは、スプライトと背景を描画する許可を設定します。 また、レンダリングをまったく禁止するために使用でき、CPUはいつでもPPUメモリ領域にアクセスできます。これは、ゲーム環境を変更し、ROMの代わりにRAMが使用された場合はCHR RAMを埋めるときにページの初期初期化中にゲームで使用されます PPUメモリへのアクセスは、PPUがアクセスしないVBLANK期間にのみ禁止なしでアクセスできます。

レジスタ0x2002(読み取り専用)

このレジスタには、PPUステータスフラグが含まれています。 これは、ゼロスプライトの最初の不透明なピクセル、VBLANK期間の開始、および8つ以上のスプライトが現在の行に落ちることを示すフラグが描画され始めたという事実です。

レジスタ0x2003(書き込み専用)

スプライトメモリ(オブジェクト属性メモリ-OAM)の後続の操作のアドレスを指定します。

レジスタ0x2004(書き込み/読み取り)

OAMデータの読み取りと書き込み。 操作後、アドレス値の自動インクリメントが発生します。 通常、ゲームはこの方法でOAMに書き込むのではなく、DMAを使用します。

レジスタ0x2005(書き込み専用)

スクロールレジスタ。 レジスタへの最初の書き込み操作では、水平スクロールの値が設定され、2番目-垂直方向に設定されます。

レジスタ0x2006(書き込み専用)

ビデオページの後続のメモリ操作のアドレスを指定します。 最初の操作では、アドレスの最も高い部分が指定され、2番目の操作では最も若い部分が指定されます。

レジスタ0x2007(書き込み/読み取り)

ビデオページメモリからのデータの読み取りと書き込み。 操作後、アドレス値は1(次の列)または32(次の行)で自動的にインクリメントされます。これは、レジスタ0x2000のビット2の状態に依存します。

二重書き込みレジスターは共通のトリガーを使用するため、たとえば、0x2005に1回書き込み、次に0x2006に書き込み、そして再び0x2005に戻ることはできません。 より正確には、できますが、これを行うには理解する必要があります。 トリガーの状態が不明な場合は、レジスタ0x2002を読み取ることができ、トリガーがリセットされます。

簡単ですね! ただし、上記のロシア語の説明には示されていない非常に重要な機能があります。

事実、リストされているレジスタは、いわば、完全に独立しているわけではありません。

2つの15ビットレジスタがあります。

vVRAM-現在のビデオメモリアドレス(以下、単に「v」)。

tVRAM-一時アドレス(以下、単に「t」);

Xでの「正確な」スクロールの3ビットレジスタ(細かいXスクロール)。 1タイル内でスクロール(0..7)を設定します。

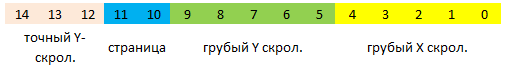

アドレスvとtは次のように形成されます。

したがって、レジスタ0x2000への書き込みによってページを設定すると、レジスタtのビット11,10が変更されます。 レジスタ0x2005に書き込むと、レジスタtのビット4:0および9:5/14:12の値とXでスクロールする「正確な」値が設定されます。しかし、レジスタ0x2006に書き込むと、すべてのビットの値を一度に変更できるため、すべてが台無しになる可能性がありますレジスタt。2回目の書き込み操作では、v = tがコピーされます。

線を描くプロセスでは、PPUはレジスタvで粗スクロールの値をXだけ増やし、粗スクロール値がオーバーフローするとビデオページのアドレスを変更します。 可視ラインの終わり(ピクセル256-257)で、PPUはY値を増やし、水平スクロールに関連するコンポーネントをコピーします(v [4:0] = t [4:0]およびv [10] = t [10])。 新しいフレームを開始する(プリレンダリング)前に、垂直スクロールのコンポーネントがコピーされます(v [9:5] = t [9:5]、v [14:12] = t [14:12]、v [11] = t [ 11])。 そして、すべてが再び始まります。

PPUレジスタの値を変更することで、さまざまなバックグラウンドティア効果を得る方法が明確になりました。

画像形成について少し

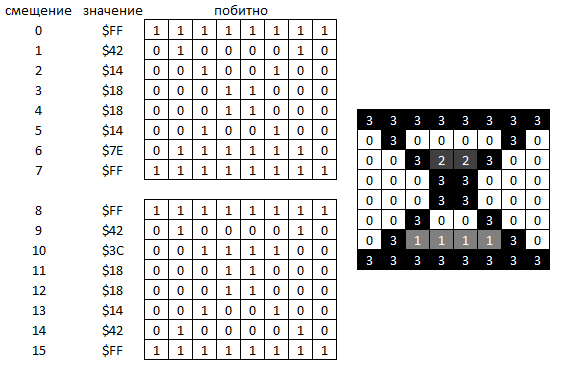

各ピクセルの色はパレットから選択されます。 背景とスプライト用の個別のパレットがあります。 パレットは16バイトのメモリ領域です。 背景パレットのゼロ要素は、キャンバスの色を設定します。 背景ピクセルをレンダリングするとき、パレットの色要素を指す4ビットアドレスが生成されます。 アドレスの2つの最上位ビットはタイルグループの属性の値であり、2つの最下位ビットは文字ジェネレーターからの画像によって設定されます。 グループの属性を変更することにより、キャラクタージェネレーターの同じ要素を使用してタイルの色を変更できます。

ビデオページ(名前テーブル)の最初の960バイトは、ページにあるCHR文字ジェネレーターからのタイルのアドレスを指定します。 属性ページの残りの64バイトはそれぞれ、属性を16タイルのグループ(32x32ピクセル領域)に設定します。

16バイトは、1つのアイコンのイメージを文字ジェネレーターのメモリに格納するために使用されます。 前述のように、各ピクセルは2ビットでエンコードされます。 最初の8バイトはピクセルの下位ビットを参照し、次の8バイトは上位ビットを参照します。 つまり、バイトのペア0 + 8、1 + 9など。 行のアイコンを設定します。

例の色は条件付きで選択されます。ゼロに等しい要素は透明であり、属性値はそれらに影響しません。

グループ属性は次のように設定されます

。PPUの1クロックサイクルで1ピクセルを描画する必要があります。元のNESでは、2サイクルのPPUでメモリから1つの値しか取得できないことを理解する必要があります。したがって、HBLANK期間の終わりに行の開始前に、新しい行の最初の2つのタイルのデータがサンプリングされます。

タイルラインの出力に必要なデータは、PPUの8サイクルでサンプリングされます。まず、ビデオメモリから、文字ジェネレーターのタイルアドレス(2メジャー)、次にグループ属性値(2メジャー)、次に文字ジェネレーターからのタイル行の下位バイト(2メジャー)、最後に、タイルの最上位バイト(2メジャー)を取得します。そして、すべてが再び始まります。

アドレスバスとデータバスを多重化していないため、プロジェクトでは各PPUクロックでデータを受信できます。

スプライト

PPUレジスタを説明するセクションで、スプライトメモリの領域-オブジェクト属性メモリ(OAM)に言及しました。サイズは256バイトで、別のアドレス空間のPPUチップ上にあります。つまり、この領域へのVRAMやCHR ROMの同時アクセスが可能です。

OAMの各スプライトには4バイトが割り当てられているため、一度に画面に表示できるスプライトは64個までです。

スプライトの画像もキャラクタージェネレーター(CHR ROM)に保存されます。

画面上の各スプライトは、XとYの画面上の位置、文字ジェネレーターのアイコンのアドレス、属性(背景をレンダリングするときのグループ属性と同じ)、スプライトの水平および垂直反射フラグ(1つのアイコンの半分を使用して対称オブジェクトを表示できます)によって記述されますジェネレーター)および優先順位のフラグ。

スプライトのサイズは8x8および8x16ピクセルです。

スプライト画像の形成は、背景画像の形成と変わりません。ただし、ハードウェアの実装にも独自の特性があります。

線が描画されると同時に、次の行に表示される(範囲評価の)スプライトの検索が行われます。 PPUには、8つのスプライトに関する情報を保存できるセカンダリOAMがあります。検索中に次の行に8個以上のスプライトがあることが判明した場合、余分なスプライトは無視され、PPUレジスタ0x2002でフラグが立てられてこれを通知します。

CHR ROMバスは線の描画中にビジーであるため、これらの8つのスプライトのピクセルカラーに関するシンボルジェネレーターからのデータは、HBLANK期間にサンプリングされます。

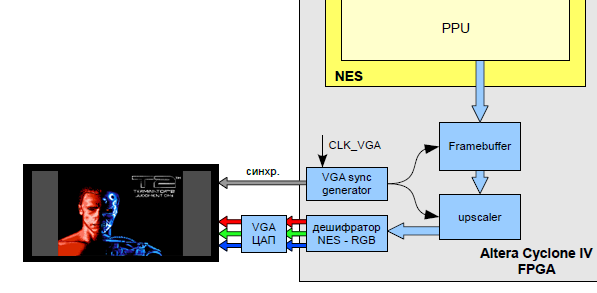

NESは、256x240ピクセルの解像度で画像を形成します。画像を表示するには、VGA 640x480の標準解像度を使用します。PPUは画像をフレームバッファーにレンダリングします。フレームバッファーからのデータは、解像度が2倍になったブロックに入ります(アップスケーラー)。将来的には、hq2xを実装します。ビデオDACにデータを適用する前に、色はRGBに変換されます。

DMAコントローラー

OAMにすばやく入力するために、NESプロセッサはDMAコントローラを使用できます。DMAコントローラは非常に簡単に実装されます。コピー操作を開始する前に、CPUはOAM開始アドレス(レジスタ0x2003)を設定するか、0にリセットする必要があります。その後、CPUはアドレス0x4014にCPUのアドレス空間の開始アドレス(0x ?? 00)の値を書き込みます。DMAコントローラはCPUを停止し、領域0x ?? 00〜0x ?? FF(??はCPUによって指定された値)からPPUレジスタ0x2004への256バイトのコピーを開始します。PPUは、書き込み操作ごとに1つずつOAMアドレスを増分します。手順の最後に、DMAコントローラーは制御をCPUに戻します。

優先度とスプライト0ヒット

ピクセルの色の最終的な値は次のように形成されます。

複数のスプライトが同じ領域に存在する可能性が非常に高く、しばしば発生します。

この場合、画面への出力の優先度は2つの要因の影響を受けます。これは、OAMのスプライトアドレスの値と優先度フラグ(0-前景、1-背景)です。たとえば、優先フラグが背景に属することを示しているが、OAMのアドレスの値が前景のスプライトの値よりも小さいスプライトの場合、背景のスプライトは前のスプライトを閉じることができるため、背景のピクセルが出力されますが、透明でない場合。

アドレス0でスプライトの最初の不透明なピクセルをレンダリングすると(この時点で背景も不透明でなければなりません)、レジスタ0x2002でフラグが立てられ、Sprite 0ヒットイベントが発生したことを示します。このフラグの適用例は、スーパーマリオブラザーズです。1、それは画面を壊し、プレイエリアからポイントと時間に関する静的な情報を分離するために使用されます。コイン画像は背景として機能し、その影はゼロスプライトとして機能します。CPUは定期的にフラグの値をチェックし、イベントが発生すると、競技場の出力が開始されます。

マッパーMMC 3からの中断

マッパーMMC3には行カウンターが含まれており、次のPPU行が表示されると値が減少します。ゼロに達すると、カウンタは、マッパーの対応するレジスタに事前に書き込むことで設定できる値でリロードされ、有効フラグが設定されている場合、CPU割り込みが発生します。カウンタークロッキングラインはかなり独自の方法で構成されています-GPUのアドレスラインA12に接続されています。背景タイルを保存するには、通常、下位バンク(領域0x000-0x0FFF)を使用し、スプライト-シニアバンク(領域0x1000-0x1FFF)を使用します。可視線を描画するとき、PPUは1つのバンクを参照し、HBLANKでスプライトイメージデータをフェッチするとき、ピリオドは別のバンクを参照します。したがって、ラインA12の周波数はライン出力周波数に対応します。マッパー割り込みは、主に画面を壊し、サインジェネレーターバンクを切り替えるために使用されます。

ビデオの例を見ることができます。

APU

NESオーディオプロセッサは、CPUと同じチップ上にあります。機能的には、APUは一連の制御レジスタ、フレームカウンター、およびオーディオチャネルの5ブロックです。

ハードウェアの観点から見ると、APUはカウンターの集まりであり、落とし穴はないため、説明は簡単です。

フレームカウンターは、CPUのIRQ割り込みだけでなく、約240 Hz、APUの場合は120 Hzの周波数のクロックパルスを生成します。割り込み生成は、APUレジスタを設定することでオフにできます。「フレーム」の概念を混同しないでください。この場合、PPUとは関係ありません。

ちなみに、開発中に不快なインシデントが発生し、APUフレームカウンターが既に実装されており、割り込みイネーブルフラグがめちゃくちゃになったため(反転することが判明)、約60 Hzの周波数で割り込みが生成されました。外側では、これは非常に予期せず現れました。ゲーム「プリンスオブペルシャ」では、画面の左側に、グリルのある出入り口が表示されず、これが唯一のグラフィックアーティファクトでした。本当の理由がわかるまで頭を骨折した。もちろん、PPUについても考えました。ModelSimでコードを100回チェックしました。不快でした!

APUには5つのチャネルがあります。

名前が示すように、2つの長方形チャネルは、方形波、1つの三角形チャネル、1つのノイズチャネル、デルタ変調チャネル(DMC)を形成します。

長方形チャネルは、可変デューティサイクル(4階調)と周期を持つ信号を形成でき、持続時間を設定する機能を持ち、スイープブロックとエンベロープブロックも備えています。スイープブロックは信号の周期を時間的に変更(順次増加または減少)でき、エンベロープブロック(エンベロープ)はループの可能性がある時間内に信号振幅を減少できます。この場合のエンベロープの形状は鋸歯状です。

三角チャンネルは、周波数と持続時間が可変の三角信号を生成しますが、音量を調整する機能はありません。

ノイズチャネルは、可変期間の擬似ランダム信号を生成します。ノイズチャンネルには、矩形チャンネルと同様に、エンベロープコントロールユニットがあります。

プロジェクトのデルタ変調のチャネルはまだ実装されていません。

LEの消費に関して「重い」操作を使用しないように、チャネルの混合は表形式で実行されます。

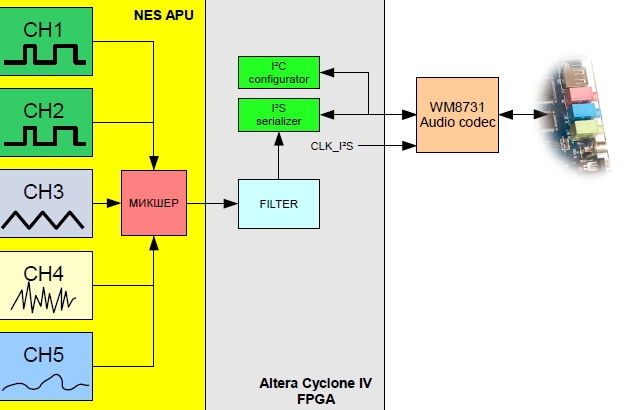

ミキシング後、信号はドメイン同期ブロックとフィルターに入り、その後、I2Sバスを介してシリアライザーブロックを介してWM8731オーディオコーデックに送られます。

プロジェクトを実装するときに、Verilog 2001ハードウェア記述言語を使用しました。

, , , , . , , . . , , , GNU GPL.

ご清聴ありがとうございました!