おそらく、現在のデジタルテクノロジーとそのコンポーネントに規定されている基本的なアイデアと原則が、コンピューター標準による遠い過去、つまり前世紀の中頃に由来することは、ハブラの人々にとってはニュースではないでしょう。 その後、過去50年間、IT分野の最大の(そしてそれほど大きくない)企業によって成功裏に開発、改善、販売されてきた基盤が発明されました。もちろんIntelもそのランクにあります。 しかし、すべての証拠で、この状況は間違いなく悲観的な態度を呼び起こします。すべての素晴らしいアイデアが終わり、私たちの世代は過去の偉大な遺産でささいなピッキングをする運命にありますか?

このブログの具体的で驚くべき例の1つを検討してください。プロセッサアーキテクチャの改善を考えている人の考えを見てください。

まず、必要な説明-超スカラー性の定義を示します。 最も単純なスカラー計算操作では、2つのオペランドが含まれます。 ベクトル演算では、2組の数値に対して実行されます。 中間(または混合)オプションがあります:同時に、過剰な数の処理セルが存在するため、さまざまな操作がスカラーの異なるペアで実行されます-このアプローチはスーパースカラーと呼ばれます。

コマンドのスーパースカラー実行の概略図

誰がスーパースカラープロセッサを最初に作成したのか、それがアメリカの科学者であったのかソビエトの科学者であったのか、そして何年にそれが起こったのかについては掘り下げません。 さらに重要なことに、スーパースカラーは現在運転しており、これまでのところ、実際の敵には見えません。 ただし、スーパースカラーの原理の単純な開発は、現在、イデオロギーの制限に基づいています-現在のアプローチでは、それ以上は絞りません。 スーパースカラーアプローチは、原則として、RISCアーキテクチャとCISCアーキテクチャの両方に等しく適用できます。 RISCは、より単純なコマンドシステムのおかげで、従来の開発方法論の枠組み内でオーバークロックする可能性がまだあります。現在、コンピューティングパワーの成長のダイナミクスが印象的なARMの例でこれを観察しています。 ただし、スーパースカラリズムの本質によって決定されるため、あちこちで「ジャンルの危機」は避けられません。

問題は何ですか? プロセッサが実行するタスクの複雑さ。 その場でスーパースカラーがシリアルコードを並列化します。 しかし、この並列化プロセスは、現在のプロセッサの処理能力にとっても手間がかかりすぎるため、マシンのパフォーマンスが制限されます。 サイクルごとに一定数の命令よりも速くこの変換を行うことは不可能です。 あなたはもっとできますが、同時に時計仕掛けは落ちます-このアプローチは明らかに無意味です。 チームの数の合理的な制限は現在、すべての側面から研究されており、改訂の対象ではありません。

スーパースカラーは素晴らしいアーキテクチャと呼ばれますが、シーケンシャルに記述されたプログラムの非常に優れた実装です。 問題はスーパースカラー自体ではなく、プログラムのプレゼンテーションにあります。 プログラムは順番に表示され、実行中に並列実行に変換する必要があります。 スーパースカラーの主な問題は、入力コードがそのニーズを満たせないことです。 カーネルの並列アルゴリズムと並列に編成されたハードウェアがあります。 しかし、それらの間には、真ん中に、特定の官僚組織、つまり一貫したコマンドシステムがあります。 コンパイラは、プログラムをシーケンシャルコマンドシステムに変換します。 プロセスの全体的な速度は、彼がこれを行う順序に依存します。 しかし、コンパイラはマシンがどのように動作するかを正確に知りません。 したがって、一般的に言えば、今日のコンパイラの仕事はシャーマニズムです。 彼はただ見ているだけです:「あなたがそれを再配置すれば、それはより速くなるでしょう。」 おそらく。

これは有益な例です。 プリフェッチは、プロセッサキャッシュにデータを事前に読み込むことができるテクノロジーです。 約10年前に発明され、システムのパフォーマンスにとって非常に有益であると考えられていました。 そして、プリフェッチを無効にすると、コンピューターの動作が1.5倍速くなることがわかりました。 問題は、1つのCPUモデルでプリフェッチがデバッグされ、他のモデル(プロセッサが自動プリフェッチを実行する)で使用されることです。現在のさまざまなプロセッサパークに適応するよりも、単にオフにする方が簡単です。 そして、そのようなケースは現在、常に起こっています。

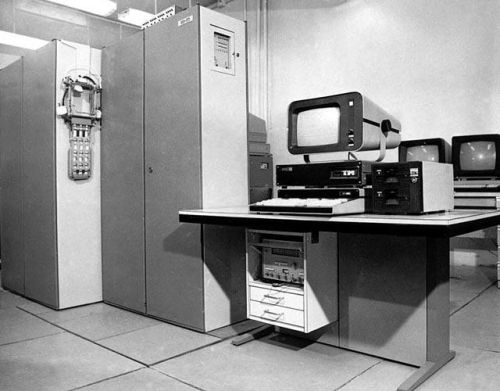

「Elbrus-1KB」-ソビエトのスーパースカラーコンピューター

コンパイラーがスーパースカラー用のプログラムを作成するのがどれほど難しいか想像できます。 しかし、機器はさらに困難です。 スーパースカラーの機能を確認してください。実行コマンドの順次表示を並列に変換し始めます。 順次表示では、すべてのデータ依存関係が削除されます。 ただし、正しい順序でレジスタにアクセスする必要があります。同じレジスタへのアクセスを再配置しないでください。 また、チームをスーパースカラーに再配置するには、すべての依存関係を知る必要があります。 したがって、コンピューティングストリーム全体を元に戻します。 ホラー-最悪の事態は想像できません。 そして、それを最適化しようとすることは、根本的な変更というよりもパッチングホールに似ています。

30年前でさえ、ソビエトのElbrusシステムを設計するコンピューターテクノロジーの開発者は 、スーパースカラーは優れたアーキテクチャであるが、複雑で不合理に複雑であることを理解していました。 さらに、速度制限があります。 根本的に新しいアプローチが必要でしたが、最も重要なことは、つまずきを取り除く必要がありました-チームの一貫したプレゼンテーションです。 マシンはすべてを並行して受信する必要があり、これは非常に簡単なソリューションになります。 それは完璧です。 また、古いコードと新しいアーキテクチャの間の互換性の問題は、 バイナリコンパイルを使用して解決できます。

このアプローチの別の可能性は、複数のコアを使用する機能です。 これはコンピューティングの計画ではなく、単にリソースを共有することです。 リソースを静的に「計算部分」に分割します。 スーパースカラーはこれを行うことができません。複数の部分にうまく分割するためには、先読みする必要があるためです(プログラムだけがこれを行うことができます)。 実際、単一のスレッドの代わりに、明示的な並列処理が行われます。 これにより、多くの制限を取り除くことができます。

プロセッサのハードウェア並列処理のバリエーションは、さまざまな研究グループによって繰り返しテストされています。もちろん、そのような開発はインテルでも行われています。 その結果の1つは、VLIWアーキテクチャ(非常に長い命令語)を使用したItaniumプロセッサでした 。 VLIWは、並列処理を作成する負担がすべてコンパイラの負担になり、プロセッサがすでに命令の適切かつ適切な並列ストリームを受け取っている場合に、上記で表されたアイデアの化学的に純粋な実装です。

Intel Itanium 2プロセッサー

並列の未来に向けた別の有望な動きは、多数の小核を持つプロセッサです。ここでは、ほとんどのハードウェアベースの方法でマルチスレッドが実現され、各コアはスーパースカラリティメカニズムもサポートします。 Intelでは、この種の開発はMIC( Many Integrated Core Architecture )のフラグの下にあります。 このプロジェクトはいくつかの開発段階を経ており、ある段階から別の段階への移行に伴い、製品の優先順位と位置付けが少し変更されました。これについては、すぐに別の話があります。

小計を要約します。 現在、根本的な開発が行われており、これが私たちの生活/将来のプロセッサの理解を根本的に変えることができますか? はい、間違いなく、今日私たちが話したことの多くは、50年後のデジタル技術の歴史に関する教科書に含まれるでしょう。 さて、Intelブログ(他の場所)では、この締め切りを待たずに、プロセッサのフロントからのニュースをさらにお知らせすることをお約束します。