提案された方法は普遍的ですが、標準的ではなく、「何があっても」創造的な楽観主義の存在を意味します。

FTPサーバーがあったことがあります。 実際、それは通常の2004年のコンピューターでした。 ここでポイント 7で、ルーターのARPテーブルを設定するのにこのようなWOLと微妙さがあり、このコンピューターが(コンピューターの電源がオフになった後)ハングするポートを忘れないようにしました。 そして、たまたま私はこのビジネスすべてに問題がなかった-対応するオプションがBIOSでオンになり、サーバーが昼夜を問わずいつでもオンになりました。

しかし、すべての良いことは常に終わりがちです。あなたはそれに慣れるか、消えます。 コンピューターは私から奪われました...

しかし、最近FTPの必要性が再び生じました。 そして、将来も彼に何かを掛けたいので、これらの目的のために比較的生産性の高い新しいコンピューターを組み立てることにしました。 そして今、Thermaltake VK72721N2E SD200パッケージのASUS P8H77-M +Intel®Core™i3-2105 + 2 x 4Gb Corsair Vengeance CMZ4GX3M1A1600C9Bプラットフォームが私の場所に登場しました。 ケースのスタイリッシュな外観に対する家庭の熱狂の後、コンピューターは2004年以来恒久的に存在していた解雇されたVHS + DVDコンバインの代わりにテレビの下に押し込まれました。 実験として、私は人生を複雑にし、このサーバーにWindowsを置くことにしました。VMWareは3つの仮想コンピューターでWindowsに入りました。 仮想コンピューターの1つであり、新しいFTPサーバーになりました。 ルーターおよび仮想ネットワーク環境VMWareでポートを転送した後、FTPサーバーは応答し、適切に動作し始めました。

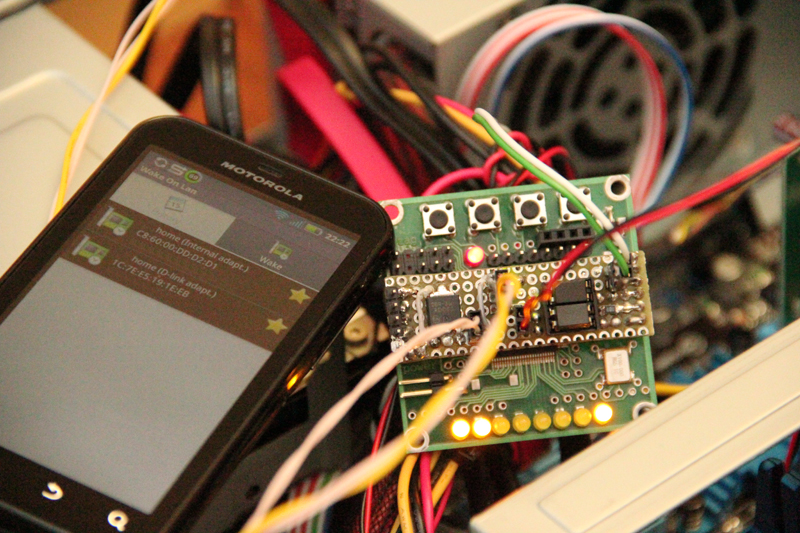

ここでは、もちろん、WOLを思い出し、ルーターのポート転送を修正し、Android用の「Wake On LAN」プログラムをダウンロードしました(以前はwakeonlan.ruサービスを使用していました)。 すべての良いことを覚えていますか? そのため、ある晴れた日、このコンピューターをリモートでオンにすることができませんでした。 私は130GBを持ち運ぶことができなかったので、とにかく悲しくなりました。 悪い言葉は、WOL実装の設計者全般、特にASUSのエンジニアに送られました。 あの日誰かが強くしゃぶってくれたらおaびしますが、本当に悲しくなりました。 デブリーフィングの後、このマザーボードが少なくとも1回はオンになり、後でWOLで起動することが判明しました。 そして、私が家にいないとき

インターネットや知識のある人々の間でこの問題に興味がありました。 知識のある人は通常、より深刻なネットワーク機器を使用しているため、この状況でどのように方向転換するのか実際にはわかりません。 それだけではありません! 多くの人は、これは正常、つまり コンピューターは、コマンドがオンになるのを待つために、どのデバイスの電源をオンにするかを知る必要があります。 そして、かなり多くの人が、「スタート」(???)で電源を入れた場合にのみ、コンピューターが正常に起動することを保証しました。 私は彼らがインターネットで言ったことを語るつもりはないが、率直に言ってmestavmiを楽しんだ。

質問が発生しました:何をすべきか?

たくさんのアイデアがありました。 「通常は目覚める」古代のコンピューターの前向きなシディロムのアイデアから、ネットワークチップのWOL信号を何らかのロジックを介してコンピューターの電源ボタンのコネクターに出力するアイデアまで。 要素ベースレベルで作業する場合の問題は、自宅にオシロスコープがないことです(C1-112Aは考慮されません)。 しかし、私は食欲を抑え、コンピューターのハードウェアに依存しない決定を下すことにしました。 ビンで、D-Link DGE-528Tネットワークカードが見つかりました。 それは素晴らしい白いWOLコネクタを収容します。 ピン配列を見ると、コネクタには3つの信号が含まれています:+ 5VSB、GND、リング。 多くの古いマザーボードにも同じコネクタが存在していましたが、現在ではこの傾向から遠ざかりつつあります。 明らかに、電力はネットワークカードに自律的に供給されます。 電源ボタンが押されたとき、または呼び出し音信号が到着した後、コンピューター自体の電源がオンになりました。 ASUS P8H77-Mにはそのようなコネクタはありません!

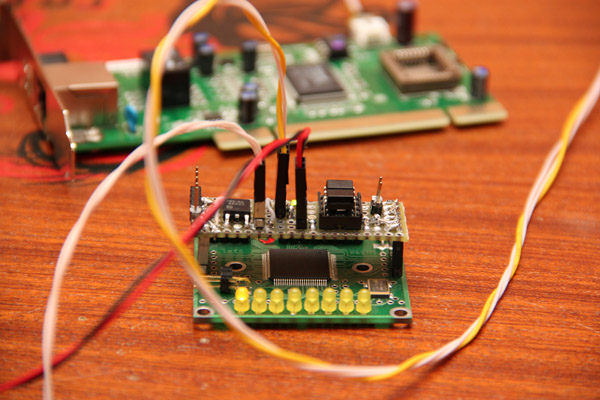

そして、FPGAを搭載した解放されたMarsローバーボードが非常に便利でした。 私は、どのコンピューターにも一生ユニバーサルソリューションを作成することにしました(これも選択できます)。

1)ボードにWOLコネクタを備えたネットワークカードをコンピューターに挿入します。

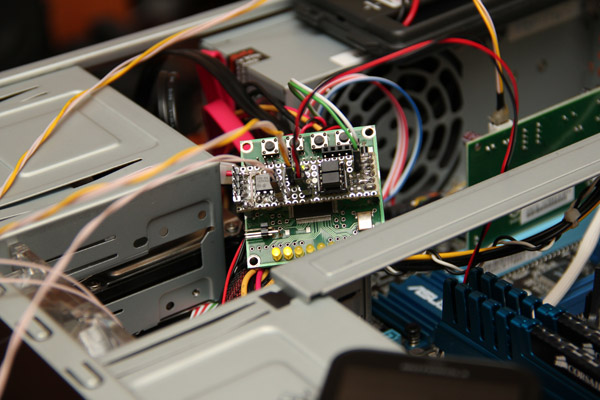

2)コンピューターのどこかで、ボードをFPGAで固定します。

3)WOLのインターフェイスボードをFPGAカードに接続します。

4)ネットワークカードとインターフェイスボードのWOLコネクタを製造された特別なケーブルで接続し、マザーボードの電源ボタンとPWR_BUTコネクタをインターフェイスボードに接続し、このボードで+ 5VSB電源を起動します。

したがって、タスクの範囲の概要を説明します。

1)FPGAには、コンピューターの電源ボタンからの信号とネットワークカードからの呼び出し信号を問い合わせ、検出された場合はマザーボードのPWR_BUTコネクターに信号を送信するファームウェアが必要です。

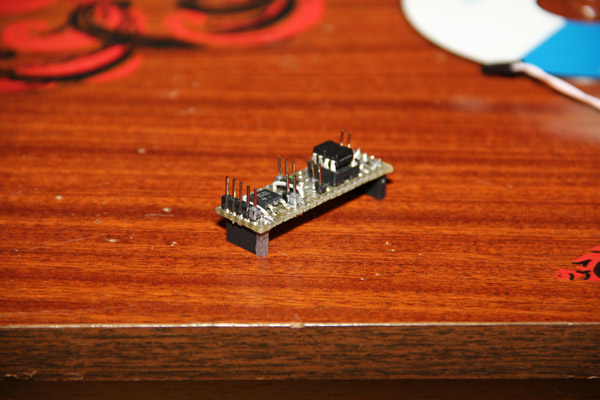

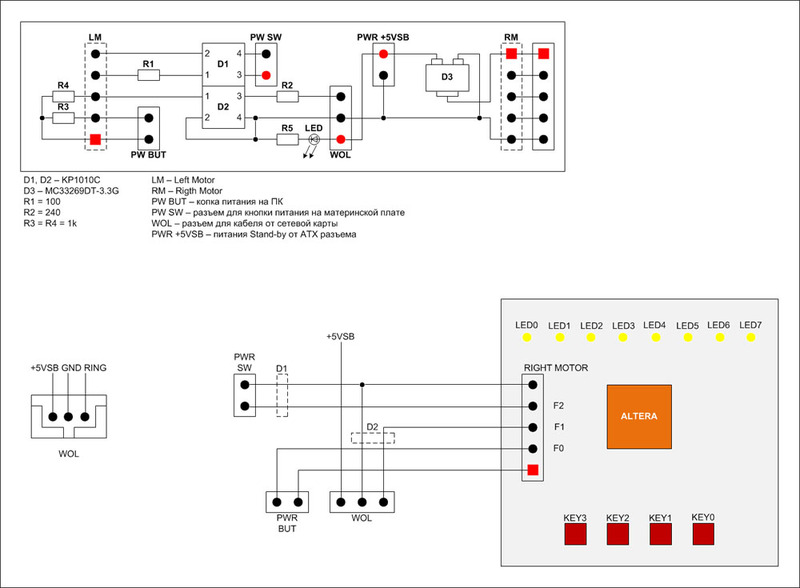

2)インターフェイスボードは、FPGAボードに電源を供給する必要があります(安定器を+ 3.3Vに設定します)。また、万が一に備えてWOLとPWR_BUTを分離しておくと便利です(オプトカプラーをいくつか配置します)。

3)ケーブルを作成する必要があります:WOL用の3線(FPGA側のコネクタは2.54刻みで、ネットワークカードの側面は2mm)、PWR_BUTの接続用の2線(2.54刻みの2つのコネクタ)、電源用の2線2.54の手順で、もう一方の端をマザーボードの電源コネクタ(GNDおよび+ 5VSBワイヤ)に何らかの方法で取り付けます)。

ルコバをロールアップしました。

私は30分でファームウェアを書きました。 ファームウェアは一般的なものです。たとえば、2つのポートを調べて、3番目のポートに0.5秒のパルスを出力します。 電源ボタンのバウンスを考慮し、Ring信号の前面のみを検出し、1日までの範囲およびその他の小さなことで正確な時間ジェネレーターを作成しました-できる限り楽しみました)ファームウェアは最初のオプションよりもはるかに重いことが判明しましたが、FPGAの半分はまだ空いています。 モジュールとしてプロジェクトに接続された世界時ジェネレーターによって多くのスペースが消費されました。

ケーブルも30分で作成しました。 しかし、私はすべてを手元に置いていました-幸運なことにコネクタがあります。

インターフェースボードで、私は翌晩全体に苦しみました。 両面ブレッドボードのプリント回路基板からボード自体を見ました。 このボードは、「Rigth Motor」および「Left Motor」コネクタの「ブリッジ」とともに、火星探査機のボードに装着されています。 「Rigth Motor」はWOLに渡され、2つ目のコネクタをインターフェイスボードに投げました-逆説的に見えるかもしれませんが、彼女の個人的な生活に女性がいないことは、同様に興味深い娯楽に貢献し、彼女がこのボードに他に何を固定したいかはわかりません。 私は配線をはんだ付けするのが面倒で、はんだがたくさんあるので、必要なトラックを「成長」させました。 ugいことが判明したので、原則としてそうすることはお勧めしません。 自宅にDC-DCスタビライザーも見つかりましたが、オプトカプラーはありませんでした。 代わりに、彼はパッドを封印し、1週間すべてが放棄されました。 2週間後、オプトカプラーをセットアップし、これがどのように機能するかを確認することにしました。

最も困難な部分は、ATX電源コネクタの切断でした。 インターネットには、クリップを曲げるために、ステープラーからクリップをコネクタに押し込む方法に関するヒントがたくさんあります(抽出器はありません)。 私はいくつかのウェブサイトでビデオを見さえしました。 しかし、私はコネクタからコネクタから抜け出したくありませんでした。 すべての有名な言葉の助けを求めて、私は針を破り、いくつかのペーパークリップを再スポーツするためにほぼ2時間を費やしました。 しかし、それは文明化されました)

ソリューションは実行可能であり、ケースの電源ボタンからコンピューターのオン/オフを切り替えたり、WOLコマンドを発行してネットワーク経由でコンピューターをオンにしたりできます。 残念ながら、ネットワーク経由でコンピューターの電源を切ることはできません。電源を入れた後、ネットワークカードは呼び出し信号の発行を停止します。 さらに、さらなる創造性のための予備があります! たとえば、FPGAファームウェアをやり直して、20秒以内に8つのWOLコマンドを受信した後、USBコントローラーに電力が供給されるようにすることができます。 USBコントローラに挿入されたUSBフラッシュドライブは、仮想マシンに自動的にマウントされ、特別なログインと特別なパスワードを使用してFTPを介してマウントされます。たとえば、ハブ上のパスワード付きドキュメントを含むフォルダが使用可能になります)

結果のデバイスをシステムユニットに慎重に固定し、任務を遂行することは残っています。 注文されたボードが到着したときに何が行われます。 そして、現在のものが車の車のアラームを制御するために戻ってきます-あなたが泳ぐとき、車の中のすべてのものをロックし、タイマーを指定した時間後に開くように設定すると便利です)))

発行価格:

-ネットワークカードD-Link DGE-528T = 300r。

-火星探査機に搭乗+プログラマー(必要な場合)+ロシア郵便= 1000r + 600こする。 + 150r。

以下に、FPGAのファームウェアテキストと、概略的にインターフェイスボードを示します。 VHDLの初心者にとって、このテキストは役に立つと思います。 時間ジェネレーターを書くのは難しくありません-カウンターをCLOCKにカウントします-ここに秒があります。 ピン留めするときは、ポートF0とF1に「シュミットトリガー入力」を設定し、プルアップ抵抗をオンにすることを忘れないでください。 抵抗を備えたインターフェースボードでは、これらの入力もプルアップされますが、他の目的のために-静電気に対する保護。

---------------------------------------------------------------------------------------------------------- -- Company: House -- Engineer: AlexanderS -- -- Create Date: 13/06/2012 -- Modification Date: --/--/---- -- Module Name: manag_pc -- Project Name: - -- Version: v.1.1 -- Description: PWR , WOL -- / PWR SW ---------------------------------------------------------------------------------------------------------- library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; --use IEEE.STD_LOGIC_SIGNED.ALL; use IEEE.NUMERIC_STD.ALL; --use IEEE.MATH_REAL.ALL; --library UNISIM; --use UNISIM.VComponents.ALL; entity project is GENERIC ( ---------- ---------- CLOCK : integer := 100000000 -- , [; 1000] ); Port ( ---------- ---------- led: out std_logic_vector(7 downto 0) :=(others=>'0'); f0: in std_logic_vector(9 downto 0) :=(others=>'1'); f1: in std_logic_vector(9 downto 0) :=(others=>'1'); f2: out std_logic_vector(9 downto 0) :=(others=>'0'); ---------- ---------- CLK: in std_logic :='0' -- ( CLOCK) ); end project; architecture Behavioral of project is signal df : std_logic_vector(5 downto 0) :=(others=>'0'); signal sw_lock : std_logic :='0'; signal hl : std_logic_vector(7 downto 0) :=(others=>'0'); signal PWR_BUT1, WOL1, PWRB_on, WOL, lock : std_logic :='0'; signal PWR_BUT2, WOL2 : std_logic :='1'; signal st : integer range 3 downto 0 :=0; signal sec0125, sec025, sec05, sec, sec2, min, hour, day, res_time : std_logic :='0'; signal time_s, time_m : std_logic_vector(5 downto 0) :=(others=>'0'); signal time_h : std_logic_vector(4 downto 0) :=(others=>'0'); COMPONENT gen_time is -- GENERIC ( CLOCK : integer := 100000000 ); Port ( ---------- ---------- sec0125: out std_logic :='0'; sec025: out std_logic :='0'; sec05: out std_logic :='0'; sec2: out std_logic :='0'; sec: out std_logic :='0'; time_s : out std_logic_vector(5 downto 0) :=(others=>'0'); min: out std_logic :='0'; time_m : out std_logic_vector(5 downto 0) :=(others=>'0'); hour: out std_logic :='0'; time_h : out std_logic_vector(4 downto 0) :=(others=>'0'); day: out std_logic :='0'; ---------- ---------- RES: in std_logic :='0'; CLK: in std_logic :='0' ); end COMPONENT; begin Inst_gen_time: gen_time -- GENERIC MAP( CLOCK => 100000000 ) Port MAP ( sec0125 => sec0125, sec025 => sec025, sec05 => sec05, sec => sec, sec2 => sec2, time_s => time_s, min => min, time_m => time_m, hour => hour, time_h => time_h, day => day, RES => res_time, CLK => CLK ); res_time <= '0'; ---- BEGIN - Process(CLK) begin if (CLK'Event) and (CLK='1') then if (sw_lock = '0') then if (f0(0) = '0') or (f1(0) = '0') then sw_lock <= '1'; end if; df(0) <= not f0(0); hl(6) <= f0(0); df(1) <= not f1(0); hl(7) <= f1(0); elsif (sec0125 = '1') then sw_lock <= '0'; end if; end if; if (df(2) = '1') then f2 <= (others=>'1'); else f2 <= (others=>'0'); end if; led <= hl; end if; end process; ----- END - --- BEGIN process(CLK) begin if (CLK'event and CLK = '1') then PWR_BUT1 <= df(0); PWR_BUT2 <= not PWR_BUT1; WOL1 <= df(1); WOL2 <= not WOL1; if ((PWR_BUT1 = '1') and (PWR_BUT2 = '1')) then -- PWRB_on <= '1'; elsif ((PWR_BUT1 = '0') and (PWR_BUT2 = '0')) then -- PWRB_on <= '0'; elsif ((WOL1 = '1') and (WOL2 = '1')) then WOL <= '1'; else WOL <= '0'; end if; -- WOL if (PWRB_on = '1') and (lock = '0') then -- df(2) <= '1'; hl(0) <= not hl(0); lock <= '1'; elsif (PWRB_on = '0') and (lock = '1') then -- df(2) <= '0'; lock <= '0'; else -- WOL case st is when 0 => if (WOL = '1') then st <= st + 1; end if; -- when 1 => df(2) <= '1'; if (sec025 = '1') then st <= st + 1; end if; when 2 => if (sec025 = '1') then st <= st + 1; end if; when 3 => hl(0) <= not hl(0); df(2) <= '0'; st <= 0; when others => null; end case; end if; end if; end process; --- END end Behavioral;

FPGAを使用して、UPS制御をボードに固定することもできます。 そして、ネットワークを起動するこの義務コンピューターは、他の機器をネットワーク対応にする機能のロックをまだ解除します)

PS

ある同志は、機器メーカーからのサポートがなければ、このすべて(WOL)を実行することは非常に困難であり、それを取るなどの意味はないと言いました。 など 彼らは彼と「ちょうどそのように」と主張しました...

さて、私たちは何もできないと言ったのは誰ですか? :)