プロセッサのクロック速度が停止し、製造業者がコンピューティングの並列化の道を進んでいるという事実にすでに同意しています。 しかし、典型的な汎用プロセッサのコアの数は、マーク2と4を急速に打ち負かし、約8で止まりました。ムーアの法則を埋めようとするものさえありました。

プロセッサのクロック速度が停止し、製造業者がコンピューティングの並列化の道を進んでいるという事実にすでに同意しています。 しかし、典型的な汎用プロセッサのコアの数は、マーク2と4を急速に打ち負かし、約8で止まりました。ムーアの法則を埋めようとするものさえありました。

この停滞には客観的な理由があります。 2、4、または8コアの違いがかなり定量的である場合、すでに16コアのプロセッサは、従来のアーキテクチャの基本的な制限に直面しています。 事実、過去数十年にわたって、 バスはチップの個々のIPブロック間の通信の基盤として機能してきました。 ブロックはほとんどありませんでしたが、彼女は管理しましたが、核が増殖し始めたとき、このアーキテクチャは使い果たされました。 バスは、いくつかのプロセッサユニットが接続されている一般的なデータ伝送媒体です。 各時点で、1つのブロックがデータを送信でき、残りはすべて受信できます。 複数のブロックを同時に送信する必要がある場合、衝突が発生するため、遅延が発生します。 コアの数が8を超えると、遅延が許容できないほど大きくなり、いくつかのコアの並列動作の利点がほぼ完全に打ち消されます。

バスをブリッジで接続された複数のセグメントに分割することで、コアの数をもう少し増やすことができますが、これは「松葉杖」に似ており、うまく拡張できず、主な問題を解決しません。 1つのチップで数百のブロックを結合できる実際のソリューションは、よく知られたパケット交換ネットワーク、またはネットワークオンチップです。

バスからネットワークへの移行は非常に自然です。 これが電気通信ネットワークの開発方法です。ラジオ放送は典型的な「バス」であり、電話ネットワークはマトリックススイッチを使用してチャネルを切り替え、インターネットはパケットスイッチングです。 コンピュータ周辺機器も開発されました-最新のPCI Expressバスは、実際にはバスではなく、スタートポロジのネットワークです。 プロセッサも開発されています-最初にブロック間の直接接続、次にバスとマトリックススイッチ、そして最後にネットワーク。

バスからネットワークへの移行は非常に自然です。 これが電気通信ネットワークの開発方法です。ラジオ放送は典型的な「バス」であり、電話ネットワークはマトリックススイッチを使用してチャネルを切り替え、インターネットはパケットスイッチングです。 コンピュータ周辺機器も開発されました-最新のPCI Expressバスは、実際にはバスではなく、スタートポロジのネットワークです。 プロセッサも開発されています-最初にブロック間の直接接続、次にバスとマトリックススイッチ、そして最後にネットワーク。

NoCアーキテクチャでは、プロセッサの各コアまたはブロックは、他のブロックと通信するルーターに接続されます。 ルーター自体は、通常のコンピューターネットワークのパケットのように、データパケットが1つのブロックから別のブロックに移動するネットワークに接続されます。 これにより、マイクロ回路のトポロジが大幅に簡素化され、スケーリングの制限がなくなります。バスとは異なり、多くのブロックは互いに干渉することなく同時に通信できます。 マルチコアプロセッサのコンピューターモデリングとプロトタイプは、多数のコアを備えたこのアーキテクチャが多くの点で従来のアーキテクチャより優れていることを示しています。

当然、インターネットのロジックとプロトコルをチップに直接転送することは不合理で非効率的です。 完全に異なる技術的制限とタスクは次のとおりです。

- 非常に厳しいレイテンシと電力要件。 スイッチはナノ秒の遅延で動作し、非常に経済的でなければなりません。 ユニット間でデータを転送するエネルギーコストは、最新のチップの総消費量のかなりの部分を占めています。

- シンプルさとミニマリズム。 チップ上のスイッチは小さなスペースを占有する必要があります。つまり、複雑なロジックと大きなバッファサイズを持つことはできません。

- シリアル接続ではなく、パラレル接続。 チップ内部の物理レベルでは、単一の導体ではなく、32または64の並列チャネルでビットを順次裏切る方が有利です。

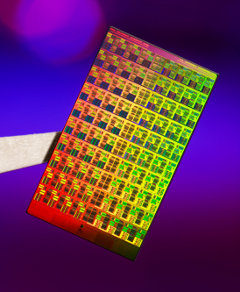

NoCの研究は、世界の大手企業や大学によって実施されています。 そのため、2007年に、Intelは80コアと1テラフロップスのパフォーマンスを備えた、わずか62ワットのエネルギー消費の実験的なプロセッサを開発しました 。 2010年には、48コアの「 シングルチップクラウドコンピューター 」が導入されました。

今年の4月に、MITの科学者グループの成果が発表され、NoC固有の最適化システム(仮想バイパスと低振幅信号)が適用されたプロトタイプの16コアプロセッサが作成されました。 これらのテクノロジーにより、帯域幅とレイテンシの理論上の限界に近づき、消費電力を大幅に削減できました。

彼らはどのように機能しますか? 通常のルーターは、受信したパケットをバッファーに保存し、ヘッダーを分析して次に送信する場所を決定します。 仮想バイパスを使用すると、ヘッダーが事前に送信され、パケット本体が到着するまでにスイッチが必要なスイッチング回線を作成するため、パケットをほぼ遅延なく転送できます。 したがって、パケットはバッファをバイパスして、ノンストップになります。 低振幅信号は、導体の電圧0と1の差を小さくすることであり、これによりエネルギー消費をさらに減らすことができました。 全体として、これらの改善により、スループットと効率が1.5倍以上向上します。

消費電力や速度などの機能の改善に加えて、NoCアーキテクチャには別の重要な利点があります。 同種のコアだけでなく、通常は単一のチップ上の任意のブロックを簡単に組み合わせることができます。 コンピュータネットワークの場合と同様に、物理層とトランスポート層は、すべてのタイプのデータとプロトコルに対して同じように機能します。 1つまたは複数のユニバーサルコンピューティングコアの代わりに、グラフィックコア、専用信号プロセッサ、デバイスのコントローラーなど、他のIPブロックを配置することができます。 また、ネットワークと同様に、チップレベルでサービス品質のサポートを実装できます。これは、リアルタイムシステムおよび仮想化システムに役立ちます。

プロセッサコアを結合するためのNoCはまだ実験的な状態ですが、NoCチップに基づくシステムで異なるブロックを結合するために、かなり長い間開発および適用されてきました。 SonicsやArterisなどの企業のソリューションは、Samsung、Qualcomm、さらにはIntelチップでも使用されています。 おそらく、近いうちに、ネットワークアーキテクチャが「神聖な」マイクロエレクトロニクスであるマルチコアセントラルプロセッサからバスに取って代わり始めるでしょう。 そして、コアの数は再び急速に増加し始めます。 したがって、ムーアの法則は早すぎて埋めることができません。

トピックに関する追加のソース: