最初に、ディスクリートロジックを使用した同様の状況を考えます。 通常、開発者が6つのNOTゲート(155LN1など)を持つチップを持っている場合、2つの要素の直列接続を遅延要素として使用します(10〜20ナノ秒)。 時々それらの間にRC回路を挿入し、10〜150 nsの遅延時間を作成できます。

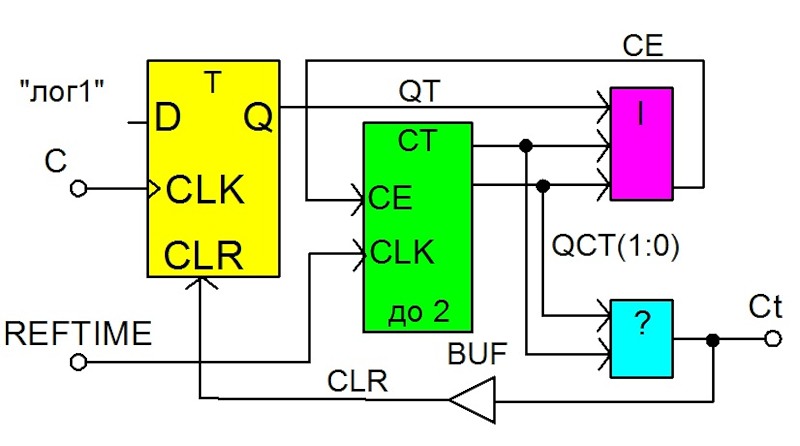

FPGAチップでは、この方法での遅延は調整できません。 それはすべてです デザイン合成機能。 合成プログラムは、二重否定を(エラーとして)不要なリンクとして認識し、排除します。 RC-回路では、FPGAが容量性負荷を許容しないため、遅延を整理することもできません。 したがって、遅延を整理するには、次の方法をお勧めします。 スケッチは次のようになります。

ct信号は同じc信号で、100 nsだけ遅延します。

基準時間信号は、特定の周波数のパルス信号であり、遅延要素で使用する必要があります。 この信号の周期は、Cに対して信号CTを遅延できる最小時間です。この場合、基準時間信号の周期は50 ns(周波数は20 MHz)です。

ここで、遅延要素の「鉄」構造に注目してください。

この構造には、わかりにくい青色の要素が1つだけあります。 実際、それは単なる組み合わせ論理の産物です。 この要素の構造を解読するのではなく、その真理値表のみを示します。

要素Tは、信号Cのエッジに沿って同期する通常のDトリガーです。要素STは、基準周波数(時間)REFTIMEのインパルスのカウンターです。 CLKクロック入力に加えて、CEイネーブル入力があります。 100 nsの遅延時間を生成するには、カウンターは2にカウントしてカウントを完了する必要があります(50 x 2 = 100)。 その後、このパラメーターはカウンターのVHDLコードで指定する必要があります。 ピンクの要素は3-ORです。 バッファBUFは、出力信号Ctと内部信号CLRを分離するために必要です。

経験豊富な開発者はこのスキームの仕組みを説明する必要はありませんが、初心者もこの記事を読んでいるので、スキームの簡単な説明をします。

20 MHzの周波数を持つ外部REFTIME信号がCTカウンターに連続的に供給されます。 トリガーTの入力「D」は、常に論理ユニットに関連付けられています。 信号エッジCトリガーが入力CLKに適用されると、最初のユニットが3-ORエレメントの入力に現れます。 この要素により、カウンタはすぐにカウントできます。 カウンタが2xにカウントされるとすぐに、Dフリップフロップが論理ゼロ状態になり、次のREFTIMEパルスとともに論理ゼロが出力に現れます。 同時に、アカウントは禁止されています。

この方式の特徴は、信号Cが100 nsだけ遅延するだけでなく、ヒープに対してもその持続時間が50 ns(つまり、基準信号の周期)に短縮されることです。 ほとんどの場合、この機能は重要ではなく、単に無視することができます。 ただし、この機能は意図的に使用してパルス幅を形成することもできます。

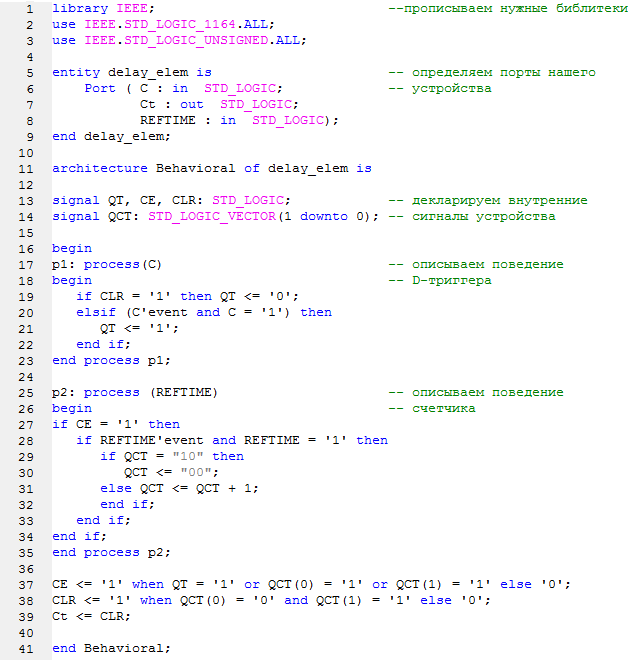

delay要素のVHDLプログラムのテキストをご紹介します。

p1というラベルのプロセスはDトリガーの動作を説明し、p2というラベルのプロセスはカウンターを説明します。