私はあなたにお知らせするという事実から最初の記事を始めます:私は記事の主題の初心者ですが、ちょうどそのようなトピックを選びました。 理由を説明します。 私はかなり以前からhabrを読んでおり、現在彼らが話していることを研究している人々からのトピックに常に興味を持っています。 そのような記事は常に理解可能であり、常に彼らの聴衆を見つけて、常に読者に著者の興味と熱意を裏切ります。これは通常、あらゆる分野の初心者にとってはスケール外れです!

私はあなたにお知らせするという事実から最初の記事を始めます:私は記事の主題の初心者ですが、ちょうどそのようなトピックを選びました。 理由を説明します。 私はかなり以前からhabrを読んでおり、現在彼らが話していることを研究している人々からのトピックに常に興味を持っています。 そのような記事は常に理解可能であり、常に彼らの聴衆を見つけて、常に読者に著者の興味と熱意を裏切ります。これは通常、あらゆる分野の初心者にとってはスケール外れです!

それで、最近、FPGAのトピックに興味を持ち、勉強中にFPGAに出会ったので、たくさんのドックを読んで、実験用のスターターキットを注文しました。 さて、郵送による実験のための訓練場を受け取り、最初の実験を完了したので、それをhabrausersと共有する準備ができました。 面白いものになることを願っています。

まず、理論を見てみましょう。FPGAの略語はこの記事のトピックで何を意味しますか? Wikiはいつでも自分で読むことができるので、自分で説明しようと思います。 誰がFPGAを知っているか、大胆にスキップしてください。

FPGA(プログラマブルロジック集積回路)は、バイナリカウンター、単純な論理回路(標準集積回路の代替-ルースパウダー)から特殊なプロセッサやニューロチップに至るまで、さまざまな複雑さのさまざまなロジックデバイスを実装するために使用される電子デバイスの一種です。

約束を理解した、質問は-どのように? FPGAの内部には、構成レコードに基づいて接続されるいくつかの基本的な要素があります。 構成レコードの可能な基本要素、タイプ、および保存場所は、FPGAのタイプと特定のモデルによって異なります。 最新のFPGAでは、CPLDとFPGAの2つのタイプが区別されます。これらは、段落に従って提供します。

CPLD(複雑なプログラマブルロジックデバイス)-FPGA。その基本要素はマクロセルと単純な論理ゲート(AND(-HE)/ OR(-HE))です。 通常、FPGAよりも少ない基本要素が含まれていますが、高速です。 また、通常、チップ上に直接不揮発性構成メモリが含まれていますが、構成サイクルの数は限られています。

FPGA(フィールドプログラマブルゲートアレイ)-FPGAは通常、多数の種類のベースブロックを持ち、これらはカスタマイズ可能なロジックエレメント(真理値表)と加算乗算ブロック(デジタル信号処理-DSP)およびPLL(位相-ロックループ)周波数の分割と乗算、およびモデルに応じた他のいくつかのループ。 通常、これらは揮発性の内部メモリと、外部の不揮発性メモリから構成をロードする機能を備えています。

これらのタイプのFPGAの定義とそれらの違いは、書籍とインターネットの両方で非常に異なることがわかります。 したがって、この違いに焦点を合わせないでください。製造業者自身が製造するFPGAを分類します。 略語を覚えていないか、いくつかの単語の意味を理解していない場合-怖くない、主なことはFPGAの一般的な概念が表示されることです、私はこれを達成したことを望みます。 そして今すぐ練習しましょう!

ツールについて議論することから始めましょう。 アルテラCyclone II FPGAスターターボードのスターターキットを使用します。これは、Cyclone IIシリーズのFPGAがインストールされた既製のボードです-EP2C20F484C7N、およびさまざまな周辺機器とインターフェース。 この記事では、LEDと7セグメントインジケーターを使用します。 このFPGAシリーズの特別なユニットは使用しません。したがって、必要に応じて、他のほぼすべてのFPGA(FPGAおよびCPLD)を使用できます。

非常に興味がある人は、開発者のキットを自分で購入するか、デバイスを自分で組み立てることができます。これは初心者にとっては非常に困難ですが、実行可能な作業です。 プログラマー回路とFPGA接続スキーム自体は簡単にグーグルで検索できます。また、以前にアマチュアAVRファームウェアに従事していた人は、それらに適したアルテラByte Blasterプログラマーを見つけることができます。 一般的に、habrayuzerの回路図実装を提供します(記事の最後に、スターターボードの図を示します)。 お金をかけずに試して仕事の結果を確認したい人は、Quartus IIに組み込まれたシミュレータを使用できます(この記事では、その操作方法については説明しません)。

ソフトウェアから、Quartus IIを使用します。QuartusIIは、製造元のWebサイト(Altera)で、WindowsとLinuxの両方のバージョンで入手できます。

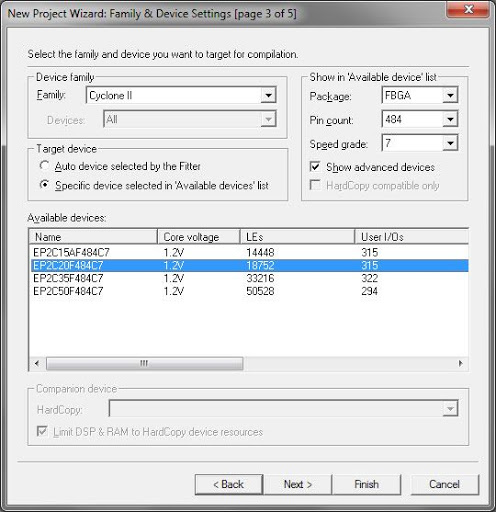

そして今、私たちは練習に近づいています! CAD Quartus IIを起動し、プロジェクトを作成します。 ウィザードの最初のステップでは、プロジェクトの名前とその場所を示してから、ファイルを追加するステップをスキップします(まだ時間があります)。 デバイスを選択する段階でプロジェクトの作成を終了します。鉄片で行う場合は、FPGAの名前を正確に知っているので選択します。 FPGAのプロジェクトを作成するだけであれば、たとえば3番目のサイクロンなど、より強力なものを選択します。 スターターキットにインストールされているFPGAを選択します。

[完了]をクリックします-プロジェクトが作成されます。 Quartusのプロジェクト構造は階層的であるため、階層の最上位(最上位エンティティ)を選択する必要があります。 回路ファイルや、HDL(ハードウェア記述言語-ハードウェア記述言語)のいずれかのロジックの記述を含むファイルの設計に使用できます。 私の意見では、メインロジックブロックを階層の最上位に持つ回路図ファイルを使用し、HDLにブロック自体を実装します。 意見は異なる場合がありますが、選択中に多くのホリバーニーのトピックを読んでいますが、これまでのところそのようなモデルに焦点を当てて、あなたは選択することができます。 プロジェクト言語のHDLとして、VHDL((超高速集積回路)ハードウェア記述言語)を選択しました。VerilogやAHDLなど、他の任意のものを使用できますが、これはすべて好みによって異なります。

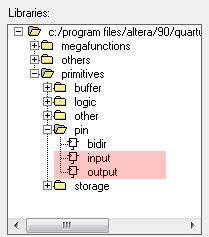

最初のプロジェクトファイル(File-New ..)を作成し、Block Diagram / Schematic Fileを選択します。 次に、最も単純な回路を描いて、1つの入力と1つの出力を追加して接続します(実際のFPGAでは、この回路は信号を1つのレッグから別のレッグに送信します)。 これを行うには、ダイアグラム内の空の場所をダブルクリックし、開いた[シンボル]ダイアログボックスで必要な要素を選択します。

このように、線で接続します。 ピンに名前を付けて(要素をダブルクリック)、CLOCK_27 [0]を呼び出す入力、LEDR [0]を出力します。 名前は偶然に選択されませんでした-次に、CLOCK_27 [0]を27Mhzジェネレータの入力に関連付け、LEDR [0]をゼロの赤色LEDに関連付けます。 プロジェクトに追加するためのチェックマークを残して、ファイルを保存します。 次に、結果のファイルをプロジェクト階層の最上部に設定します。 そのためには、プロジェクトナビゲータウィンドウの[ファイル]タブで、ファイルのコンテキストメニューから[最上位エンティティとして設定]を選択します。 こんにちは、世界は準備ができています。 Info:Quartus II Full Compilationが成功した場合、プロジェクトをコンパイルします(Processing-Start Compilation)。 -喜んで、最初の段階が完了したと信じます。

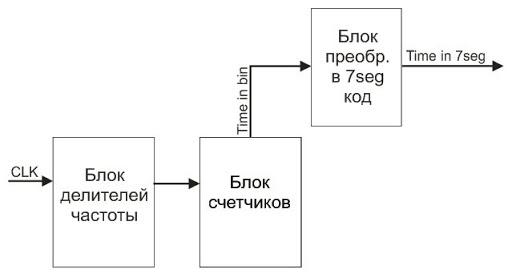

では、目標を考えてみましょう。 デバイスは、電源を入れると分と時間のカウントダウンを開始します。 したがって、4つの7セグメントインジケータ「HH:MM」が必要です。 時間をカウントするには、多少正確な1Hz信号が必要です。 周波数を27Mhzで除算して取得し、60(秒)、60(分)、24(時間)の順にカウントします。 最後の2ブロックから、分と時間の2進数はBin-> BCD(2進化10進数)-> 7segデコーダーに移動します。 ここで、一般的に、デバイス全体です。 簡単かつ明快にするために、回路が非同期になるようにすぐに予約してください(分は秒から始まり、時間は分から始まります)。

それでは、最初のブロックである周波数分割ブロックを作成しましょう。 既にわかっているように、新しいファイルを作成します。ファイルタイプのみがVHDLファイルになります。 コードを挿入します:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity Div_27Mhz_to_1Hz is

port( clk:in std_logic; clk_out:out std_logic);

end Div_27Mhz_to_1Hz;

architecture div_behavior of Div_27Mhz_to_1Hz is

begin

process(clk)

variable cnt : integer range 0 to 27000000;

begin

if(clk'event and clk = '1')

then

if(cnt >= 13500000)

then

clk_out <= '1';

else

clk_out <= '0';

end if;

if(cnt = 27000000)

then

cnt := 0;

else

cnt := cnt + 1;

end if;

end if;

end process;

end div_behavior;

ユーティリティディレクティブはスキップします(マニュアルの最後にあるリンクで確認できます)。作業のロジックにのみ注意を払います。 最初に、エンティティ、つまり ブロック自体。 入力と出力、それらのタイプと名前を示します。 共通のタイプstd_logicはビットを意味します。 次に、このユニットの内部アーキテクチャについて説明します。 アーキテクチャは並列プロセスで構成されています。 各プロセスには独自の感度リストがあります。たとえば、上記の例の唯一のプロセスは、clk入力での変更に敏感です。 変数はプロセスに対して宣言することができ、この例では0から27000000型の整数範囲です。次に、要素のロジックがプロセス本体に設定されます:期間の半分が経過するまで、出力に論理ゼロを入れます。 27000000に達したらカウンターをリセットします。完璧なコードのふりをするわけではありません。勉強している間、訂正してくれてうれしいです:)

ファイルをコードとともに保存し、シンボルを作成します(ファイル-作成/更新-現在のファイルのシンボルファイルを作成)。これは、このブロックをメインスキームに挿入するために必要です。 キャラクター挿入ダイアログのプロジェクトフォルダーでキャラクターを見つけることができます。 次に、残りのブロックについて詳しく説明しません。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

-- For CONV_STD_LOGIC_VECTOR:

use ieee.std_logic_arith.all;

entity cnt_0_to_59 is

port( clk:in std_logic; c59:out std_logic; vector:out std_logic_vector(5 downto 0));

end cnt_0_to_59;

architecture cnt_behavior of cnt_0_to_59 is

begin

process(clk)

variable cnt : integer range 0 to 59;

begin

if(clk'event and clk = '1')

then

if(cnt = 59)

then

cnt := 0;

c59 <= '1';

vector <= CONV_STD_LOGIC_VECTOR(cnt, 6);

else

cnt := cnt + 1;

c59 <= '0';

vector <= CONV_STD_LOGIC_VECTOR(cnt, 6);

end if;

end if;

end process;

end cnt_behavior;

これは、0から59までのカウントブロックであり、これを使用して分と秒をカウントします。 ここの新製品のうち、出力タイプは、ビットのグループ(ビットベクトル)を決定するstd_logic_vector(5 downto 0)と、変数を指定された長さのビットベクトルに変換する関数CONV_STD_LOGIC_VECTOR(cnt、6)です。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

-- For CONV_STD_LOGIC_VECTOR:

use ieee.std_logic_arith.all;

entity cnt_0_to_23 is

port( clk:in std_logic; vector:out std_logic_vector(4 downto 0));

end cnt_0_to_23;

architecture cnt_behavior of cnt_0_to_23 is

begin

process(clk)

variable cnt : integer range 0 to 23;

begin

if(clk'event and clk = '1')

then

if(cnt = 23)

then

cnt := 0;

vector <= CONV_STD_LOGIC_VECTOR(cnt, 5);

else

cnt := cnt + 1;

vector <= CONV_STD_LOGIC_VECTOR(cnt, 5);

end if;

end if;

end process;

end cnt_behavior;

高い時間カウンター。 新しいものはありません。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

-- For CONV_STD_LOGIC_VECTOR:

use ieee.std_logic_arith.all;

entity bin2bcd_5bit is

port( bin:in std_logic_vector(4 downto 0);

bcd1:out std_logic_vector(3 downto 0);

bcd10:out std_logic_vector(3 downto 0)

);

end bin2bcd_5bit;

architecture converter_behavior of bin2bcd_5bit is

begin

process(bin)

variable i : integer range 0 to 23;

variable i1 : integer range 0 to 9;

begin

i := conv_integer(bin);

i1 := i / 10;

bcd10 <= CONV_STD_LOGIC_VECTOR(i1, 4);

i1 := i rem 10;

bcd1 <= CONV_STD_LOGIC_VECTOR(i1, 4);

end process;

end converter_behavior;

Binary to BCD Converterは、基本的に1つの2進数を2つに分割し、それぞれが小数点以下を表します。 新製品の-rem演算子、部門の残りの部分。 6ビット用のコンバーターは同じ方法で記述されていますが、これは提供しません。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity BCD_to_7seg is

port(

BCD:in std_logic_vector(3 downto 0);

seg:out std_logic_vector(6 downto 0)

);

end BCD_to_7seg;

architecture conv_behavior of BCD_to_7seg is

begin

process(BCD)

begin

if BCD = "0000" then seg <= "0000001";--0

elsif BCD = "0001" then seg <= "1001111";--1

elsif BCD = "0010" then seg <= "0010010";--2

elsif BCD = "0011" then seg <= "0000110";--3

elsif BCD = "0100" then seg <= "1001100";--4

elsif BCD = "0101" then seg <= "0100100";--5

elsif BCD = "0110" then seg <= "0100000";--6

elsif BCD = "0111" then seg <= "0001111";--7

elsif BCD = "1000" then seg <= "0000000";--8

elsif BCD = "1001" then seg <= "0000100";--9

else seg <= "1001001";--err

end if;

end process;

end conv_behavior;

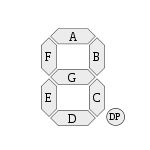

単純な真理値表によって実装される7セグメントコードへの1ビットのコンバーター。 7セグメントのコード自体は、abcdefgの順序でインディケーターの書き込みセグメントをビット表現したもので、私の場合も逆です。

そこで、すべてのブロックを実現しました。それらを接続することは残っています。 Mainスキームと、bin2segシンボルのデコードを行います。これは、スペースを節約するスキームとしても実装されています。

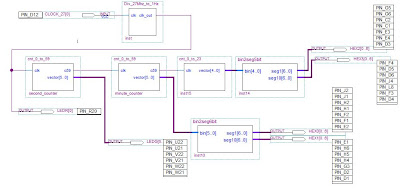

主回路:

(クリックしてクリック)

(図でわかるように、わかりやすくするために、緑色のLEDに秒数を表示しました)

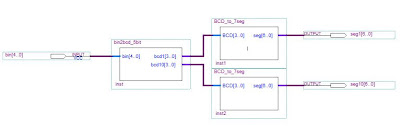

bin2seg:

(クリックしてクリック)

プロジェクトの準備ができたら、コンパイルしてテストできます。 私は四分の一で回路の動作をモデル化することについて話したかったのですが、何かが起こったので、興味があります-私は次の記事で書きます。 最後のステップは、仮想入力/出力を実際のFPGAレッグに関連付けることです。

関連付けは、[割り当て]-[ピン]メニューでコンパイル後に実行できます。 表示されるウィンドウに、チップ上のピンレイアウトが表示され、その下にプロジェクトピンのリストが表示されます。 Locationフィールドを変更することにより、内部入力を実際のレッグにマッピングします。 私の場合、ボードのレイアウトに応じてピン名を確認します。開発の場合、ピン名がわかります。 最後のステップはファームウェアです。ツール-プログラマーメニューのスタートボタンで実行します(プログラマーを接続し、ドライバーをインストールする必要があります)。

まあ、すべての並べ替え。 結論として、このトピックに対する公共の関心がある場合、私は確かにより多くの記事を書くと言いたいと思います。 たとえば、設定と目覚まし時計などを使ってこのプロジェクトを通常の時間に完了する方法は、すでに計画しています:)

約束のリンク:

www.altera.com-あらゆる種類の製品ドキュメントと広告

www.bsuir.by/vhdl/reference-VHDLリファレンス

altera.ru-アルテラの会社の代表者、私はそこにスターターキットを注文しました

+ J.R. Armstrong Modeling digital systems by VHDLの本を使用しました。

自分で組み立てる人のために、ボードの回路を取り付けます。 ( 品質 )

また、ボーナス-タイマープロジェクト( kach-kach )