まず、素晴らしいドキュメントAN82156 Designing PSoC Creator Components with UDB Datapathsをお勧めします。 その中に、典型的なソリューションといくつかの標準プロジェクトがあります。 さらに、ドキュメントの冒頭で開発はUDBエディターを使用して実行され、最後に向かって、データパス構成ツールを使用して実行されます。つまり、ドキュメントは開発のすべての側面をカバーします。 しかし、残念ながら、単一のPSoCチップの価格を見ると、このドキュメントで説明されている問題しか解決できない場合、コントローラーは非常に過大評価されていると言えます。 PWMと標準シリアルポートは、PSoCなしで実行できます。 幸いなことに、PSoCタスクの範囲ははるかに広いです。 したがって、AN82156を読み終えたら、他のインスピレーションの源を探し始めます。

次に役立つソースは、PSoC Creatorに付属のサンプルです。 私はすでに、会社文書の翻訳の一部の1つへのメモでそれらを参照しています( こちらをご覧ください )。 これらはおおよそここに保存されます(ディスクは異なる場合があります):

E:\ Program Files(x86)\ Cypress \ PSoC Creator \ 4.2 \ PSoC Creator \ psoc \ content \ CyComponentLibrary。

* .vファイル、つまり、Verilogテキスト、または* .vhdを探す必要があります。これは、VHDL言語の構文を説明するためにもう少し必要なためです。 問題は、これらは例ではなく、既成のソリューションであるということです。 これは素晴らしく、完全にデバッグされていますが、単純なプログラマーはサイプレスのプログラマーとは異なる目標を持っています。 私たちの仕事は、短時間で補助的なことをすることです。その後、私たちのプロジェクトでそれを使い始め、ほとんどの時間を費やします。 今日私たちに割り当てられたタスクを理想的に解決する必要があり、明日はすべてがわずかに異なる別のプロジェクトに同じコードを挿入したい場合、明日はその状況でそれを終了します。 サイプレス開発者にとって、コンポーネントは最終製品であるため、ほとんどの時間を費やすことができます。 そして、それらはすべてすべてを提供しなければなりません。 ですから、これらのテキストを見たとき、私は悲しく感じました。 最初の開発のインスピレーションを引き出す場所を探し始めたばかりの人には、あまりにも複雑です。 しかし、参考書として、これらのテキストは非常に適しています。 あなた自身のものを作成するときに必要な多くの貴重なデザインがあります。

また、非常に興味深いコーナーがあります。 例えば、今、私は「バターオイル」のスタイルで、モデリングのためのモデルがあります(昔、厳しい教師は「モデリング」以外の方法でシミュレーションを翻訳することを私に思いとどまらせました)。 それらはカタログにあります。

E:\ Program Files(x86)\ Cypress \ PSoC Creator \ 4.2 \ PSoC Creator \ warp \ lib \ sim

Verilogプログラマにとって最も興味深いディレクトリは次のとおりです。

E:\ Program Files(x86)\ Cypress \ PSoC Creator \ 4.2 \ PSoC Creator \ warp \ lib \ sim \ presynth \ vlg

ドキュメント内のコンポーネントの説明は適切です。 ただし、ここではすべての標準コンポーネントの動作モデルについて説明します。 これは、ドキュメントよりも優れている場合があります(重い言語で書かれており、いくつかの重要な詳細が省略されています)。 このコンポーネントまたはそのコンポーネントの動作が明確でない場合は、このディレクトリのファイルを表示して、コンポーネントを正確に理解してみる価値があります。 最初はGoogleで検索しようとしましたが、見つかったフォーラムで出会ったのは推論だけで、詳細はありませんでした。 詳細は次のとおりです。

それにもかかわらず、参考書は素晴らしいですが、どこで教科書を探すべきか、何から学ぶべきですか? 正直なところ、特別なことは何もありません。 一般に、UDB Editorの既製の良い例はほとんどありません。 突然、RGB LEDをプレイすることに決めたとき、UDB Editorの下で美しい例を見つけました(サイクル全体を開始した記事で書きました)。 ただし、検索エンジンで多くの作業を行う場合は、Datapath Config Toolの例がまだあります。そのため、このツールの使用方法を全員が理解できるように、 前の記事を作成しました 。 そして、多くの例が集められている素晴らしいページがここにあります 。

このページには、サードパーティの開発者による開発がサイプレスによって検証されています。 つまり、まさに必要なものです。私たちはサードパーティの開発者でもありますが、正確に検証されたものから学びたいのです。 このページを見つけた例-平方根ハードウェア計算機を見てみましょう。 エンドユーザーはそれを信号処理パスに含め、回路にコンポーネントを投げます。 この例では、同様のコードを分析するためのトレーニングを行います。そうすれば、誰もが自分の水泳を始めることができます。 そのため、必要なサンプルはリンクからダウンロードできます。

調べます。 例があり(誰もが個別に検討します)、\ CJCU_SquareRoot \ Library \ CJCU_SquareRoot.cylibディレクトリにライブラリがあります。

タイプ(整数または固定小数点)およびビットごとに解決策があります。 これに注意する必要があります。 UDBエディターで開発する場合の汎用性は優れていますが、データパス編集ツールを使用して開発する場合、ご覧のとおり、人々はこのように苦しめられます。 あなたが普遍的にそれを行うことができない場合(しかし、それがうまくいく場合)怖がらないでください。

トップレベル(回路)で、私はやめません。PSoCでは動作せず、UDBで動作することを研究しています。 中程度の複雑さのオプション-16ビットですが整数を見てみましょう。 これは、ディレクトリCJCU_B_Isqrt16_v1_0にあります。

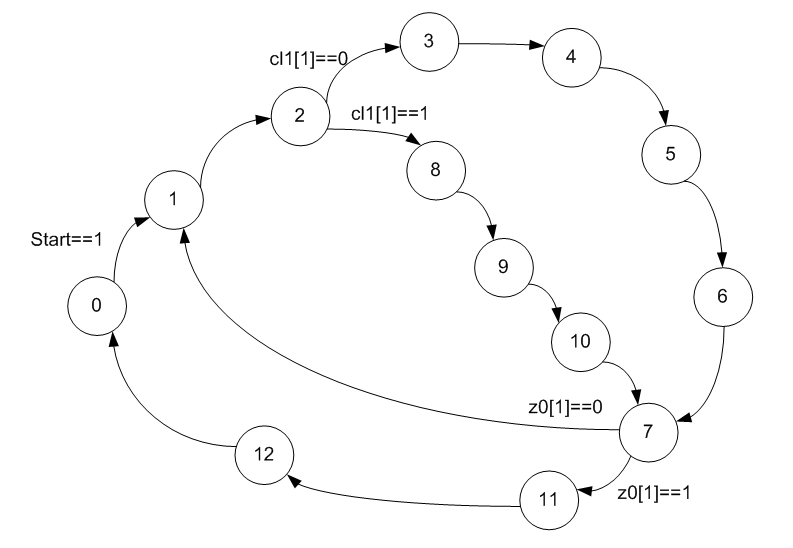

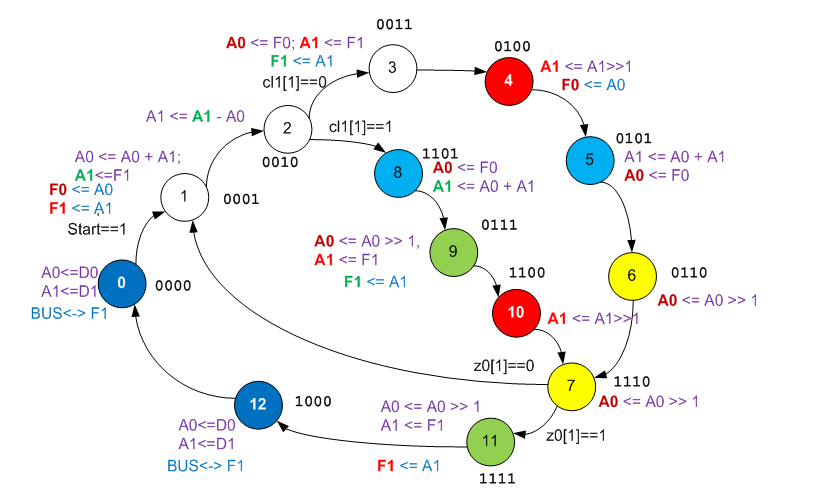

最初に行うことは、ファームウェアの遷移グラフを拡張することです。 Googleにはいくつかの根本的に異なるアルゴリズムの選択肢が用意されているため、これがないと、どのような平方根アルゴリズムが適用されているか推測することさえできません。

これまでのところ、何も明確ではありませんが、予測可能です。 さらに情報を追加する必要があります。 状態のコーディングを見ます。 通常のインクリメンタルバイナリコードでエンコードされていないことは印象的です。

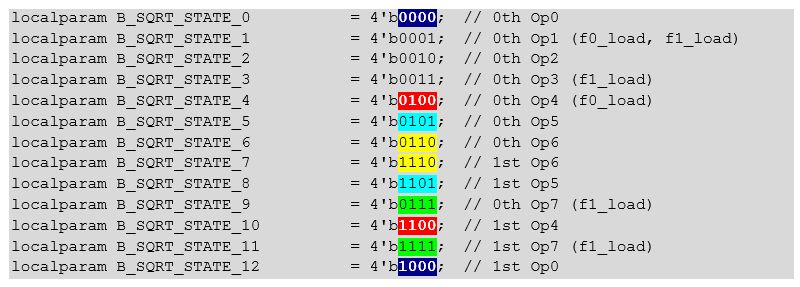

私はすでにこのアプローチを記事で言及しましたが、特定の例で使用することはできませんでした。 RAM動的構成ALUには3つのアドレス入力しかありません。 つまり、ALUは8つの操作のいずれかを実行できます。 オートマトンにさらに状態がある場合、「各状態に独自の操作がある」というルールは不可能になります。 したがって、ALUの操作が同一である状態が選択され、動的構成のRAMアドレス(通常は下位)に3ビットが供給され、同じ方法でエンコードされ、残りは異なる方法でエンコードされます。 このようなソリティアを追加する方法は、すでに開発者の問題です。 調査したコードの開発者は、上記のとおり正確に折りたたまれています。

この情報をグラフに追加し、ALUで同じ機能を実行する状態を同様の色で色付けします。

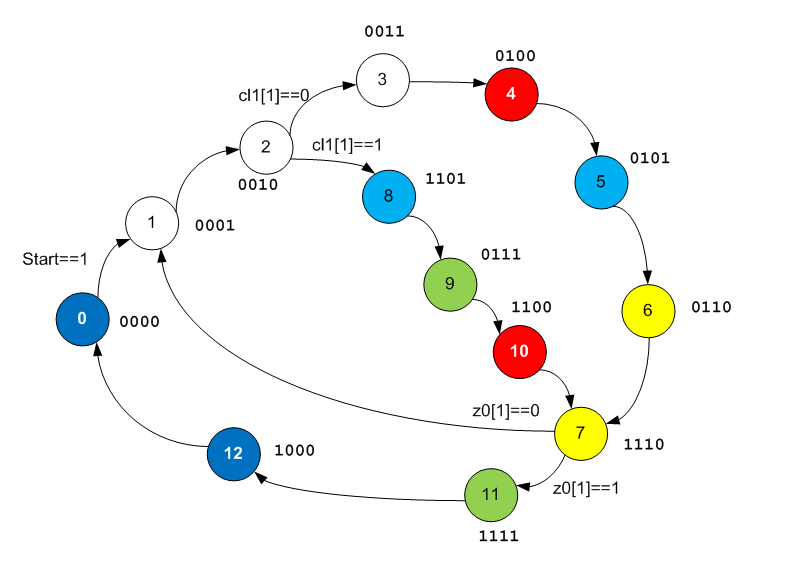

パターンはまだ現れていませんが、グラフを明らかにし続けています。 Datapath Edit Toolを開き、その中のロジックを既に調べています。

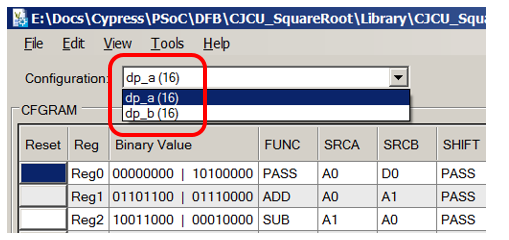

2つのDatapathブロックがチェーンで接続されていることに注意してください。 独自の操作を行う場合、これも必要になる場合があります(ただし、データパス編集ツールは既にチェーンで結合されたブロックを作成できるため、これは怖くないです)。

ALUに対応するグラフを読み取る(および記入する)ときは、常に次の図のドキュメントを開きます。

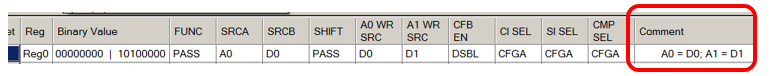

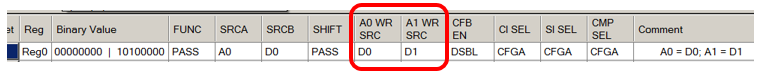

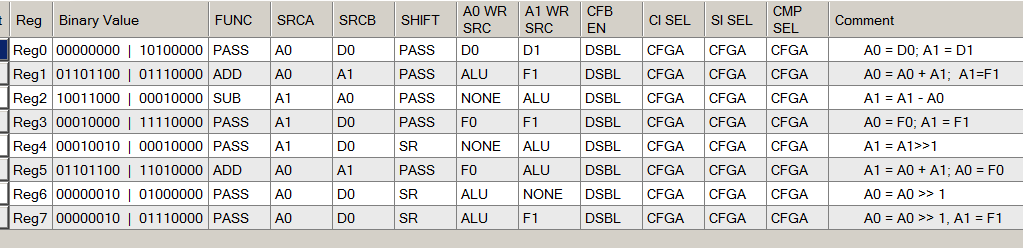

確かに、この例の開発者は私たちの面倒を見て、コメント欄に記入しました。 これを使用して、何が構成されているかを理解できます。 同時に、コメントを書くことは、コードに同行する人にとっても、6か月後にそれを忘れるときも、私たちにとって常に役立つことに留意しています。

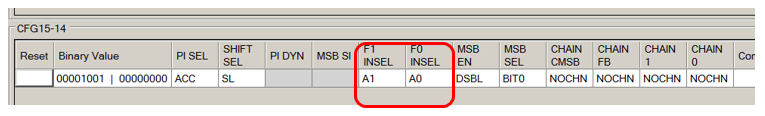

状態0および12に対応するX000コードを確認します。

解説から、そこで何が起こっているかはすでに明らかです(レジスタD0の内容はレジスタA0にコピーされ、D1の内容はレジスタA1にコピーされます。これを知って、将来の直感を訓練し、設定フィールドで同様のエントリを見つけます:

ALUはPASSモードで動作し、シフトレジスタもPASSであるため、他のアクションが実際に実行されないことがわかります。

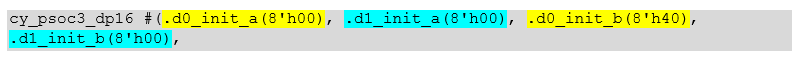

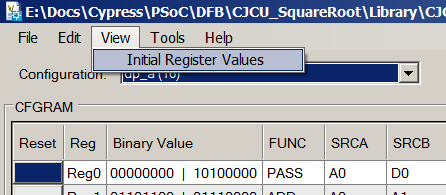

途中で、Verilogのテキストを見て、レジスタD0とD1の値が等しい場所を確認します。

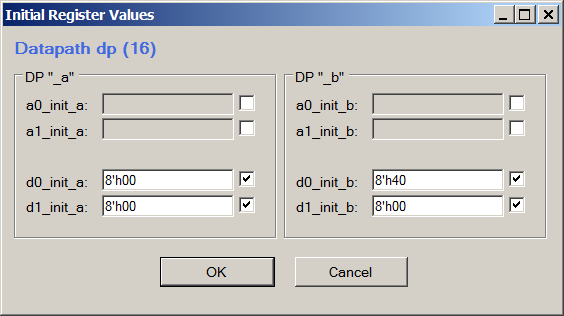

必要に応じて、[表示]-> [初期レジスタ値]を選択して、データパス構成ツールで同じことを確認できます。

表示するには、Verilogコードを直接分析し、独自のバージョンを作成する方が便利です。構文を考慮しないようにエディターで作業してください。

同様に、他のすべてのALU関数を解析します(最初にコメントを見てください)。

新しい知識を考慮して、オートマトンの遷移グラフを再作成します。

すでに何かが迫っていますが、これまでのところ、このグラフでGoogleが見つけたアルゴリズムを自信を持って言えません。 むしろ、自分ではないと自信を持って言える人もいますが、信じられないほどの人でさえ、彼らだと自信を持って答えることはできません。 レジスタFIFO F0およびF1のアクティブな使用を混乱させます。 一般的にファイル内

\ CJCU_SquareRoot \ Library \ CJCU_SquareRoot.cylib \ CJCU_Isqrt_v1_0 \ API \ CJCU_Isqrt.c

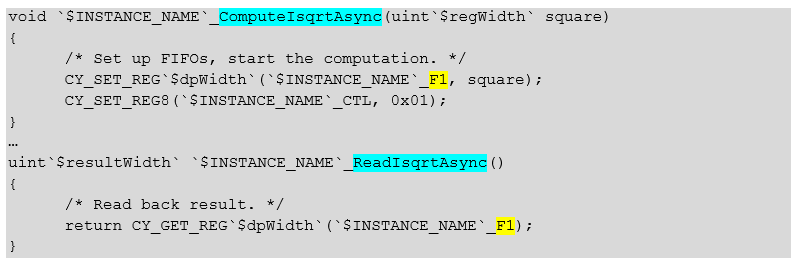

F1を使用して引数を渡し、結果を返すことがわかります。

同じテキスト:

void `$INSTANCE_NAME`_ComputeIsqrtAsync(uint`$regWidth` square) { /* Set up FIFOs, start the computation. */ CY_SET_REG`$dpWidth`(`$INSTANCE_NAME`_F1, square); CY_SET_REG8(`$INSTANCE_NAME`_CTL, 0x01); } … uint`$resultWidth` `$INSTANCE_NAME`_ReadIsqrtAsync() { /* Read back result. */ return CY_GET_REG`$dpWidth`(`$INSTANCE_NAME`_F1); }

しかし、1つの引数と1つの結果。 そして、なぜ作業中にFIFOへの呼び出しが非常に多いのですか? そして、FIFO0はそれと何の関係がありますか? 私をバラバラに切りましたが、著者はドキュメントの翻訳に見られるモードを利用したようです。本格的なFIFOの代わりに、このブロックは単一のレジスタとして機能しました。 著者がレジスタセットを拡張することに決めたとします。 もしそうなら、彼らの方法論は私たちの実際の仕事で私たちに役立つでしょう、詳細を勉強しましょう。 実際、ドキュメントでは、FIFOを操作するさまざまなアプローチについて説明しています。 できる-そう、できる-そう、でもできる-ある種の。 そして、詳細はありません。 繰り返しますが、外国のベストプラクティスについて学ぶ機会があります。 著者はFIFOで何をしますか?

まず、これらは信号の割り当てです。

wire f0_load = (state == B_SQRT_STATE_1 || state == B_SQRT_STATE_4); wire f1_load = (state == B_SQRT_STATE_1 || state == B_SQRT_STATE_3 || state == B_SQRT_STATE_9 || state == B_SQRT_STATE_11); wire fifo_dyn = (state == B_SQRT_STATE_0 || state == B_SQRT_STATE_12);

次に、Datapathへの接続を次に示します。

/* input */ .f0_load(f0_load), /* input */ .f1_load(f1_load), /* input */ .d0_load(1'b0), /* input */ .d1_load(fifo_dyn),

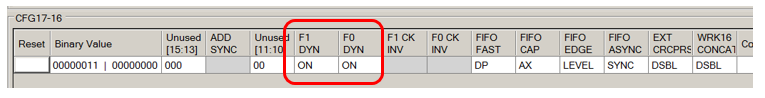

コントローラーの説明から、このすべてが何を意味するかは特に明確ではありません。 しかし、アプリケーションノートから、この設定がすべての原因であることがわかりました。

ところで、まさにこの設定のため、このブロックはUDBエディターを使用して記述できません。 これらの制御ビットがONの場合、FIFOは異なるソースとレシーバーで動作できます。 Dx_LOADが1に等しい場合、 Fxはシステムバスと交換し、ゼロの場合、ここで選択されたレジスタと交換します。

F0は常にレジスタA0と、状態12および0のF1と-システムバスと(結果をアップロードして引数をロードするために)、他の状態と-A1と常に交換することがわかります。

さらに、Verilogコードから、F0ではデータが状態1および4でロードされ、F1では状態1、3、9、11でロードされることがわかりました。

取得した知識をグラフに追加します。 一連の操作中の混乱を避けるために、割り当てマーク「a la UDB Editor」をVerilogovの矢印に置き換えて、ソースがブロックに入る前の信号の値であることを強調します。

アルゴリズムの分析の観点からは、すべてがすでに明確になっています。 そのようなアルゴリズムの修正を次に示します。

uint32_t SquareRoot(uint32_t a_nInput) { uint32_t op = a_nInput; uint32_t res = 0; uint32_t one = 1uL << 30; // The second-to-top bit is set: use 1u << 14 for uint16_t type; use 1uL<<30 for uint32_t type // "one" starts at the highest power of four <= than the argument. while (one > op) { one >>= 2; } while (one != 0) { if (op >= res + one) { op -= res + one; res += one << 1; } res >>= 1; one >>= 2; } return res; }

システムとの関係でのみ、次のようになります。

uint32_t SquareRoot(uint32_t a_nInput) { uint32_t op = a_nInput; uint32_t res = 0; uint32_t one = 1uL << 14; // The second-to-top bit is set while (one != 0) { if (op >= res + one) { op -= res + one; res += one << 1; } res >>= 1; one >>= 2; } return res; }

状態4および10は、文字列を明示的にエンコードします。

res >>= 1;

さまざまな支店向け。

行は次のとおりです。

one >>= 2;

状態6と7のペア、または状態9と7のペアのいずれかによって明示的にエンコードされています。および回避策)。

状態2は条件分岐をエンコードします。 状態7はループステートメントをエンコードします。 ステップ2の比較操作は非常に高価です。 一般に、多くの場合、レジスタA0には変数1が含まれています。 しかし、ステップ1で変数oneがF0にアンロードされ、代わりに値res + oneがロードされます。その後、ステップ2で比較のために減算が実行され、ステップ3および8で1の値が復元されます。 ステップ4で、A0が再びF0にコピーされるのはなぜかわかりませんでした。 おそらくこれはある種の初歩です。

誰がresで誰がopであるかを把握することは残っています。 条件がopと合計res + 1を比較することを知っています。 状態1では、A0( one )とA1が合計されます。 A1はresです。 状態11では、A1もresであり、関数の出力に供給されるF1に入るのは彼です。 状態1のF1は明らかにopです。 変数の

実際、全体の真実が明らかにされています。 比較と計算のためにA1が一時的にF1で一時的にどのように変化するか、比較(実際にはビットCを生成)と式への参加の両方に同じ差がどのように使用されるかを確認します。 Cアルゴリズムの空のスペース(バイパス)がオートマトンの遷移グラフの長いブランチによってエンコードされる理由さえわかります(このブランチでは、レジスタはメインコードブランチで発生する交換と同じように交換されます)。 すべてが見えます。

私を苦しめることのない唯一の質問は、著者がどのようにFIFOをシングルバイトモードに切り替えたのですか? ドキュメントには、このために補助制御レジスタのCLRビットをユニットに上げる必要があると書かれていますが、APIに同様のエントリがあることはわかりません。 おそらく誰かがこれを理解し、コメントを書くでしょう。

さて、そして独自の何かを開発する-取得したスキルを使用して、逆の順序で。

おわりに

UDBに基づいて「ファームウェア」を開発するスキルを開発するには、ドキュメントを読むだけでなく、他の人のデザインからインスピレーションを引き出すことも役立ちます。 PSoC Creatorに付属するコードはリファレンスとして役立ち、コンパイラーが提供するビヘイビアーモデルは、ドキュメントの意味をよりよく理解するのに役立ちます。 この記事では、サードパーティのメーカーのサンプルセットへのリンクも提供し、そのようなサンプルの1つを解析するプロセスを示しています。

これについては、UDBでの作業に関する著作権の記事のサイクルは完了したと見なすことができます。 彼が誰かが実際に役立つ知識を得るのを手伝ってくれたら嬉しいです。 まだドキュメントの翻訳がいくつかありますが、統計ではほとんど誰も読んでいないことが示されています。 トピックを簡単に説明するために、それらはきれいに計画されています。