これらすべての質問に対する答えを知りたいなら、猫へようこそ。 以前の記事の読者のリクエストに応じて、私はあなたに警告します:30分の間、たくさんのテキストがあります。

開始する

1947年から1948年の間に、ベル研究所のウィリアム・ショックリー率いるジョン・バーディンとウォルター・ブラッテンは、ゲルマニウムダイオードの電界分布を研究し、偶然トランジスタ効果を発見しました。 そして、発見の潜在的な有用性は明白に見えましたが(しかし、都市の伝説では、軍事専門家が実際の使用を発見しなかった後に発見が機密解除されたと言います)、最初のトランジスタは次のように見えました:

図2.最初のトランジスタのレプリカ

工業生産に適したデバイスにあまり似ていませんか? 気相点バイポーラトランジスタをpn接合から製造するのにより便利にするのに2年かかり、その後、大量電子機器の電子管の日数(数日ではなく数年)がカウントされました。

トランジスタの3つの先駆者のうち、ショックリーだけが彼らに取り組んでいたことは事実です。彼は元の仕事とはほとんど関係がありませんでした(彼は理論家であり、研究者ではなく上司だったため)が、彼はすべての名声を引き継いだので、バーディンとandしました彼らはマイクロエレクトロニクスを二度と扱ったことはありません。 Brattainは電気化学、およびBardin-超伝導性を研究し、2回目のノーベル賞を受賞し、物理学で2つの賞を受賞した歴史上唯一の人物になりました。

Shockleyは、野心を持って研究チームを解散させることに成功し、Bell Labsを去り、独自のShockley Semiconductor Laboratoryを設立しました。 しかし、その中の労働環境も望まれていなかったため、ショックリーから逃れ、フェアチャイルドセミコンダクターを設立した有名な「反逆者の8人」が出現しました。フェアチャイルドセミコンダクターは、現在「シリコンバレー」として知られるものの親になりました- Intel、AMD、Intersilなどの企業が含まれます。

図3.フェアチャイルドレン-フェアチャイルドが設立した企業

ショックリー自身はG8の裏切りから決して回復せず、下り坂に転がりました。彼は自分の会社から解雇され、人種差別と優生学に連れ去られ、科学界の追放者となり、すべて忘れ去られました。 彼の子供でさえ新聞から死について学びました。

開始する前に

トランジスタの発見の歴史は広く知られており、多くの記述があります。 トランジスタの最初の特許出願が1947年にはまったく行われていなかったが、2025年前の1925年にオーストリアハンガリー出身のアメリカ人であるJulius Lilienfeldによって出願されたことはあまり知られていません。 この場合、1947年のバイポーラトランジスタとは異なり、Lilienfeldの特許に記載されているデバイスはフィールドでした.1930年に受信した特許では、金属シャッター付きMESFET、および1933年の特許-MOSFET、私たちが知っているものとほぼ同じです今。 Lilienfeldは、ゲート誘電体としてゲートアルミニウムとアルミナを使用することを意図していました。

残念ながら、当時のレベルの技術開発では、リリエンフェルドがプロトタイプでアイデアを実現することはできませんでしたが、1948年にショックリーが実施した実験(すでに単独で)は、リリエンフェルドの特許が基本的に操作可能なデバイスを説明していることを示しました。 実際に、バイポーラトランジスタのランダムな発明につながったダイオードの特性に関するショックレーグループのすべての作業は、真空管にはるかに類似した特性を持ち、したがって当時の物理学者にとってより理解しやすい電界効果トランジスタの作成に関する研究の一部でした。 それにもかかわらず、Lilienfeldのアイデアの実行可能性が成功裏に確認されたにもかかわらず、1948年には欠陥のない誘電体薄膜の安定した生産のための技術はまだありませんでしたが、バイポーラトランジスタはより技術的に進歩し、商業的に有望であることが判明しました。 MOSFETは棚に置かれ、バイポーラデバイスは惑星の周りで勝利の行列を始めました。

用語の瞬間

バイポーラトランジスタまたはバイポーラトランジスタは、電子と正孔の両方の両方のタイプの電荷キャリアが動作するために必要なトランジスタであり、ベース電流によって制御されます(トランジスタのゲインで乗算します)。 通常、pn接合またはヘテロ接合を使用して行われますが、最初のトランジスタはバイポーラですが、接合トランジスタではありませんでした。 人気のある英語の頭字語は、BJT、バイポーラ接合トランジスタです。

ヘテロ接合のトランジスタ(ヒ化ガリウムとアルミ化ガリウムなどの異なる材料間の遷移)には、頭字語HBT(ヘテロ接合バイポーラトランジスタ)が使用されます。

電界効果トランジスタまたは電界効果トランジスタとしても知られるユニポーラまたは電界効果トランジスタは、その動作が電界効果に基づいており、1種類の電荷キャリアのみを必要とするトランジスタです。 電界効果トランジスタには、ゲートに印加される電圧によって制御されるチャネルがあります。 電界効果トランジスタには、かなりの種類があります。

通常のMOSFETまたはMOSFETは、誘電体(通常は酸化物)によってチャネルから絶縁されたゲートを備えたトランジスタであり、金属酸化物半導体構造です。 酸化物を使用しない場合、MISFET(I-絶縁体)またはMDPT(D-誘電体)と呼ぶことができます。

JFET(J-接合)または制御pn接合を備えたトランジスタ。 このようなトランジスタでは、制御pn接合に電圧を印加することにより、チャネルをブロックする電界が生成されます。

ショットキー電界効果トランジスタ(PTSH)またはMESFET(ME-金属)は、制御としてpn接合ではなく、ショットキーバリア(半導体と金属の間)を使用するJFETの一種で、電圧降下が小さく、動作速度が高速です。

HEMT(高電子移動度トランジスタ)または高電子移動度のトランジスタ-ヘテロ接合を使用したJFETおよびMESFETのアナログ。 このようなトランジスタは、複雑な半導体で最も一般的です。

図4. BJT、MOSFET、JFET

ゲルマニウム

最初のトランジスタはゲルマニウムでしたが、さまざまな企業の技術者がすぐにシリコンに切り替えました。 これは、純粋なゲルマニウムが実際には電子アプリケーションに非常に適していないという事実によるものでした(ただし、ゲルマニウムトランジスタは依然としてアンティークの草刈り機で使用されています)。 ゲルマニウムの利点の中には、電子移動度が高く、最も重要なのは、シリコンの0.3 V対0.7 Vのpn接合のロック解除電圧だけでなく、2つ目はショットキー遷移を使用してレベリングできます(TTLSロジックで行われたように) 。 しかし、バンドギャップが小さい(0.67対1.14 eV)ため、ゲルマニウムダイオードには温度とともに大きく増加する大きな逆電流があり、ゲルマニウム回路の適用範囲と許容電力の両方が制限されます(小さな電流に対する逆電流の影響は大きすぎます。自己発熱を妨げる)。 ゲルマニウムの温度問題を補うために、その熱伝導率はシリコンの熱伝導率よりはるかに低く、つまり、強力なトランジスタから熱を除去することはより困難です。

半導体エレクトロニクスの歴史の初期においてさえ、ゲルマニウムデバイスは、酸化物による外部の影響から保護されていないシリコンとは異なり、らせん格子転位のない純粋な結晶ゲルマニウムを得ることが困難であり、表面品質が低いため、大きな歩留まりの問題がありました。 より正確には、ゲルマニウムには酸化物がありますが、その結晶格子は、シリコンよりもはるかに悪い純粋なゲルマニウムの格子と一致し、許容できないほど多くの表面欠陥の形成につながります。 これらの欠陥は、電荷キャリアの移動度を著しく低下させ、シリコンに対するゲルマニウムの主な利点を無効にします。 さらに、酸化ゲルマニウムは水と反応します-チップの製造プロセス中および動作中の両方で。 しかし、残りの半導体はさらに幸運でなく、酸化物はまったくありません。

Shockleyは、電界効果トランジスタの製造を妨げていたゲルマニウム表面の問題を解決しようとして、チャネルを半導体の奥深くに除去するというアイデアを思いつきました。 そのため、制御pn接合、別名JFETを備えた電界効果トランジスタがありました。 これらのトランジスタは、(バイポーラトランジスタと比較して)入力電流が非常に小さく、ノイズ特性が優れているため、まずアナログ回路での位置を見つけました。 この組み合わせにより、JFETはオペアンプの入力段に最適な選択肢となります。 これは、たとえばKen Shirrif によるこの記事で確認できます。 さらに、個別のコンポーネントの代わりに集積回路を作り始めたとき、JFETはバイポーラ技術と非常によく互換性があり(上図のバイポーラトランジスタからJFETを作りました)、アナログバイポーラ製造プロセスの一般的な場所になりました。 しかし、これはすべてシリコン上にすでにあり、ゲルマニウムはシリコンと戦う代わりにシリコンの地位を強化する時が来るまで長年忘れられていました。 しかし、それについては後で。

電界効果トランジスタ

MOSトランジスタはどうですか? 彼らは双極の相手の急速な進歩に関連してほぼ10年間忘れられていたように見えますが、それでも発展しました。 1959年のベル研究所と同じように、最初に動作するMOSトランジスタは、デボンカンとマーティンアッタラによって作成されました。 一方で、彼はLilienfeldのアイデアをほぼ直接実現し、他方で、彼はシリコン酸化物をゲート誘電体として使用する多くの次世代トランジスタとほとんど同一であることがすぐに判明しました。 残念ながら、Bell Labsは本発明の商業的可能性を認識していませんでした。プロトタイプは当時のバイポーラトランジスタよりも大幅に低速でした。 しかし、この新規性の可能性はアメリカのラジオ社(RCA)とフェアチャイルドによって認識され、1964年にはすでにMOSトランジスタが市場に出回っていました。 それらは、バイポーラの同等品よりも遅く、増幅され、ノイズが多く、静電気放電の影響を非常に受けましたが、入力電流がゼロで、出力抵抗が低く、優れたスイッチング能力を備えていました。 それはそれほどではありませんが、それは非常に長い旅の始まりに過ぎませんでした。

バイポーラロジックとRISC

半導体エレクトロニクスの開発の初期段階では、アナログおよび高周波アプリケーションが支配的でした。長い間、「トランジスタ」という言葉は、トランジスタ自体だけでなく、それに基づくラジオ受信機も意味していました。 1つまたは2つのゲートを含む超小型回路に基づくデジタルコンピューターは巨大であるため(ランプのゲートと比較することはできませんでした)、類似の方法で計算を行うことさえ試みられました-デジタルチップ全体の散乱の代わりに1つの演算増幅器を統合または差別化することは良いことです。 しかし、デジタルコンピューティングはより便利で実用的であることが判明し、その結果、デジタル電子コンピューターの時代が始まり、今日も続いています(ただし、量子コンピューティングとニューラルネットワークはすでに大きな成功を収めています)。

当時のMOSテクノロジーの主な利点はシンプルでした(80年代まで、各マイクロエレクトロニクス企業は独自の生産を組織しなければならなかったことを思い出します):最も単純な動作n-MOSまたはp-MOS回路を実装するには、CMOSには6枚、バイポーラリソグラフィ回路では、1つのタイプのトランジスタに7つが必要であり、拡散のより正確な制御と、理想的にはエピタキシーが依然として必要です。 ファットマイナスは速度でした。MOSトランジスタは、バイポーラやJFETと比較して1桁以上失われました。 CMOSが5 MHzの周波数に達することを許可した時点で、ESLで100〜200を作成できました。 アナログアプリケーションについて話す必要はありません。MOSトランジスタは、低速と低ゲインのために非常に不適切です。一方、JFET入力を備えたバイポーラ回路は、ほとんどすべての設計者の要求を提供できます。

超小型回路の集積度は小さく、消費電力を特に考慮した人はいませんでしたが、高性能アプリケーション向けのエミッタ結合ロジック(ESL)の利点は明らかでしたが、MOSテクノロジーのスリーブには切り札があり、それが少し遅れて再生されました。 60年代、70年代、80年代には、MOSとバイポーラ製造プロセスが並行して開発され、MOSはデジタル回路専用に使用され、バイポーラ技術はアナログ回路とTTL(トランジスタ-トランジスタロジック、TTL)およびESLファミリに基づくロジックの両方に使用されました。

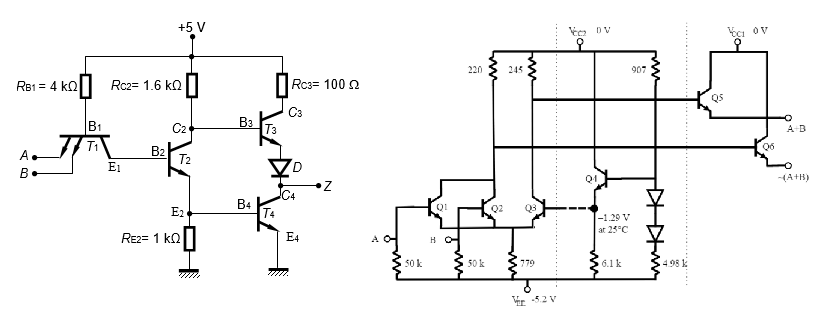

図5. 1975年に一般公開された最初のSeymour CrayスーパーコンピューターであるCray-1は、重量が5.5トン、エネルギー消費が115 kW、容量が80 MHzで160 MFLOPSでした。 4種類のディスクリートECL回路上に構築され、約20万個のバルブが含まれていました。 ロジックが構築されたチップは、要素4 ILINEおよび5 ILINEを含むデュアルバルブであるフェアチャイルド11C01で、-5.2 Vで電力を供給されると25-30 mAの電流を消費します。

図6. TTL上の論理要素2INEおよびESL上の2OR / ILINE

ESLロジックエレメントは、スイッチングトランジスタが常に「高速」リニアモードであり、「低速」飽和モードに陥らないように構築された単なるフィードバックアンプであることに注意してください。 速度に対する料金は、動作周波数や入力および出力の状態に関係なく、回路を連続的に流れる電流です。 おもしろいですが、彼らはこの欠点を少し前に利点として使用しようとしました:ESLの暗号回路は、消費電流が特定の時間に切り替わるバルブの数に比例するCMOSよりも消費電流を「聞く」ことにより、クラッキングに対してはるかに耐性があります。 バイポーラトランジスタを電界効果トランジスタ(JFETまたはMESFET)に置き換えると、ISL(ソース関連ロジック)が得られます。これは、当時の複雑な半導体にも応用されていました。

nMOSまたはpMOSロジックの明らかな利点は、製造が簡単で、トランジスタの数が少ないことです。これは、小さな面積と、より多くの要素をチップ上に配置できることを意味します。 比較のため:nMOS / pMOSの2INEまたは2ILINEエレメントは、CMOSの3つのエレメントで構成されます-4つ。 TTLでは、これらの要素には4〜6個のトランジスタ、1〜3個のダイオード、4〜5個の抵抗が含まれます。 ESLでは-4つのトランジスタと4つの抵抗(ESLではORとNORを実行すると便利であり、ANDとNANDには不便です)。 ところで、TTLおよびESLエレメントの回路内のトランジスタはすべてnpnであることに注意してください。 これは、p基板にpnpトランジスタを作成することがnpnよりも複雑であり、その構造が異なるためです。両方のタイプのトランジスタがほぼ同じであるCMOSテクノロジーとは異なります。 さらに、ホールを犠牲にして動作するpMOSとバイポーラpnpは、どちらも「電子的」なものよりも低速です。つまり、速度が主な目的であるバイポーラロジックでは、対立しませんでした。

MOSテクノロジーの2番目の重要な利点は、CMOSへの移行中に完全に現れ、このテクノロジーの優位性を大きく決定したものであり、低消費電力です。 CMOSバルブはスイッチングプロセス中にのみエネルギーを消費し、静的なエネルギー消費はありません(最新の技術ではそうではありませんが、詳細は省略しています)。 ESLバルブの一般的な動作電流は、100μA〜1 mA(0.5〜5 mW、5.2 Vで駆動)です。 この数に、たとえば最新のIntelプロセッサを構成する10億ゲートを掛けると、MegaWattが得られます。実際、上記で見たCray-1の消費量です。 しかし、80年代には、通常、数千または数万のバルブの問題であり、理論的には、バイポーラロジックであっても、妥当な電力バジェット内に保つことができました。 ただし、実際には、消費電力が少なく、設計基準の低下に伴ってはるかに高速化されたCMOSバルブが同じ結晶領域に配置されました(ムーアの法則は強力なものと主要なもので機能しました)。

10ミクロンのpMOSテクノロジーを使用するIntel 8008(1972)は、500 kHzの周波数で動作しました(より複雑なCray-1システムでは80 MHzに対して)、Intel 8086(1979)は3ミクロンのnMOSと10 MHzに加速されたCMOSを使用し、元の80486( 1989)-最大50 MHz

設計者が、バイポーラとCMOSの違いが急速に減少し、エネルギー消費にもかかわらず、バイポーラ設計を試み続けたのはなぜですか? 答えは簡単です-速度。 明け方、ESLの追加の大きな利点は、大きな容量性負荷または長いラインで作業するときのパフォーマンスの損失が最小限であったことです。つまり、ESLロジックを使用した多くのケースのアセンブリは、CMOSまたはTTLでのアセンブリよりもはるかに高速でした。 集積度の向上により、CMOSはこの欠点を部分的に克服でき、コンピューターシステムは依然としてマルチチップであり、クリスタルの外部(たとえば外部キャッシュへ)の各出力はすべてを遅くしました。 しかし、バイポーラバルブは、たとえば、論理ゼロと論理ユニットの間の電圧差が数倍小さいため、ESLで600-800 mV対CMOSで5 Vであるため、80年代後半でもずっと高速でした。これは、トランジスタのサイズがバイポーラ技術はすでにCMOSに遅れをとってきています。 しかし、CMOSスケーリングが、チップの単位面積あたりの特定の電力が一定のままになるようになった場合(この現象はムーアの法則の「結果」であり、「デナードスケーリング」と呼ばれます)、高速動作には静的動作電流が必要なので、ECLの電力はほとんど低下しませんでした。 その結果、デジタル回路設計者は、より高い生産性が必要な場合でも、ますます洗練されたコンピューティングシステムアーキテクチャを実装するためにCMOSを好むようになりました。

デジタルバイポーラテクノロジーの支援は、彼らが待たなかったところから生まれました。 80年代前半には、RISCコンセプトが発明されました。これは、マイクロプロセッサの大幅な簡素化と、その中の要素数の削減を意味します。 バイポーラテクノロジは、集積度においてCMOSにやや遅れていました。これは、バイポーラLSIの大部分がアナログであり、ムーアの法則を急ぐ大きな理由がなかったためです。 それでも、RISC開発の始まりは、プロセッサ全体を1つまたは少なくとも2つまたは3つのチップにパックすることが現実的になった瞬間と一致しました(キャッシュは通常外部でした)。 1989年にIntel 80486がリリースされ、FPUはメインプロセッサと同じチップで実行されました。これは、100万個を超えるトランジスタを使用した最初のチップです。

問題の時までに、多くのチップメーカーはファブレスモデルに切り替え始め、他の企業に生産組織を提供しました。 これらの企業の1つの活動の結果、ESL上の統合マイクロプロセッサが開発されました。 同社はBipolar Integrated Technologyと呼ばれ、1983年の創業から1996年のPMC-Sierraでの販売まで、特に成功したことはありませんでした。失敗の理由は、まさにバイポーラデジタル製品への賭けだったと疑われていますが、80年代後半にはそれほど明白ではありませんでした、同社は規模と統合度の点で高度なバイポーラプロセスを有していました。 彼らの最初の製品はFPUコプロセッサチップであり、BITは2つのRISCの先駆者であるMIPS Computer SystemsとSun Microsystemsと積極的に協力して、このコプロセッサが役立つRISCアーキテクチャに基づいてチップを作成しました。 MIPS IIアーキテクチャの最初の実装であるR6000、R6010、およびR6020チップセットは、ESLに実装され、BIT施設で生産されました。 また、SPARC B5000プロセッサも生産しました。

やがて、DECはモトローラのバイポーラ技術を使用して、単一チップにMIPS IIを実装しました。 想像してみてください。1993年の構内では、Intelの主要製品はPentium(CMOSプロセス技術800 nm、クロック周波数66 MHz、TPD 15 W、チップ上の300万個のトランジスタ)です。 「 300 MHz 115-W 32-bバイポーラECLマイクロプロセッサ 」というタイトルの記事がIEEE Journal of Solid-State Circuitsに掲載されています。 300(!)メガヘルツと115(!!!!)ワット。 もちろん、この怪物の体とヒートシンクについては別の記事が取り上げられました。 IEEEライブラリにアクセスできる場合は、両方の記事を読むことを強くお勧めします。これは、「チップは主に設計チームのメンバーが開発したCADツールを使用して設計された」スケールのフレーズと「回路のパフォーマンスが向上した時代の素晴らしい文書ですさまざまなアプリケーションでさまざまな信号スイングを使用すること、および回路トポロジ(低スイングカスコード回路やワイヤードOR回路など)を使用することにより大幅に向上します。 OK CAD、1993年に怠laな人だけが自分で書いたわけではありません( YuriPanchulに尋ねてください 、彼は確認します)が、ワイヤードOR!

図7. DECプロセッサチップとそのヒートシンクの写真

2レベルの論理ゼロと1、ライブラリ内の75エレメント、5独自のCADシステム、C内の半回路、すべての種類と色のトレース方法、トポロジプリミティブ、ブロックツリー、3層のメタライゼーション、放射線耐性、キロバイトのキャッシュ、 2ダースのテストベンチ。 それが設計に必要なものではなかったのではなく、マイクロプロセッサの組み立てを開始した場合、停止するのが難しくなります。 私を心配させた唯一の事はワイヤードORでした。 世界中でワイヤードORほど無力で無責任で悪質なものはありません。 遅かれ早かれ、このゴミに進むことを知っていました。耐放射線性や他の特別な機器といえば。 1948年のトランジスターの開通の物語、および他の多くのあまり知られていない出来事(たとえば、米軍の資金によるシリコンバレーの作成)は、軍隊の神話が、ゆるい74シリーズとTL431で第5世代の戦闘機をリベットする準備ができている人々として、 28 nmまたは16 nmの設計基準は、テレビでのみ聞かれ、少なくとも不公平です。 本物の軍隊は、常に新しい技術を適用するだけでなく(適切な認証を取得した後、かなりの時間がかかる場合もあります)、その作成に資金を提供しています。 したがって、TTLマイクロ回路の有名な「第74」シリーズは、もともと軍事用に作成された単純化された「第54」です。 AMDが長年使用して成功した「シリコン・オン・インシュレーター」技術や、私たちの日常生活に長くしっかりと定着した他の多くの技術についても同じことが言えます。 そのため、ESLの耐放射線性は、CMOSアナログの耐放射線性よりも平均して高かった(おそらく現在はより高い)-バルブに大きな一定の動作電流がある場合、リークやトランジスタゲインの低下についてあまり心配していないためです。 この事実は、ESL開発と私の物語の次のパートのヒーローの両方の寿命をさらに延ばしました。

ヒ化ガリウム-未来の材料

ヒ化ガリウムは、マイクロエレクトロニクス業界の注目を集めた最初の複雑な半導体の1つです。 ゲルマニウムとシリコンの両方に対するヒ化ガリウムの主な利点は、その大きな電子移動度です。 同時に、彼はかなり広い禁制帯もあり、高温での作業が可能です。 数百MHzまたは数GHzの周波数で動作すると同時に、数十MHzがシリコンからほとんど搾り取られない場合、これは夢ではありませんか? ヒ化ガリウムは、シリコンを置き換えようとしている「未来の材料」と長い間考えられてきました。 最初のMESFETは1966年に作成され、その上でLSIを作成する最後の積極的な試みは、90年代半ばにCray Corporation(最終的に埋められました)およびMikron(一連のK6500チップ)で行われました。

解決しなければならない重要な問題は、ヒ化ガリウムに自然酸化物が存在しないことでした。 しかし、これは問題ですか? 結局のところ、酸化物がなければ、耐放射線性に問題はありません! . , . JFET — , , JFET MOSFET n- — , . — , JFET , , , MOSFET. , , . , , GaAs ED JFET (E — enhancement) (D — depleted) . — , . nJFET (, ), 1 , , - .

, , RISC MIPS. 1984 DARPA GaAs MIPS — RCA, McDonnell Douglas CDC-TI. 30 , “ ”. , Am2900 AMD, 1802 RCA, .

, 1990 , MIPS , SPARC — LEON MIPS. , LEON ARM, - . ARM- . , . , , Elsevier .

McDonnell Douglas. IEEE Transactions on Nuclear Science ( Zuleeg), 1971 JFET 1989. ? ( , ) -, , , . nJFET-, McDonnell Douglas — , - .

, , , , , . “ ” - « 3%, 75 », « - , 1% 10%», . , , , , , , , , . , , , . , , , .

, ?

, , ? , . — ( , , ) IEEE, , — . . , , ( , , ). , , , , , . , , , , . , , , . , , , — , . , , ( , ), — , “” .

, GaAs Cray, -4, RISC-, , . , , , “” 6500, 16 , — , . McDonnell Douglas JFET GaAs n , , 6500 ( 1 ), MESFET ( ).

8. McDonnell Douglas 6500

«» 1984 1996 , , , . “”, , .

; , , , — , . , , , , .

9. , -

, , ? , , . , , , , .

, , . 2000 , , — « , ». , ( ), 5G, 39 , A3B5, - , .

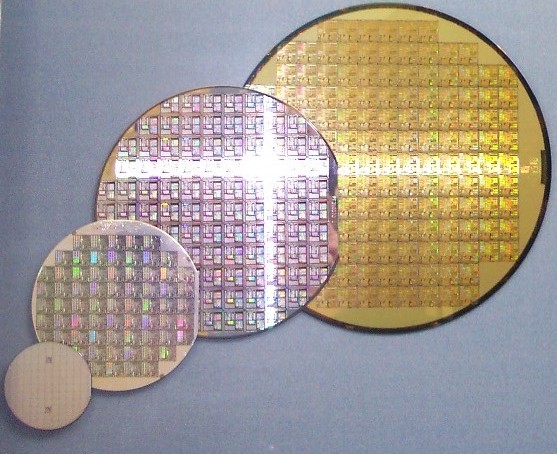

, , . TSMC 5 180 200 — . , , . . , , , . . 180, 90 65 “”, 200 “” 150 “”. , STM , 180 «», , . STM SiC, , , .

80年代後半と90年代前半の記事は、有望な技術に捧げられています-シリコン上のESLは、GaAs上のJFETを補完し、ゲルマニウムを再び素晴らしいものにしようと試みます-ほぼ常に「私たちのアイデアの優れた見通しを実証し、数年後に技術がさらに発展し、文字通りチップ上でより多くのトランジスタを使用できるようになり、消費量が減り、歩留まりが向上し、世界を征服します。」 それは、DARPAが決してやってこなかったお金の約束された進歩です。 なんで? チップを製造するテクノロジーは、サイズが新しくなるたびに価格が上昇し、研究助成金がインテルの投資額を上回ることはないため、巨大な消費者市場で働いており、技術的リーダーシップが商業的リーダーシップの鍵の1つであることを十分に認識しています。 Intelがムーアの法の旗を掲げ、その実装に自ら責任を負ったのはそのためです。その後、他のすべてのメーカーは、中小企業や他のテクノロジーが予測できないほどのクレイジーな軍拡競争に巻き込まれました。 その結果、Intelはパーソナルコンピュータのニッチ分野で競合他社を1社だけ抱えており、一般に14nm未満の技術を保有しているのは世界で3社だけです(TSMC、Intel、Samsung)。 インテルは、ESLではなくMOSトランジスタを使い始めたのはかなり前のことでしたが、ラッキーでなければ、他の誰かがラッキーであり、結果はほぼ同じままです。

シリコン上のCMOSの利点が否定できないという事実は、90年代の終わりまでに明らかになり、特定のニーズに合わせて新しいテクノロジーを開発する代わりに、対応する重み付け要素をCMOSに取り付けることがより容易になるようになりました。 バイポーラnpnトランジスタを備えたBiKMOPテクノロジーは、アナログ回路設計者、組み込み電子機器の不揮発性メモリ、電力用途の高電圧DMOSトランジスタ、高温または高速のSOI基板、オプトエレクトロニクスの集積フォトダイオードに登場しました。 CMOSテクノロジーに追加オプションを統合するための重要なドライバーは、チップ上のシステムの概念でした。 以前にシステム設計者がターゲット機能への対処方法に基づいて適切な超小型回路を選択し、製造技術に注意を払わなかった場合(最悪の場合、レベルトランスレーターが依然として必要でしたが、これは怖くはありません)、統合の度合いの増加、機会システムのすべてのコンポーネントを1つのチップに配置し、1石で多くの鳥を殺します-プリント回路基板のトラック容量をポンピングする必要がないため、速度を上げて消費を減らします。 はんだ付け点の数を減らして信頼性を高めるために、より良い整合素子によってchnost。 ただし、このためには、システムのすべての部分がCMOS互換である必要がありました。 工場はこれに「何でも、追加のマスクと技術オプションにお金を払うだけ」と答え、生産に特化した技術プロセスを一つずつ投入し始めました。 余分なマスク-高価で複雑ですが、チップを安くする必要がありますか? そして、アナログ設計の教科書はすでに、良い高速のバイポーラトランジスタから悪い低速の電界トランジスタに書き換えられています。 電子レンジの速度はまったくありませんか? ヒ化ガリウムをもう一度試しますか? いいえ、シリコンの結晶格子をゲルマニウムで引き伸ばして、電子移動度を局所的に高めましょう。 複雑に聞こえますか? しかし、CMOS互換です! フラッシュメモリーとシングルチップ上のADCを備えた安価なマイクロコントローラーは、3つのチップ上の同じマイクロコントローラーよりも格段にいいですね。 システムのアナログ部分と同じチップ上でのデジタルデータ処理と制御は、マイクロコントローラーが深宇宙から電気ケトルまであらゆる場所に侵入できるようにする重要な成果となりました。

図10. BCDテクノロジーの概略セクション

この種の私のお気に入りの例は、BCDテクノロジーです。 BCDは、バイポーラ(アナログパーツ用)、CMOS(デジタル用)、DMOS(制御ロジックと同じチップ上の高電圧スイッチ)です。 このような技術は最大200ボルト(時にはそれ以上)の電圧で動作し、電気モーターやDC / DC変換を制御するために必要なすべてを単一のチップに実装できます。

図11.絶縁ポケットに高電圧LDMOSトランジスタを搭載した断面SOI BCD

BCD SOIテクノロジーは、上記のすべてを要素の完全な誘電体分離で補完し、サイリスタ効果抵抗、ノイズ分離、動作電圧を向上させ、チップ上にハイサイドキーを簡単に配置したり、負の電圧で作業したりすることができますゼロボルト)。 メーカーは、同じチップ上に不揮発性メモリ、IGBT、ツェナーダイオードを配置することを提案しています...リストは長く、プレゼンテーションででたらめビンゴをプレイできます)シリコン層の深さに注意してください:「通常の」SOIテクノロジーとは異なり、それを最小限に抑えて取り除くドレインとソースのpn接合の底から、動作速度を上げるため、BCDシリコン層は非常に深く、静電放電と熱特性に対する許容可能な抵抗を提供します。 同時に、トランジスタは完全に絶縁されている場合のみ、体積トランジスタとまったく同じように動作します。 自動車電子機器メーカーのターゲットオーディエンスに加えて、彼らはこれを使用して、独自の高電圧ではなく耐放射性のCMOSチップ、たとえばMilanderやAtmelを作成し、通常の欠点なしにSOIの主な利点を享受します。

CMOSと代替の未来

シリコントランジスタのサイズの縮小が物理的な限界に達したという事実によりムーアの法則が破れ始めた場合でも、CMOSを思い起こさせることは、根本的に新しいものを探すよりも有益であることが判明しました。 もちろん、代替手段や脱出ルートへの投資が行われましたが、シリコンCMOSを改善し、開発の継続性を確保するために主な努力が注がれました。 グラフェンの発見で、ノヴォセロフとゲームはほぼ10年前にノーベル賞を受賞しました。 そして、そのグラフェンはどこにありますか? そうです、カーボンナノチューブと将来のその他すべての材料、およびシリコンはすでに5 nmプロセスによる生産を開始しており、すべてが3または2 nmにもなります。 もちろん、これらは実際のナノメートルではありません(Habrについてはすでにこちらで説明しています )が、パッキング密度は増え続けています。 非常に遅いですが、それでもシリコンCMOSです。

図12. 5 nm以下のSamsungトランジスタのゲート 次のステップは、FinFETと「なぜトランジスタをいくつかの層にパックしないのか?」という質問に対する答えと比較したものです。他のすべての方法は使い果たされました。 これらのトランジスタを7つ縦に並べると、7つではなく1ナノメートルになります!

すべてが元々考えられていた酸化ケイ素でさえ、CMOSの進歩の犠牲になりました! 酸化ハフニウムに基づく複雑な多層構造に置き換えられました。 ゲルマニウムは、モビリティを高めるためにチャネルに追加され始めました(BiKMOSマイクロ波の開発で既にテストされています)。 「シリコン」トランジスタで、A3B5材料(電子移動度が高い)からのn型チャネルと、ドイツからのp型チャネル(正孔移動度が高い)を(現時点ではテストのみ)テストすることさえできます。 チャネルの形状を平面から3次元(FinFET)に変更するなどの些細なことや、多数の設計標準を使用したマーケティングの秘、については、何も書かなくても十分です。

将来、私たちを待っていますか? 一方で、EUVリソグラフィとGate All Aroundトランジスタの導入に伴うシリコンテクノロジーの進歩は、すでに枯渇しています。 20年前のITRSの計画に対する遅れはすでに約10年であり、Intelはその有名な「ティックタック」であるGlobalfoundriesを長い間放棄し、14 nmを下回ることを完全に拒否しました。 チップあたり1つのトランジスタのコストは、少なくとも28 nmの基準を超えており、その後成長を始めています。 そして最も重要なことは、ターゲット市場が変化したことです。 長年、設計基準を下げる要因はパソコン市場でしたが、その後パソコンは携帯電話に変わりました(この頃、TSMCとSamsungはIntelに追いつきました)。 しかし、現在、携帯電話市場、不況と停滞。 チップのマイニングには短期的な希望がありましたが、実現しなかったようです。

新しいお気に入りのチップメーカーは、モノのインターネットです。 実際、市場は大きく、急速に成長しており、長期的な見通しが良好です。 そして最も重要なこと-モノのインターネットにとって、チップ上のパフォーマンスと要素数は競争上の重要な利点ではありませんが、低消費電力と低コストは重要です。 これは、設計基準を削減する主な理由がなくなったことを意味しますが、特定のタスクのためにテクノロジーを最適化する理由があります。 おもしろそうですね。 グローバルファウンドリーズのプレスリリースは、7 nmでの作業の終了と14/12および28/22 nmのFDSOIでの濃度に関するプレスリリースです。 さらに、激しい価格競争と相まって、新技術の価格の上昇により、チップメーカーは新しい設計標準への切り替えを急いで行うことができました。なぜなら、できる限り、古いものを維持し、異機種を統合するためです。チップ-しかし、ボード上ではなく、ケース内。 「System on a chip」は「system in a case」に置き換えられました(これについてはすでに詳しく説明しました )。 ケース内のシステムの出現と、特にモノのインターネットは、1つのケースにヒ化ガリウムチップをシリコンと配置することで干渉しなくなるため、複雑な半導体に新たな機会を与えます。 同じことは、さまざまな光学デバイス、MEMS、センサーに適用されます。一般的に、シリコン上のCMOS以外のマイクロエレクトロニクスに存在するすべてのものに適用されます

したがって、シリコン技術とその代替品のCMOSのさらなる開発の私の予測は、完全に停止するまでの根本的な減速の進行を見ることであり、不必要に-大量生産(カーボンナノチューブ、グラフェン、メモリスタの論理)-再び、不必要。 しかし、間違いなく、既存の技術的手荷物の使用はより広くなるでしょう。 マイクロエレクトロニクスは私たちの生活のあらゆる領域に浸透し続けており、利用可能なニッチの数は膨大であり、新しい市場が現れ、成長し、成長し続けます。 世界の大手メーカーは、最新の設計基準だけでなく、古いものの生産も増やしています:TSMCは15年ぶりに200 mmプレートの工場を建設しています。Globalfoundriesは昨年、新しい180 nm BCD製造プロセスを導入しました。 世界の主要メーカーは、控えめな追加により、近い将来に大きな利益を約束する新しいニッチについて楽観的です。 一般的に、ナノメートルの進歩がないにもかかわらず、退屈することはありません。