このメモでは、HR5000 SoCとそのプロセッサコアに含まれるものについて簡単に説明し、MIPS 4Kおよび5Kラインの2人の主要開発者の写真を示します。 32ビットMIPS microAptiv UPカーネル。Verilogハードウェア記述言語のコードはMIPS 4KEcに基づいていました。

日本の航空宇宙機関JAXAは、米国企業のMIPS TechnologiesからMIPS 5Kfプロセッサコアのライセンスを取得しました。 これは2000年代に起こりました。 このコアを開発したグループは、40年間さまざまな構成で存在していました。

- まず、1978年から1984年にかけて、MIPSはジョンヘネシーが率いるスタンフォードのプロジェクトでした。 このプロジェクトの成功により、ヘネシーはコンピューターアーキテクチャに関する最も有名な教科書の著者になり、ある時点でスタンフォードの社長になりました。

- その後、1984年に、MIPSはMIPS Computer Systemsという商業会社になりました。 同じ年に、ARMも商品化されました。 1991年、MIPSは世界初の64ビットマイクロプロセッサであるMIPS R4000をリリースしました。

- その後、MIPSはシリコングラフィックスに吸収され、1990年代にグラフィックステーション内で使用され、ハリウッド(ジュラシックパーク)でリアルなグラフィックスを備えた最初の映画が作られました。

- 2000年代に、グループはMIPS Technologiesに分離し、特に、JAXA用のプロセッサを設計しました。 MIPSの本社はカリフォルニアにあり、MIPS 5Kf開発者の一部はコペンハーゲンの MIPS Europeにいました。

- 2012年、MIPS Technologiesは英国のImagination Technologiesに買収され、初期のApple iPhone内でGPU開発者として有名になりました。

- 2017年、AppleはImaginationを投入し、いくつかの混乱の後、テクノロジーとMIPSグループの一部が、ニューラルネットワークを加速するチップを開発する新興企業であるWave Computingに統合されました。

- Wave Computingチップは、64ビットMIPS I6500プロセッサのクラスター、Google TPUのシストリックアレイに基づくマトリックス乗算器、および粗粒度の再構成可能なアーキテクチャを備えたデバイスに基づくデータプロセッサプロセッサ-CGRAの組み合わせです。 ) I6500クラスターのクラシカルプロセッサは、マトリックス乗算器とデータストリームプロセッサを読み込み、マトリックス乗算器は計算密度を提供し、タスクデータストリームプロセッサは、クラシカルプロセッサとマトリックス乗算器の間に配置されます-乗算器よりも柔軟性があり、クラシカルCPUよりも生産的です。

そこで、私はMIPS 4Kおよび5Kラインの2人の主要開発者の1人であるLarry Hudepohl、Larry Huedepol(右側の赤いシャツ)で写真を撮りました。 Larryは、Digital Equipment Corporation(DEC)でMicroVAXのプロセッサ設計者としてキャリアを始めました。 その後、Larryは小さな会社Cyrixで働きました。Cyrixは、1980年代後半にIntelに挑戦し、Intel 80387と互換性があり、50%高速なFPUコプロセッサを作成しました。 その後、LarryはSilicon GraphicsでMIPSチップを設計しました。 MIPS TechnologiesがSilicon Graphicsから分離したとき、LarryとRyan Quinterは一緒になって最初の独立したMIPS製品であるMIPS 4Kを発売しました。これは、2000年代の家電製品(DVDプレーヤー、カメラ、デジタルテレビ)を支配するラインのバックボーンとなりました。 その後、MIPS 5Kが宇宙に飛びました-日本の宇宙機関JAXAによって使用されました。 その後、ラリーはハードウェアエンジニアリング担当副社長として次のラインの開発を指揮し、現在は新しいWaveアクセラレーターアーキテクチャの開発に取り組んでいます。

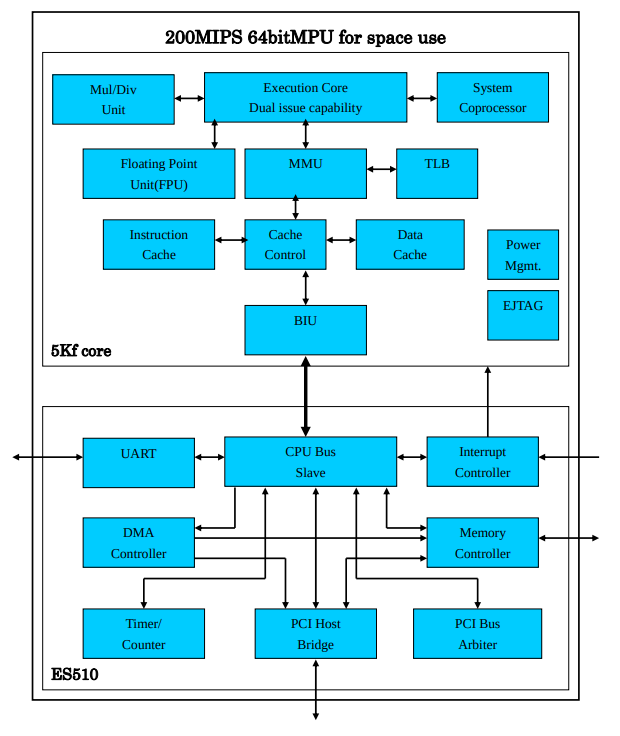

さて、はやぶさ2のプロセッサに戻ります(はやぶさ1では違います)。 これは、MIPS64 5Kfプロセッサコアのデータシートと 、HR5000チップ上のシステムデータのページです。 興味深い点に注意してください。

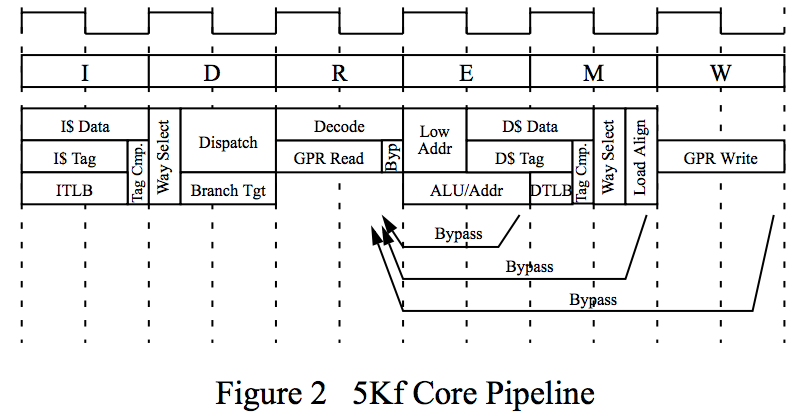

まず、MIPS 5Kfはパイプラインプロセッサです。 これがどのように機能するかに慣れていない場合、お互いを知るための最も簡単な方法は、David M. HarrisとSarah L. Harrisによる本「Digital Circuitry and Computer Architecture」の第7章を研究することです。 。 同時に、MIPS 5Kfのコンベヤーは、Harris&Harrisの従来のMIPSコンベヤーとは異なります。 X&Xを読んだ人は、違いを見て理由を推測できます。

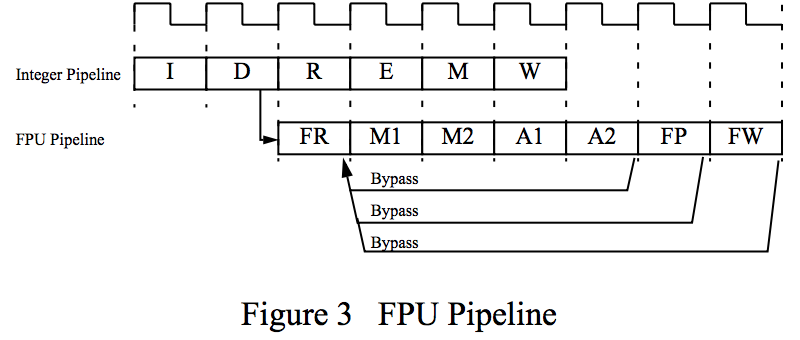

もちろん、MIPS 5Kfには5つのパイプラインステージがありませんが、6つのパイプラインステージに追加のDispatchステージがあります。 この段階は、MIPS 5Kfを限りなくスーパースカラーにするために必要です。 パイプラインで操作を次々に実行できるだけでなく、整数操作またはメモリ操作(ロードまたは保存)と同時に浮動小数点操作も実行できます。 Stage Dispatchは、独自の7ステージパイプラインを持つ浮動小数点コプロセッサーを起動します。

そして、写真の右側には、MIPS 5KfのFPU開発者であるDarren Jones、Darren Jonesがいます。 「5Kf」の文字「f」は、浮動小数点があることを正確に意味します。

このプレートでは、FPUで異なる操作を必要とするサイクル数と、パイプラインで実行できる頻度(繰り返し率)を確認できます。 たとえば、単精度の乗算には4サイクルが必要ですが、パイプラインでサイクルごとに新しい乗算を開始できます。 そのため、FPUは各処理段階で4つの単精度乗算を同時に処理できます。 ただし、倍精度の乗算には5サイクルが必要であり、サイクルの一時停止でのみ開始できます。 倍精度の平方根を取得する複雑な操作には最大32サイクルが必要であり、29サイクル後に初めて平方根の取得を開始できます。 これにより、宇宙空間での船の座標とその運動式の計算が最適化されます。

「はやぶさ-2」は、32キロバイトの命令キャッシュとデータキャッシュを別々に備えたMIPS 5Kf構成を使用します。 同時に、 HR5000の簡単な説明から、8キロバイトの4チャネルキャッシュを使用するのか、16キロバイトの2チャネルキャッシュを使用するのかは明確ではありません。 これらのキャッシュがどのように機能するかは、X&Xとキャッシュに関する私の以前のプレゼンテーション、およびDominic SweetmanによるMIPS Run Linux 2nd Editionを参照してください。

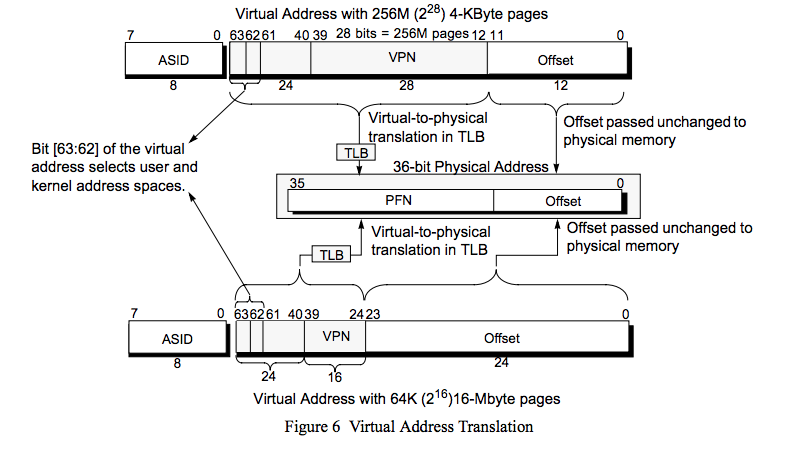

「はやぶさ-2」には、変換ルックアサイドバッファ(TLB)を備えたメモリ管理ユニット(MMU)もあります。 TLBは、アドレスを仮想から物理にすばやく変換するための汎用ツールです。 TLBでできること:

非特権コードからオペレーティングシステムのメモリを隠します。

ユーザープログラムを互いに保護します。

物理RAMの量を超える仮想メモリの量へのプログラムアクセスを提供します。

仮想アドレスよりも大きな物理メモリを使用できます。

プログラムを物理メモリの任意の部分に配置します。

複数のメモリ領域を連続したピースのように見せることができます。

必要に応じて、外部デバイスからプログラムの一部をロードできます。

TLBは、キャッシュ、コヒーレンス属性と同様に、読み取り、書き込み、実行の禁止など、さまざまな属性をアドレスに関連付けます。

キャッシュ属性は、次のキャッシュレベルのアドレス空間の場所と、キャッシュできないI / Oレジスタの場所をプロセッサに示すために必要です。

Coherence属性は、複数のプロセッサコアが連携して動作するために必要であり、それぞれが独自の第1レベルキャッシュを持ち、共通の第2レベルキャッシュを使用します。

TLBは、特定のアドレスを持つページが記録されたことを示すインジケーターを保存できます。 これは、アプリケーションがコードとデータのすべての部分を仮想アドレスでアドレス指定する必要があるよりも物理メモリが少ないシステムで、メモリページをスワップ、ロード、アンロードするときに役立ちます。

これは、MIPS 5Kfで64ビット仮想アドレスを36ビット物理アドレスに変換する方法です。 Hayabusa-2で36ビットの物理アドレスを持つ64ビットプロセッサを使用するのはなぜですか? 「はやぶさ2」は写真を撮り、画像を処理しなければならず、これには多くのメモリが必要だと思います。 おそらく、一部のアルゴリズムでは、64ビットの算術および64ビットのキャッシュ交換(または64ビットのキャッシュ不可のメモリ交換)が何かを改善し、スペースで役立つことが判明しました。 しかし、私は確かに知りません、私はおそらく私よりも宇宙についてもっと知っているZelenyikotとamartologyに尋ねる必要があります。

X&XでTLBを読んでMIPS Runを見ることができますが、微妙な違いがあります。どちらの本もTLBがプログラマーの観点からどのように見えるかを説明しています。 しかし、ハードウェア開発者の観点から見ると、プロセッサの設計者は、実際に「はやぶさ-2」のTLT内に3つのテーブルがあるという事実にもかかわらず、TLBを1つの連想変換テーブルとして見せることでプログラマを欺いています。 最初に、メモリ管理デバイスはITLBとDTLBを検索し、見つからない場合にのみJTLBから取得します。 これにより、プロセッサにさらに2サイクルのコストがかかります。 TLBに関する私の以前のプレゼンテーションも参照してください。

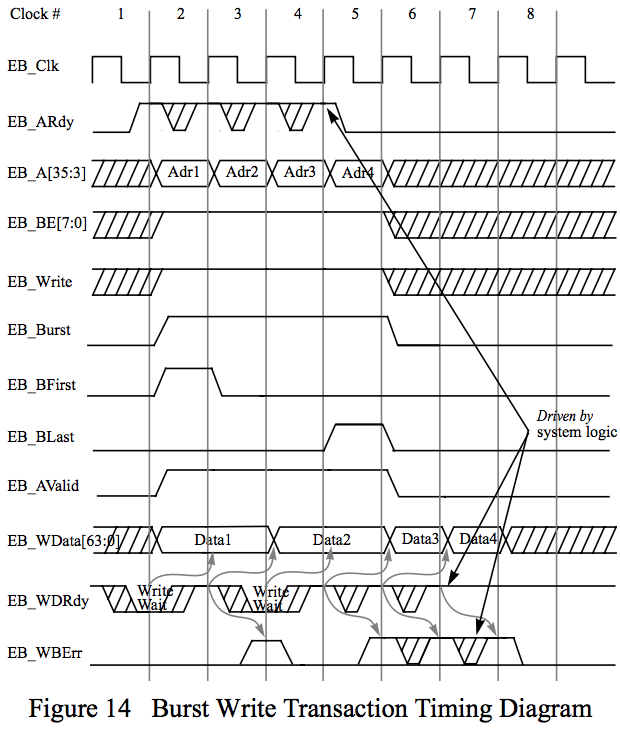

はやぶさ2のMIPS 5Kfの第1レベルキャッシュとメモリコントローラー間のインターフェイスはEB(発音IB)と呼ばれます。 これは外部バスの略です。 これはAHBおよびAXIに似ており、連続ループの転送を使用して、バースト、キャッシュからのダンプ、またはライン全体のキャッシュへの充填を行うことができます。

プロセッサコアの外部に、HR5000には割り込みコントローラー、UARTモジュール、ダイレクトメモリアクセスコントローラー、タイマー、およびPCIコントローラーがあります。

宇宙で作業するには、チップを放射線から保護する必要があります。 私は放射線防護の専門家ではありません、これにはHabréにマートロジーがありますが、そのような防護は物理的な生産技術のレベル、さまざまなECCチェックのレベル、さらには3等のアーキテクチャのレベルの両方で行えることを知っています。 HR5000クリスタルシステムの作成者は、商用アプリケーションで採用されている通常のRTL2GDSIIルート、Verilogハードウェア記述言語のコードからの論理要素からのグラフの合成を使用することにしました。 ただし、このようなグラフ(ネットリスト)を受け取った後、彼らはプリミティブハードウェアバイデザイン(HBD)の特別なライブラリを使用してそれを変更します(これを使用したことがないため、コメントの説明は歓迎します)。

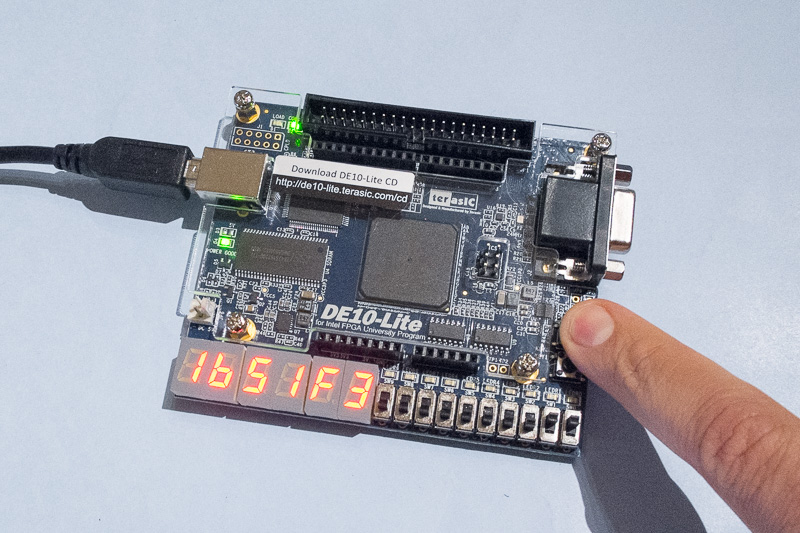

MIPS 5KfはVerilogで記述されているため、ネットリストに変換できるだけでなく、工場でチップを製造するためのマスクだけでなく、FPGAコンフィギュレーションにも変換できます。 残念ながら、MIPS 5Kfのソースはパブリックドメインではありませんが、パブリックドメインには、32ビットMIPS 4Kプロセッサである「弟」の子孫のソースがあります。 この「子孫」はMIPS microAptiv UPと呼ばれ、その基本構成はMIPSfpgaパッケージに含まれています。 MIPS 4K / 4KEc / microAptiv UP / M5150コード(これらはすべてラインのプログレッシブバージョンです)も、Larry、Ryan、Darrenによって書かれました。

パイプライン、キャッシュ、メモリ管理デバイス、MIPS microAptiv UPカーネル割り込みを使用して、FPGA / FPGAを搭載したシミュレーターまたはボードで実行できます。 これを行うには、 MIPS Open™FPGA Labsと共にMIPS Open™FPGA Getting Started Packageをダウンロードし、(これは重要です!) MIPSfpga +で補完します。 後者には、パイプライン、キャッシュ、およびメモリ管理デバイスに関するラボがあります 。

MIPS microAptiv UPプロセッサーは、安価なボードで85ドル(アカデミック価格55ドル)で合成して実行できます。

MIPSfpga / MIPSfpga +パッケージを使用するには、Verilogハードウェア記述言語の知識、レジスタ転送レベルでの設計原則、およびMIPSアセンブラーでの書き込み機能が必要です。

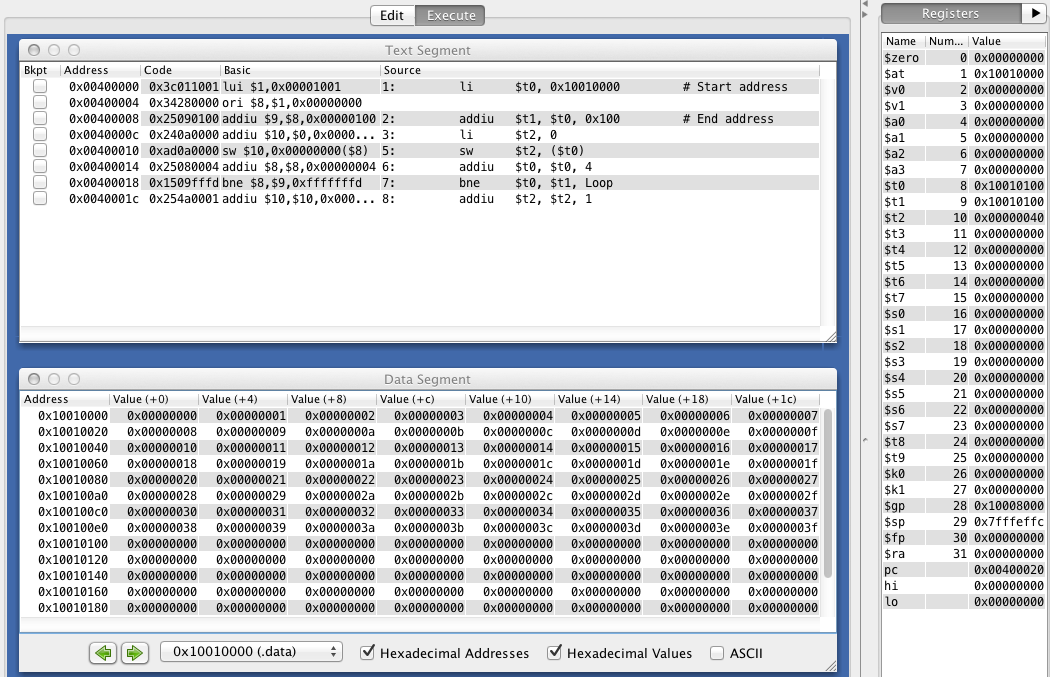

MIPSアセンブラーは習得が最も簡単です。 これを行うには、MARSシミュレーター(MIPSアセンブラーおよびランタイムシミュレーター)をダウンロードできます 。 あなたは5分でそれを使用する方法を学ぶことができます、実際には、3つのボタンがあります-アセンブル、実行、ステップバイステップ:

その後、 Harris&HarrisとSee MIPS Run Linuxの本のためにアセンブリ言語で書く練習に1日を費やすことができます 。

一般的なデジタル回路の開発について、特に機器を説明するための言語でまったく何も知らない場合は、 「 トランジスタからマイクロ回路まで」 、 「デジタル回路の論理的側面」 、 「物理的側面」の 3つのパートで、学童向けのRosnanovオンラインコースから始めることができますデジタル回路 " )。 その後、X&XでVerilogを調べて、簡略化されたschoolMIPSプロセッサにプロセッサがあることを理解できます。

このトピックに興味があり、 MIPS Open (MIPS microAptiv UPカーネルが開かれたフレームワーク内)での作業に参加したい場合は、コメントを書いてください。 Rosnanovtsyは、 4月17日から19日にかけて、 デジタルデザインに関する小学生向けのセミナーも開催します。このセミナーには、特にこのスペースプロセッサが含まれます。 「はやぶさ2」は無駄にならずにリュウガを爆撃しました-これは、ロシアの小学生と学生が彼女の内部を知る機会でもあります。