昨日、2019年4月2日、Intelは2017年半ばに導入されたIntel®Xeon®スケーラブルプロセッサファミリの待望のアップデートを発表しました。 新しいプロセッサは、Cascade Lakeというコードネームのマイクロアーキテクチャに基づいており、改善された14 nmプロセスに基づいています。

新しいプロセッサの機能

まず、ラベル付けの違いを見てください。 Skylake-SPに関する以前の記事で、すべてのプロセッサが4つのシリーズ( ブロンズ 、 シルバー 、 ゴールド 、 プラチナ)に分割されていることを既に述べました 。 数字の最初の数字は、プロセッサモデルが属するシリーズを示しています。

- 3-ブロンズ、

- 4-シルバー、

- 5、6-ゴールド、

- 8-プラチナ。

2番目の数字は、プロセッサの世代を示します。 インテル®Xeon®スケーラブルプロセッサーの場合、コードネーム生成:

- 1-スカイレイク、

- 2-カスケード湖。

次の2桁は、いわゆるSKU(在庫保管単位)を示します。 実際、特定の利用可能な機能のセットを備えた単なるCPU識別子です。

また、モデル番号の後に、1文字または2文字で示されるインデックスがある場合があります。 インデックスの最初の文字は、アーキテクチャの機能またはプロセッサ自体の最適化を示し、2番目の文字はソケットのメモリ容量を示します。

たとえば、 Intel®Xeon®6240というラベルのプロセッサーを使用します。 復号化:

- 6 -Goldシリーズのプロセッサー、

- 2-カスケード湖の生成、

- 40 -SKU。

性能

新世代のプロセッサは、仮想化、人工知能、および高性能コンピューティングの分野での使用を期待して設計されています。 最初の注目すべき変更は、クロック速度の増加です。 プロセッサコアの数よりもクロック速度が重要なサーバーアプリケーションが多数存在するため、これは非常に期待されていました。 たとえば、金融商品1Cのシステム要件では、プロセッサの周波数が高くなるほど、エンドユーザーは結果をより速く得ることが明確に示されています。

場合によっては、コアの数が増加しました。 明確にするために、第1世代および第2世代のインテル®Xeon®スケーラブルプロセッサーファミリーのいくつかのプロセッサーの比較表をまとめました。

| インテル®Xeon®シルバー4114

(10コア) | インテル®Xeon®シルバー4214

(12コア) | |

| クロック速度 | 2.20 GHz | 2.20 GHz |

| ターボモードで | 3.00 GHz | 3.20 GHz |

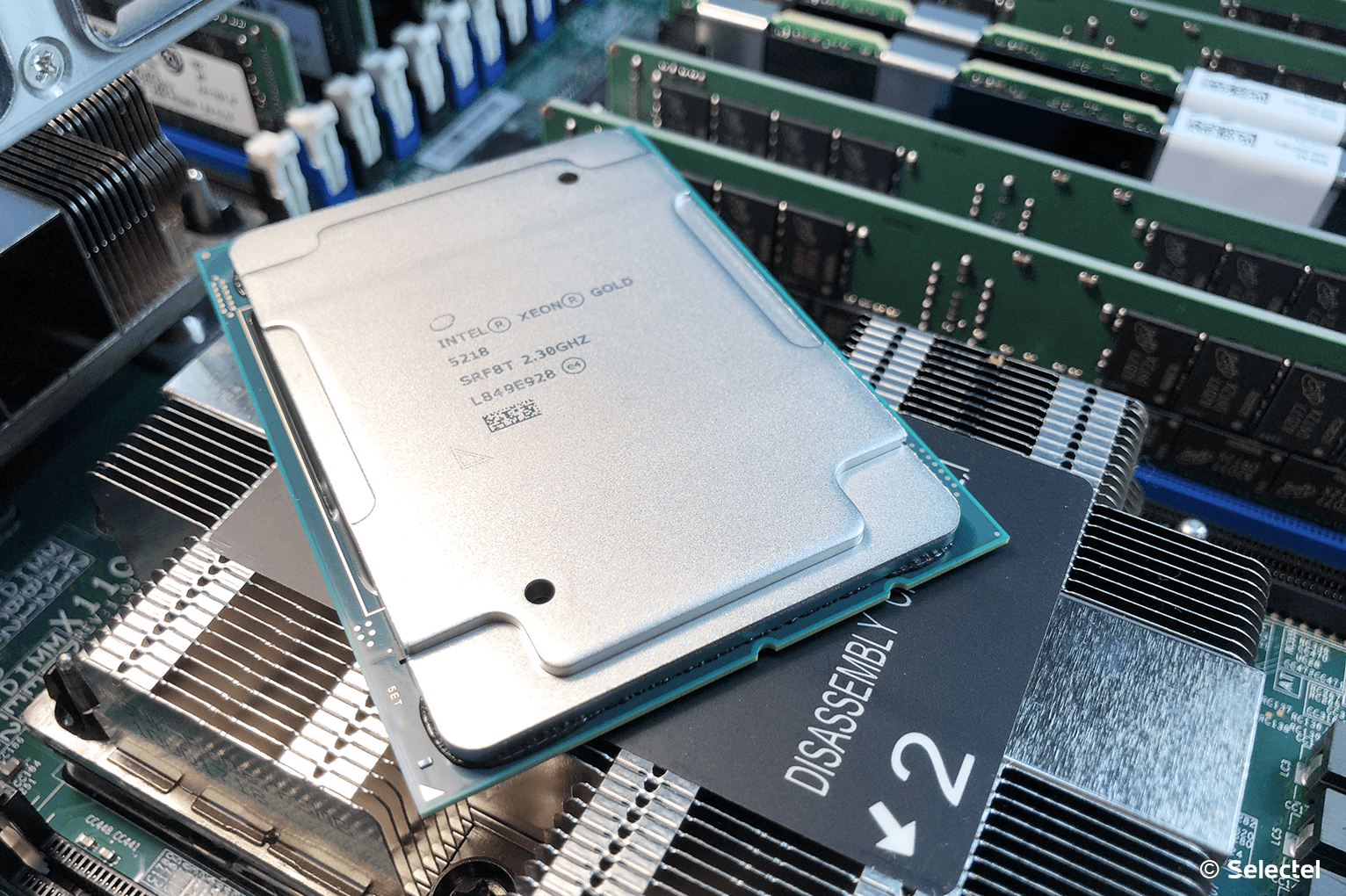

| インテル®Xeon®Gold 5118

(12コア) | インテル®Xeon®Gold 5218

(16コア) | |

| クロック速度 | 2.30 GHz | 2.30 GHz |

| ターボモードで | 3.20 GHz | 3.90 GHz |

| インテル®Xeon®Gold 6140

(18コア) | インテル®Xeon®ゴールド6240

(18コア) | |

| クロック速度 | 2.30 GHz | 2.60 GHz |

| ターボモードで | 3.70 GHz | 3.90 GHz |

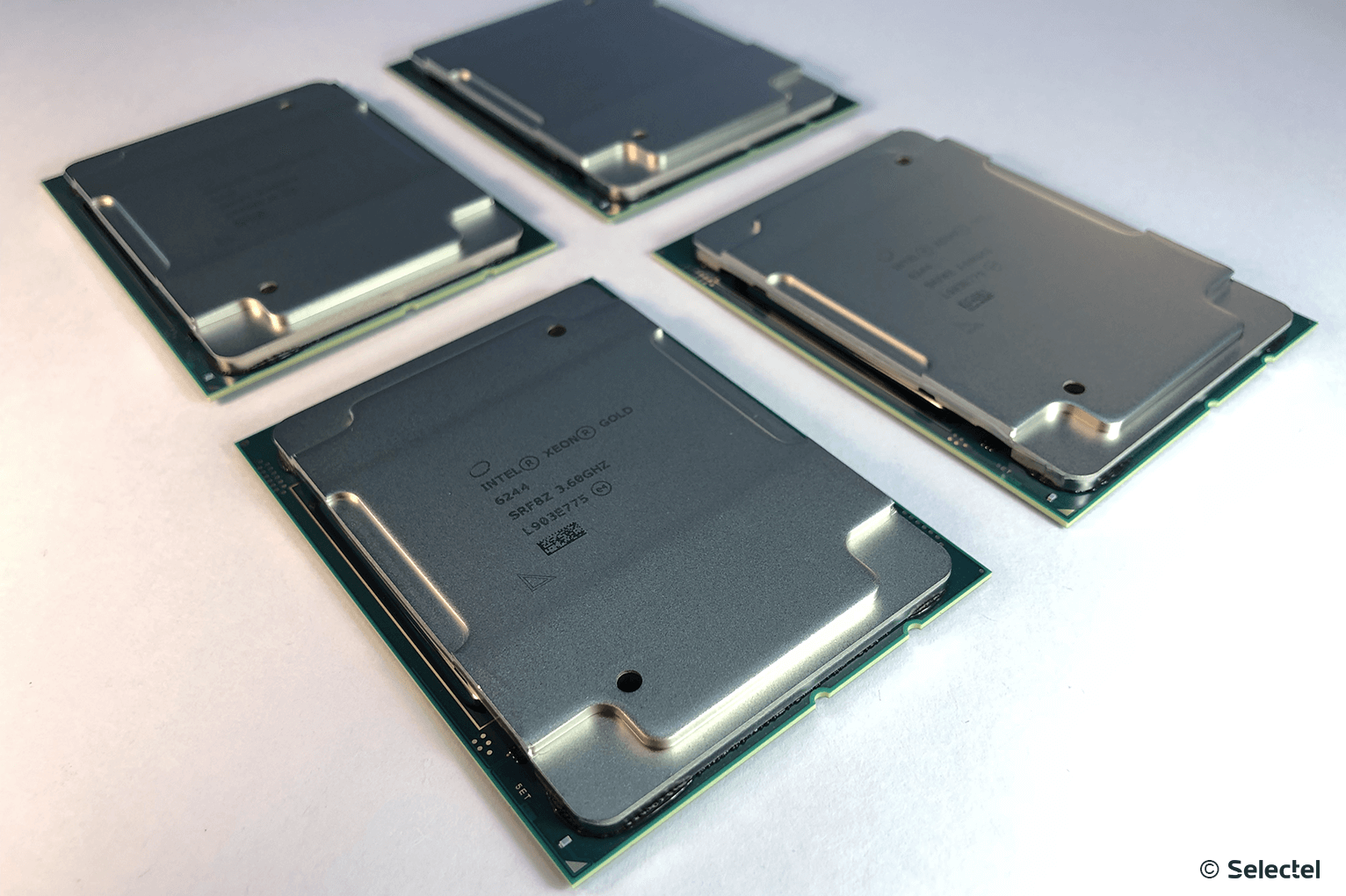

| インテル®Xeon®Gold 6144

(8コア) | インテル®Xeon®Gold 6244

(8コア) | |

| クロック速度 | 3.50 GHz | 3.60 GHz |

| ターボモードで | 4.20 GHz | 4.40 GHz |

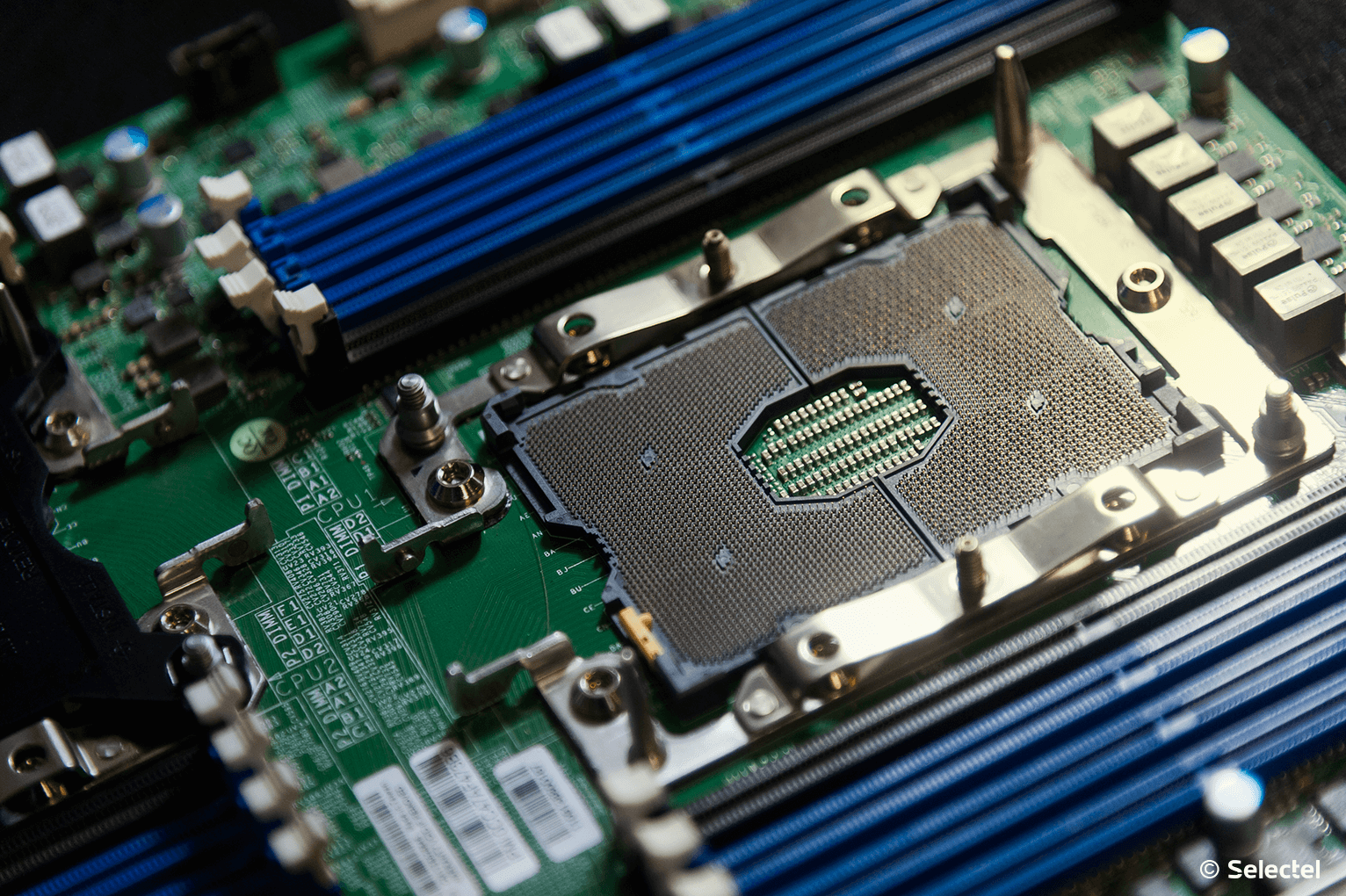

Skylake SPの前世代と同様に、プロセッサはLGA3647ソケット(ソケットP)にインストールされます。これは、6チャネルメモリコントローラー(チャネルごとに最大2つのメモリモジュール)の使用によるものです。 メモリ周波数は2666 MT / sですが、6000および8000シリーズのプロセッサを使用する場合、メモリは2933 MT / s (チャネルごとに1モジュール以下)で使用できます。

第1世代のIntel Xeon SPプロセッサで正常に使用されたUltra-Path Interconnectバスは、第2世代に残り、各チャネルで9.6 GT / sまたは10.4 GT / sの速度でプロセッサ間のデータ交換を提供しました。 これにより、ハードウェアプラットフォームを8つの物理プロセッサに効果的に拡張し、帯域幅とエネルギー効率を最適化できます。

テスト

私たちは、 SPECテストスイートを使用して新世代プロセッサのテストを開始しました。SPECテストスイートは、生命の最も重要なタスクのソリューションに基づいて負荷をシミュレートします。 これらのテストは、最も単純な計算と、分子物理学や流体力学の問題を解決するなど、さまざまな物理プロセスの計算の両方を表します。

現在、インテル®Xeon®Gold 6140およびインテル®Xeon®Gold 6240プロセッサーを例として使用した整数計算用のSPECテストの結果を用意しています。

積分する

| テスト | インテル®Xeon®Gold 6140 | インテル®Xeon®ゴールド6240 |

| 500.perlbench_r | 147 | 157 |

| 531.deepsjeng_r | 127 | 139 |

| 541.leela_r | 125 | 127 |

| 548.exchange2_r | 176 | 203 |

Intsepeed

| テスト | インテル®Xeon®Gold 6140 | インテル®Xeon®ゴールド6240 |

| 600.perlbench_s | 5.67 | 6.33 |

| 602.gcc_s | 6.95 | 8.74 |

| 641.leela_s | 3.24 | 3.62 |

| 648.exchange2_s | 5.94 | 7.90 |

テストの説明

- perlbench_rは、Perl言語の簡易バージョンです。 テスト負荷は、一般的なSpamAssassinスパム対策システムの動作を模倣しています。

- deepsjeng_r-チェスのゲームのシミュレーション。 サーバーは、アルファベータクリッピングアルゴリズムを使用して、ゲームポジションの詳細な調査を実行します。

- leela_r-囲 gameゲームのシミュレーション。 テストのプロセスでは、動作パターンの分析と、信頼限界の上限に基づいたツリー内の選択的検索があります。

- exchange2_r-自明でない数独パズルのジェネレータ。 Fortran 95で作成され、ほとんどの配列処理関数を使用します。

- gcc_s C言語コンパイラ:テストロードは、IA-32マイクロプロセッサアーキテクチャのソースコードからGCCコンパイラを「コンパイル」します。

テストの結果によると、新世代プロセッサは前世代よりも高速に整数計算を実行することが明らかになりました。 次のいずれかの記事で、他のテストの結果を共有します。

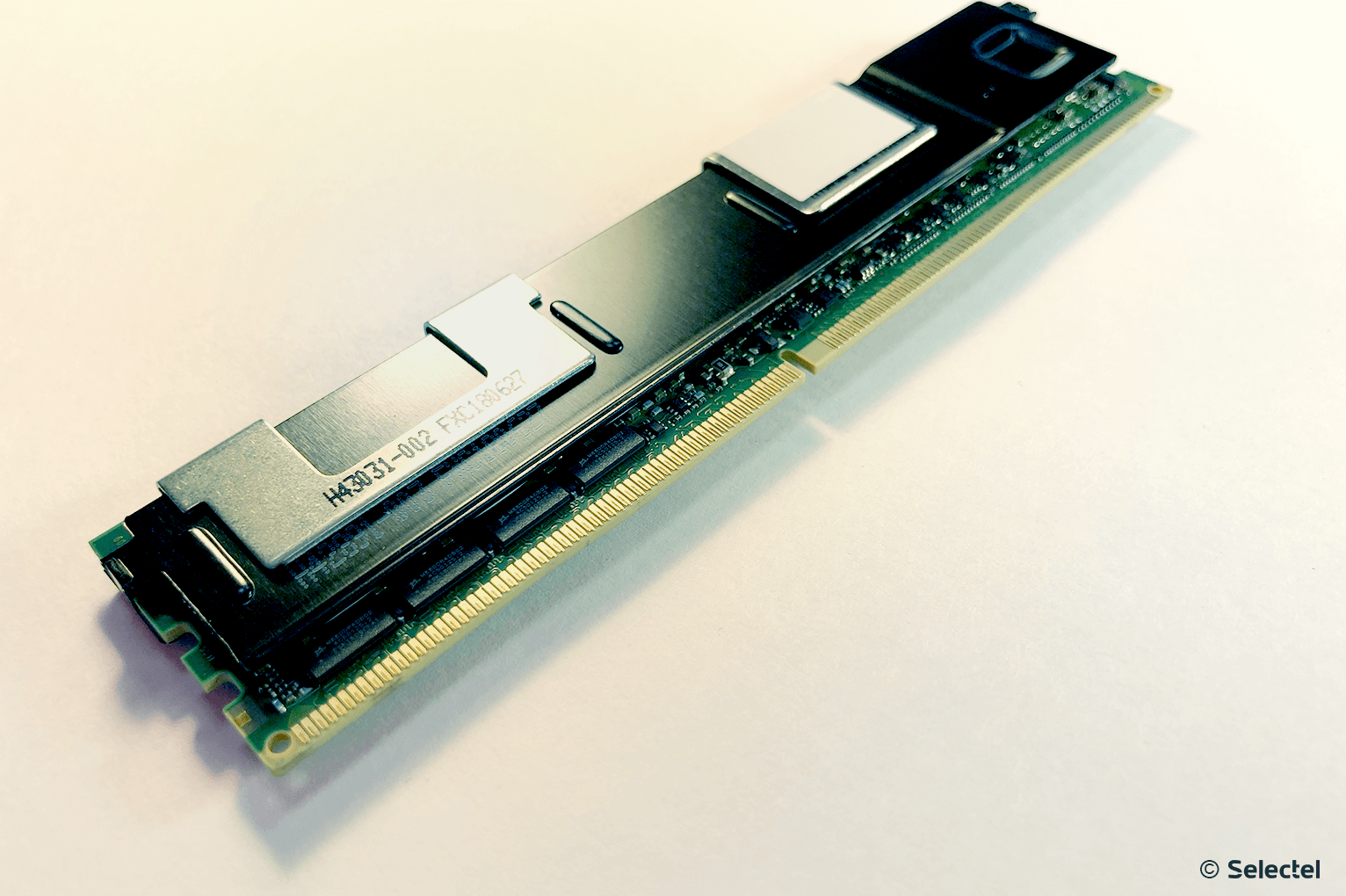

インテル®Optane™DC永続メモリのサポート

負荷の高いデータベースとアプリケーションのワークロードを加速する-これは、すべての顧客が次のアップデートから期待したことです。 したがって、重要な革新は、インテル®Optane™DC永続メモリのサポートであり、Apache Passというコード名でよく知られています。

このメモリは、適切な量のDRAMを使用することが経済的に不利であり、フラッグシップSSDでさえ十分に高速でない場合に、問題に対する普遍的なソリューションになるように設計されています。

鮮明な例は、データベースをIntel®Optane™DC Persistent Memoryに直接配置することです。これにより、RAMとストレージデバイス(従来のシステムに固有の機能)間のデータ交換を継続する必要がなくなります。

新しいタイプのメモリはDIMMスロットに直接取り付けられ、完全に互換性があります。 次のボリュームのモジュールが利用可能です。

- 128 GB

- 256 GB

- 512 GB

このような大量のモジュールを使用すると、ハードウェアプラットフォームを柔軟に構成でき、負荷の高いシステムに非常に大容量で非常に高速なディスクスペースを確保できます。 Intel®Optane™DC Persistent Memoryは、機械学習を含むアプリケーションに非常に大きな可能性を秘めています。

より高速なディープラーニング

Intelのエンジニアは、新しいタイプのメモリをサポートすることに加えて、ディープラーニングのプロセスを加速しました。 たたみ込みニューラルネットワークでは8ビット値と16ビット値の乗算が必要になることが多いため、新しいプロセッサはAVX-512 VNNI (Vector Neural Network Instructions)命令のサポートを受けました。 これにより、計算を数回最適化および高速化できます。

次の一連の指示を実装することにより、最高の効率が達成されます。

- VPDPBUSD (INT8計算用)、

- VPDPWSSD (INT16計算用)。

一番下の行は、サイクルごとに処理されるアイテムの数を減らすことです。 VPDPWSSD命令は、2つのINT16命令を組み合わせ、INT32定数を使用して、2つの現在の命令PMADDWDおよびVPADDDを置き換えます。 同様に、 VPDPUSB命令は、3つの既存の命令VPMADDUSBW 、 VPMADDWD、およびVPADDDを置き換えることにより、要素の数を減らします。

したがって、新しい命令セットを正しく適用すると、サイクルごとに処理される要素の数を2〜3倍減らし、データ処理の速度を上げることができます。 新しい命令の適切なフレームワークは、次のような一般的な機械学習ソフトウェアライブラリの一部になります。

負荷分散の最適化

Intel®Speed Select Technology(インデックスがYのプロセッサー)を使用すると、コンピューティングリソースの均等なロードが容易になります。 一番下の行は、各操作が関連するコアの数とクロック速度に関連付けられ始めるということです。 各操作で選択されたプロファイルに応じて、リソースは次のように割り当てられます。

- より多くのコアが、より低いクロック速度で。

- コアは少なくなりますが、クロック速度は向上します。

このアプローチにより、リソースを完全に活用できます。これは、仮想化環境を使用する場合に特に重要です。 これにより、仮想化ホストの負荷が最適化され、コストが削減されます。

科学計算の加速

特に粒子レベルで物理プロセスをモデリングする場合(たとえば、電磁相互作用の計算)、科学データを処理するには、膨大な量の並列計算が必要です。 この問題は、CPU、GPU、またはFPGAを使用して解決できます。

マルチコアCPUは、データ処理用のソフトウェアツールとライブラリが多数あるため汎用的です。 これらの目的でGPUを使用することも非常に効果的です。何千もの並列スレッドをハードウェアグラフィックコアで直接実行できるからです。 OpenCLやCUDAなど、開発に便利なフレームワークがあり、 GPUコンピューティングを使用して複雑なアプリケーションを作成できます。

それにもかかわらず、 以前の記事で既にお話しした別のハードウェアツール、FPGAがあります。 特定の計算を実行するようにそのようなデバイスをプログラムする機能により、データ処理を高速化して、CPUを部分的にオフロードできます。 同様のシナリオは、個別のIntel®Stratix®10 SX FPGAと組み合わせて、新しいCascade Lakeプロセッサに実装できます。

従来のCPUと比較してクロック速度が遅いにもかかわらず、FPGAは10倍高いパフォーマンスを発揮できます。 デジタル信号処理などの一部の種類のタスクでは、Intel®Stratix®10 SXは最大10 TFLOPS(1秒あたりのテラ浮動小数点演算)までの結果を表示できます。

プラットフォームのスケーリング

リアルタイムでビジネスを行うことは、安定性だけでなく、オンデマンドで拡張できることも意味します。 良い例は、データの保存と処理に使用される高性能SAP HANAプラットフォームです。 このプラットフォームを物理的に展開するには、非常に強力なハードウェアリソースが必要です。

インテル®Xeon®スケーラブルプロセッサーは、マルチソケットシステムをITインフラストラクチャのコア要素に変えるように設計されており、ビジネスアプリケーションの要求を満たすスケーラビリティを提供します。

これは、外部ノードコントローラーのサポートという形で実装されます。これにより、1つのプラットフォームが提供できるよりも高いレベルの構成を作成できます。 たとえば、いくつかのマルチソケットプラットフォームのリソースを1つの全体に結合することにより、32個の物理プロセッサの構成を作成できます。

おわりに

動作周波数とプロセッサコアの増加、生産性の向上、およびIntel®Optane™DC永続メモリのサポート-これらすべての改善により、各プラットフォームの計算能力が大幅に向上し、使用する機器のコストが削減され、データ処理効率が向上します。 アーキテクチャレベルで定められたスケーラビリティの原則により、複雑なITインフラストラクチャを構築し、高いパフォーマンスとエネルギー効率を実現できます。

SelectelはIntelプラチナパートナーであるため、お客様はカスタムサーバーで次世代Intel®Xeon®スケーラブルプロセッサを注文できます。

次世代プロセッサを搭載したサーバーを借りるのは簡単です! 構成ページに移動して 、必要なコンポーネントを選択するだけです。 コントロールパネルでチケットを作成することにより、サービスの運用に関するご質問はスペシャリストにお問い合わせいただけます。 数か月前からサーバーに支払うと、最大15%の割引を受けられます。

最新テクノロジーのテストに参加したい場合は、Selectel Labに参加してください。

コメントでご質問やご提案をお待ちしております。