サイプレスのドキュメントに基づいて、UDBの検討を続けています。 そして今回は、運用オートマトンであるDatapathについて詳しく説明します。

サイクルの一般的な内容「UDB。 これは何ですか?」

パート1.はじめに。 Pld。

パート2.データパス。 (現在の記事)

パート3.データパスFIFO。

パート4.データパスALU。

パート5.データパス。 有用なささいなこと。

パート6.管理およびステータスモジュール。

パート7.タイミングとリセット制御モジュール

パート8. UDBのアドレス指定

21.3.2運用マシン(データパス)

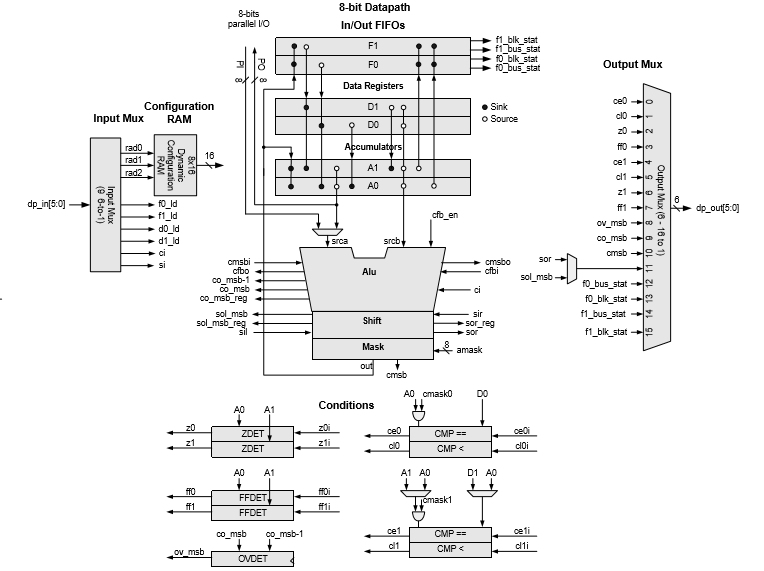

図21-6に示すデータパスには、条件フラグを比較および生成するための8ビットのシングルエンドALUとそれに関連する回路が含まれています。 隣接するUDBのデータパスブロックをチェーン化して、ビット深度を増やすことができます。 データパスには、特定のサイクルで実行する操作を動的に選択できる小さな動的構成RAMが含まれています。

データパスは、タイマー、カウンター、PWM、PRS、CRC、シフトレジスタ、デッドバンドジェネレーターなどの典型的な組み込み機能を実装するために最適化されています。 加算および減算関数を追加すると、デジタルデルタシグマ演算がサポートされます。

図21-6。 トップレベルのデータパス。

21.3.2.1概要

次の章では、データパスの主な機能の概要を説明します。

動的な構成

動的構成-シーケンサーの制御下で各サイクルでデータパスの作業と内部通信を変更する機能。 これは、8つの固有の構成を保存する構成メモリ(構成RAM)を使用して実装されます。 このメモリの入力アドレスは、トレースリソースに接続された任意のブロック、通常PLDロジック、I / Oピン、または他のデータパスから転送できます。

アル

ALUは、8つの汎用機能を実行できます。インクリメント、デクリメント、加算、減算、および論理演算AND、OR、XOR、およびPASSの実行です。 機能の選択は、各サイクルの構成メモリによって決まります。 独立したシフト操作(左、右、ニブル置換)、およびマスキング操作はALU出力で使用できます。

条件付き構造

各データパスには、複数のデータパスレジスタ入力を引数として選択するように構成できる2つのビットごとにマスクされたコンパレータがあります。 その他の検出可能な状態は、すべてゼロ、すべて1、およびオーバーフローです。 これらの条件は、データパスのメイン出力を形成し、デジタルトレースラインまたは他の機能の入力に転送できます。

埋め込みCRC / PRS

データパスには、特定のビット深度と生成多項式を使用して、シングルサイクルCRC計算と擬似ランダムシーケンス(英語の擬似ランダムシーケンス、PRS)の生成が組み込まれています。 8ビットを超えるビット深度を実現するために、データパス間で信号をチェーンできます。 この機能は動的に制御されます。つまり、他の機能と交互に切り替えることができます。

カスタム高ビット数

算術関数とシフト関数の最上位ビット(MSB)番号は、プログラムで設定できます。 これにより、可変長CRC / PRS機能がサポートされ、ALU出力のマスキングと組み合わせて、任意の長さのタイマー、カウンター、およびシフトブロックを実装できます。

FIFO入力/出力バッファ

各データパスには2つの4バイトFIFOバッファーがあり、それぞれが入力バッファー(CPUまたはDMAがFIFOにデータを書き込む、データパスがFIFOを読み取る)、または出力バッファー(データパスがFIFOに書き込む、およびCPUまたはDMA)として機能するように構成できますそれから読み取ります)。 これらのFIFOバッファーは、シーケンサー、割り込み、またはDMA要求と対話するために転送できるステータスを生成します。

連鎖

データパスは、隣接するデータパスにチェーン内の条件と信号をチェーンするように構成できます。 シフト、転送、キャプチャ、およびその他の条件付き信号をチェーンで組み合わせて、より高いビット深度の算術関数、およびシフト関数とCRC / PRS関数を作成できます。

時分割多重

オーバーサンプリングアプリケーションまたは高クロック速度が不要な場合、データパスの1つのALUを2セットのレジスタと条件ジェネレーターに効果的に分割できます。 ALUおよびシフトレジスタの出力はラッチされ、後続のサイクルで入力として使用できます。 使用例には、1つの(8ビット)データパスでの16ビット機能のサポート、またはデータシフト操作とCRC生成操作の交互実行が含まれます。

データパス入力

データパスには、構成、制御、およびデータ入力(シリアルおよびパラレル)の4種類の入力があります。 構成入力は、動的構成のRAMアドレスを選択します。 制御入力はFIFOからデータレジスタをロードし、バッテリー出力をFIFOにダウンロードします。 シリアルデータ入力には、シフトおよびキャリー入力が含まれます。 パラレルデータ入力ポートを使用すると、トレースリソースから最大8データビットを受信できます。

データパス出力

合計で、Datapathによって生成される16の信号があります。 それらの一部は条件付き信号(比較など)、その他はステータス信号(FIFOステータスなど)、残りはデータ信号(シフトレジスタ出力など)です。 これらの16の信号は、6つのデータパス出力に多重化され、トレースマトリックスにルーティングされます。 デフォルトでは、出力はクロック周波数に同期され、1クロックサイクルの遅延でパイプラインが作成されます。 また、それらは(出力)を非同期(組み合わせ)モードに切り替えることができます(翻訳者注を参照)。

翻訳者のメモ

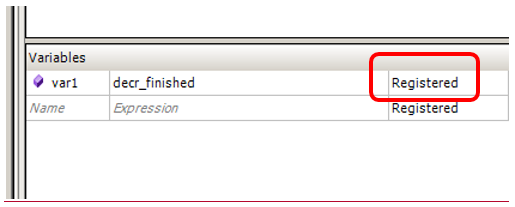

Datapath出力のタイミングが何であるかについて長い間検索しました。 私の経験では、すべてが非同期に存在すると言われています。 これは出力の状態ではなく、それらに基づく変数のこのエディター設定であることが判明しました。

これにより、エディターは次のVerilogコードを生成します。

/* ==================== Assignment of Registered Variables ==================== */ always @ (posedge clock) begin : register_assignments var1 <= (decr_finished); end

コンビナトリアルモードに切り替えた場合

コードは次のようになります。

assign var1 = (decr_finished);

ただし、これはすべて、データパス出力に基づいて生成された変数に適用されます。 また、出力自体は常に非同期です。 そして、それらの名前(この例ではdecr_finished )は、追加の変数を入力せずに使用できます。

データパス作業レジスタ

各データパスモジュールには、6つの8ビット作業レジスタがあります。 CPUまたはDMAには、すべてのレジスタへの読み取りおよび書き込みアクセスがあります。

表21-1

| 種類 | 名 | 説明 |

|---|---|---|

| バッテリー | A0、A1 | バッテリーはソースまたはレシーバーのいずれかです

ALUの場合。 データレジスタからロードすることもできます。 またはFIFO。 通常、バッテリーには現在の機能値が含まれています。 (例:カウンター、CRC、またはシフト)。 これらのレジスタは失われます スリープモードに入ったときとリセット時の値 値0x00。 |

| データ | D0、D1 | データレジスタには通常、関数定数が含まれています。

たとえば、PWM比較値、タイマー周期、CRC多項式など。 これらのレジスタは、スリープモードのときに値を保持します。 モード。 |

| FIFO | F0、F1 | 2つの4バイトFIFOバッファーがソースとして提供され、

バッファされたデータの受信者。 FIFOは 入力バッファー、出力バッファー、または1つとして構成 入力バッファと1つの出力バッファ。 状態信号ショー これらのバッファのステータスを読み書きします。 使用例へ SPIまたはUARTにバッファリングされたTXおよびRXデータを含めることができます。 バッファされたPWMデータとバッファされたデータ タイマー期間について。 これらのレジスタは値を保存しません。 スリープモードおよびリセット中は、値0x00を取ります。 |

次の記事では、FIFOの取り扱いを開始します。