はじめに

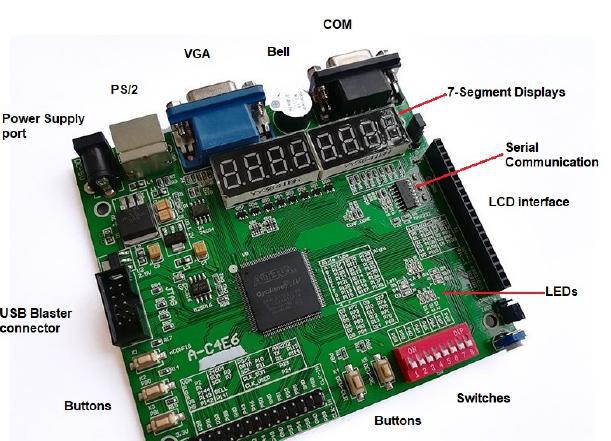

私たちはイノポリス大学でコンピューターサイエンスを学ぶ最初の1年生であり、FPGAボードでこれまでで最もクールな(少なくとも、最も大きな)ロータリーエンコーダーを作成するためのVerilogプログラムの開発経験を共有したいと思います。

この記事では、プロジェクト、使用したハードウェア、ソフトウェア、およびロータリーエンコーダーとFPGAブザーでのサウンドの作成に関するいくつかの背景理論についての素晴らしいストーリーを見つけることができます。 最後に、読者がソースコードにアクセスできるgithubリポジトリへのリンクを提供します。 あなたがこのプロジェクトを気に入ってくれて、それが似たようなものを作るきっかけになることを願っています。

それでは、始めましょう!

ハードウェアとソフトウェア

- Quartus PrimeのCyclone IV FPGAデバイスのサポート

- Quartus Prime Liteエディション

- Arduinoキットのロータリーエンコーダー

- ModelSim * -Intel FPGA(デバッグ専用)

- Arduinoキットのワイヤ

簡単な話

ずいぶん昔、遠くの銀河で、学生たち(私たち)がハードウェアに近づくことを決めました。 コンピューターアーキテクチャコースは、FPGAボードでプロジェクトを作成する素晴らしい機会を与えてくれました。 いくつかの議論の後、ロータリーエンコーダを備えたシステムを実装することにしました。 私たちはタスクを達成しましたが、欲求を満たすのに十分ではなかったので、キーボードとボードのブザーを使用して異なるノートを演奏する楽器に変えてプロジェクトをアップグレードすることにしました。 しかし、FPGAのPS / 2ポートは機能していません。

最終的に、ボタンが押されたときに再生される単純なメロディを書くことになります。

オルゴール

音波の周波数によって音を区別できます。 したがって、ブザーに異なる音を鳴らすには、異なる周波数の音波を生成する必要があります。

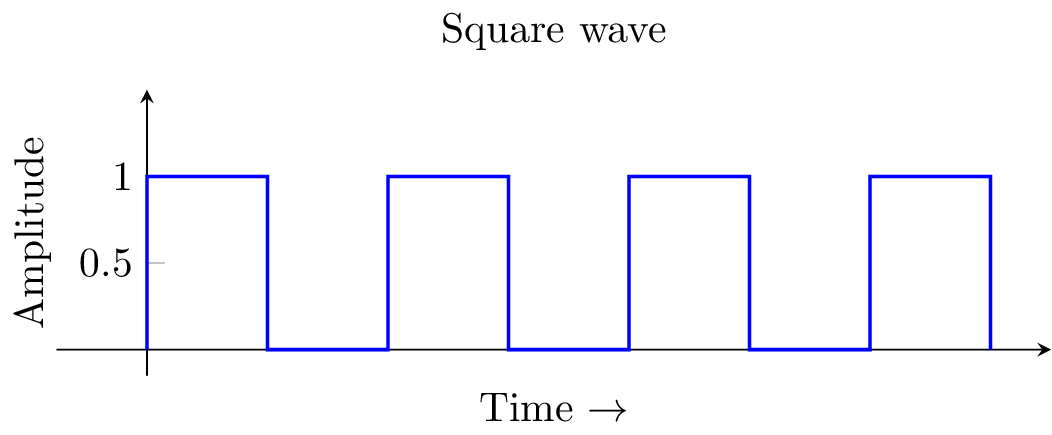

方形波は実装が非常に簡単なので、矩形波を使用することにしました。

方形波は、高と低の間で状態を変える信号です。 方形波の主な考え方は、High状態の信号とLow状態の信号が同じ時間になるということです。 方形波を生成するには、I / Oをオンにし、x時間待機し、I / Oをオフにし、x時間から待機し、必要な回数だけこれらのアクションを繰り返す必要があります。

この写真はここから撮りました 。

Cyclone IVには、周波数50 MHzのクロックジェネレータがあります。 方形波の定義を使用すると、次の式を導き出すのはそれほど難しくありません。

x =(50 * 10 ^ 6)/(2 * n )

ここで、 nはHz単位の目的の周波数、 xは状態を高から低、またはその逆に変更する前に待機する必要があるクロックサイクル数です。

ブザーで周波数n Hzの波を生成するには、クロック分周器を実装しました。

クロック分周器と方形波の詳細については、 こちらをご覧ください 。

別のしかし :

ブザーの音質が低いため、低周波数で音を鳴らすことはできません。 そのため、4オクターブのF#から5オクターブのC#までのものを使用しました。

オルゴールのロジックを示すフローチャートです。

ロータリーエンコーダー

ロータリーエンコーダーはどのように機能しますか?

導体板と2つのアナログセンサーを備えた円でできているものです。

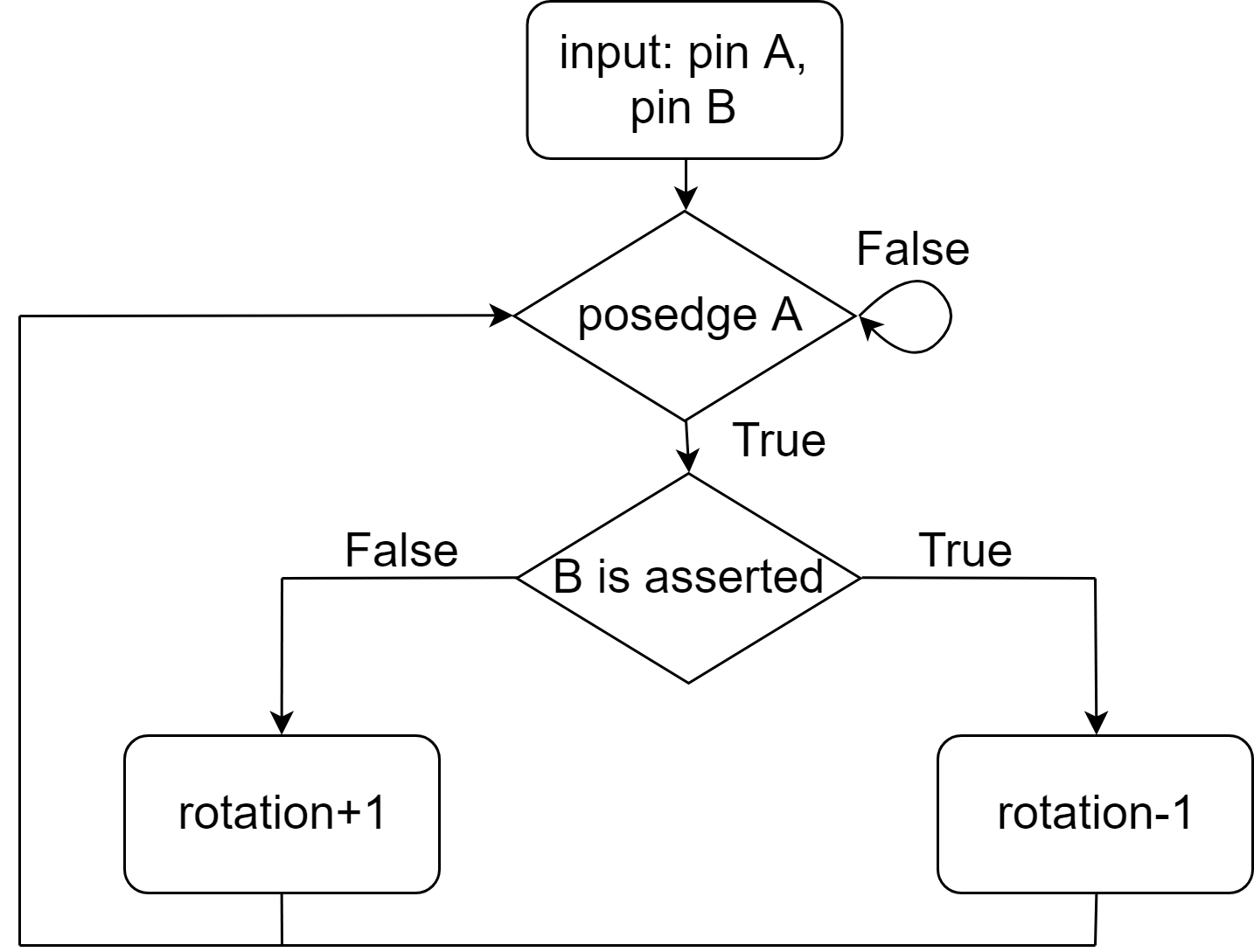

ロータリーエンコーダーを回すと写真からわかるように、センサーの1つが最初にプレートに触れ、低から高になります。 そのため、エンコーダーを時計回りに回しているか反時計回りに回しているかを知ることができます。 アイデアは次のとおりです。センサーAがローからハイに変わるたびにセンサーBを確認します。 その時点でBがアサートされている場合、エンコーダーは時計回りに回され、そうでない場合は反時計回りに回されました。 ここで、回転という言葉は、エンコーダーを1つのセクションでオンにすることを意味します。

(写真はhowtomechatronics.comから盗まれました )

ロータリーエンコーダーのロジックを示すフローチャートです

また、回転角度を8セグメントディスプレイに出力します。 エンコーダには20のセグメントがあるため、1つのセグメントの回転は18の角度の回転に等しく、使用する式は次のとおりです。

角度 =( 回転数 mod 20)* 18

素材

プロジェクトのコードはこちらです。

こちらとこちらがロータリーエンコーダーとオルゴールのビデオです。

著者 :アミナ・ミフタホワ、カミル・カマリエフ、レフ・スバロフ。