信頼できる高速ストレージをお探しですか? StoreQuantソリューションを使用する

ストレージシステム(SHD)は、ビジネスをサポートすることを目的としたシステムなど、現代のITシステムの重要な要素です。 外国企業は、ビジネスクリティカルシステムまたはミッションクリティカルシステムなどのシステムを表す用語を作成しました。

実際、データの処理と保管は重要なタスクです。ストレージシステムの運用におけるデータの損失や短期的な誤動作は、ビジネス全体に重大な結果をもたらす可能性があるためです。

ビジネスクリティカルという用語は、この分野で働く多くの専門家にとって直感的に明確であるため、ロシア語に翻訳しませんが、私たちの仕事は、ストレージの基本をより多くの人々に理解してもらうことです。 したがって、ストレージという用語を参照する場合、ビジネスクリティカルストレージを意味します。理解する限り、ストレージは必ず多くの機能を実行し、ビジネスクリティカルという用語で正確に定められた必要な要件を実装する必要があります。

この記事では、ストレージシステムのアーキテクチャ、その機能、および外国ベンダーの競合ソリューションに対する利点について説明します。

ストレージシステムを使用している多くのお客様の経験と同様に、StoreQuantのロシア特許取得済みストレージテクノロジーを使用して実際の問題を解決する方法の典型的な例をさらに見ていきます。

顧客は何を購入し、市場には選択肢がありますか?

市場を分析し、ストレージシステムで満たす必要のある多くの要件を策定しました。 残念ながら、現在ロシアの外国のストレージソリューションの購入者は、ストレージメーカーの助けを借りて製品の開発に影響を与えたり、ニーズに合わせて製品を適応させることはできません。

最新のストレージシステムの主な要件:

- ストレージは24時間365日動作し、サービスを停止することなくアップグレードをサポートする必要があります。

- ストレージシステムでは、メディア障害が発生した場合にユーザーの介入なしにデータ回復テクノロジーを実装する必要があります。

- ストレージアーキテクチャに単一障害点がないようにする必要があります。

- ストレージは、アプリケーション自体の構成を変更せずに、アプリケーション側の負荷に適応する必要があります。

- ストレージには、データアクセスプロトコルのレベルで自己診断機能を含める必要があります。

ストレージエラーの大部分は、ソフトウェアエラーが原因で発生するか、データアクセスプロトコルのレベルでの非互換性が原因で発生します。

これらの原則に従って、製品を作成し、顧客の問題を解決します。

ストレージとは何ですか?

現在、ストレージシステムのメーカーにはさまざまなオンラインコースがあり、その中でストレージシステムの管理方法とその機能について説明しますが、実際にどのように機能するかについての主なことは説明しません。

SHDは、ハードウェアとソフトウェアの複合体です(英語の用語では、アプライアンス)。 ストレージシステムの開発は、ソフトウェアによって非常に決定され、実際には多くのベンダーによって「マイクロコード」と呼ばれています。 ソフトウェアは、ストレージのほぼすべての重要な要素を実装します。これは、ハードウェアストレージの開発を節約できるため、有能な技術的アプローチです。 私たちの理解では、ソフトウェア定義ストレージ(SDS)という用語は正しくありません。ストレージに純粋にソフトウェアを実装することはできないため、SDSのどのバージョンも何らかの形でハードウェアに関連し、それに依存します。

最初に、ストレージシステムを開発する際に遵守するいくつかの原則を導入しました。

- データ管理にオープンソースツールを使用しないでください。

- ストレージシステムの特別な重要機能を除き、ハードウェアプラットフォームのアーキテクチャに依存しないでください。

- 重要な領域を除き、低レベル(カーネル)でプログラムしないでください。

ストレージの分野でソリューションを開発する多くの先駆者は、インターネット上でデータを管理するために十分に宣伝されたオープンソースパッケージを取得するだけで十分であり、以前は安価なサーバーを使用していた問題を解決できると単純に信じています。 ストレージ分野のオープンソースソリューションは、まったく異なる目的のために作者によって作成されたものであり、ストレージを非常に慎重に作成するために使用する必要があると推測するのは簡単です。

ストレージは、単一の適切に機能するメカニズムとして機能するシステムであり、さまざまな著者の作品から組み立てるのは難しく、費用がかかります。

また、顧客データのセキュリティと整合性を誰が保証しますか?

ストレージなどの複雑なシステムでデータ管理をオープンソースソリューションに任せることは非常に危険です。

外国のストレージベンダーがこの問題を解決するのにどのように適しているかを分析した後、オープンソースコンポーネントを使用せずに独自のストレージコアを開発しました。

ストレージの主要な要素を特定しました。これについては、この記事で説明します。

ストレージを構築する理由

将来、この問題の多くの側面をカバーしますが、主な理由を定式化します。

- ストレージのリーダーになることは、ストレージを作成することを意味します。 消費者になることは、他の人のソリューションを購入することです。

- 既存のアプリケーションへの適応が難しいロシアのDBMSなどとは異なり、ストレージはITランドスケープに簡単に統合できます。

- データ処理および伝送技術で使用されるマイクロチップの大規模な品揃えにより、新しいユニークなストレージソリューションを迅速に設計できます。

- 深刻なデータセキュリティは、国内のソリューションでのみ確保できます。

将来の記事では、データ処理およびストレージアルゴリズムを実装するための興味深い方法と、エンジニアリングソリューションだけを紹介する予定です。

ストレージの未来はありますか?

間違いなく、ストレージシステムには未来があります。現代のコンピューターのアーキテクチャでは、RAMに大量のデータを継続的に格納できないためです。

新しいインメモリDBMSが出現しても、上記の理由でストレージがキャンセルされることはありません。

NVMeキャリアに基づいてロシア市場で初めてストレージを実装し、StoreQuant Velocity Scaleラインでソリューションを発表したのはこのためです。 この製品はNVMe標準に基づくロシア初のストレージシステムであり、外国のアナログ製品と自信を持って競合し、あらゆるクライアントのSANインフラストラクチャに簡単に統合できます。

次に、アーキテクチャ、製品、ソリューションについて説明します。

StoreQuant Velocity Scaleストレージではどのアーキテクチャを使用していますか?

StoreQuantストレージアーキテクチャの主要な要素は、トランザクション処理メカニズムに基づいてデータの安全性を保証するインメモリ DBMSです。

ストレージシステムでの書き込みまたは読み取りデータコマンドの処理に関連する操作は、ACID(原子性、一貫性、分離、耐久性)の概念に準拠する必要があります。 DBMSストレージはブロックデータのストレージに基づいており、オブジェクトデータベースとして分類できます。 DBMSのタスクは、複数のコントローラーのメモリ内のデータのフォールトトレラントな処理でもあります。 DBMSがRAMにデータを保存するために使用するメモリ領域は、キャッシュと呼ばれます。

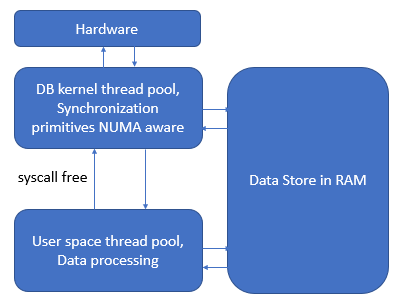

キャッシュを積極的に使用して、I / Oを高速化します。 すべての操作は、主にストレージコントローラーのRAMメモリに保存されます。 キャッシュという用語では、RAM内のデータの処理だけでなく、RAMとHDDストレージメディア間のデータの移動を制御するアルゴリズムも理解しています。 ストレージシステムソフトウェアパッケージのブロック図を図1に示します。

図1.ストレージプログラムコードのブロック図

Cacheでのデータ処理とデータ同期アルゴリズムを組み合わせることで、物理的な機器障害が発生した場合の同時同期データ複製と可用性を提供します。 ACIDコンセプトにより、すべてのコマンドがストレージシステム内で実行されることが保証されます。 DBMSコンポーネントのブロック図を図2に示します。

図2. DBMSコンポーネントの構造図

なぜ高性能のスケーラブルリンクスイッチが必要なのですか?

コード名「URSUS」を指定した高性能スケーラブルリンクスイッチの特別なコンポーネントにより、syscall(syscall freeスキームで)を使用せずにユーザー空間とカーネル空間の間で呼び出しを行うことができます。 URSUSでは、HBAアダプター、RAIDグループ、外部ストレージコントローラーを操作する際に、ハードウェアプラットフォームの実装の機能を無視できます。 URSUS SDKを実装するために、ブロックデータストレージの問題を解決できるさまざまなプリミティブとデータ構造をサポートするために、C ++とC ++のテンプレートライブラリを使用しました。 開発を加速するために、SDKを作成しました。これにより、情報のエンコード、重複排除、圧縮など、さまざまな情報処理機能を実装するための独自のモジュールを作成できます。

24時間365日のマイクロコードストレージの更新を保証する方法

URSUSを使用すると、I / Oを停止することなく、ユーザー空間でオンラインで実行されるストレージソフトウェアモジュールを更新できます。 URSUSレイヤーのコアでは、標準のオペレーティングシステムメカニズムを使用せず、キャッシュ内のデータに直接アクセスするため、ゼロコピーデータ処理メカニズムを使用します。 OSカーネルの異なる構造間でデータが複数回コピーされるLinuxのブロックレイヤーレベルとは異なり、コマンドの処理に時間を浪費せず、これによりストレージシステムでのI / O操作の待ち時間が短縮されます。

外国のストレージベンダーよりも優れている点は何ですか?

開発パートナーは、外国ベンダーのストレージキットを使用して、次のすべての欠点を受け取ります。

- パートナーは、複雑でアクセスできないプロセッサー技術に基づいた独自のコントローラーに完全に依存しています。 結果として生じるソリューションは、ハードウェアプラットフォームのライフサイクルに完全に依存します。

- 特に、主に外国ベンダーのシステムで使用される複雑なFPGA回路による、開発中および運用中のベンダーの技術サポートへの完全な依存。

- 開発プロセス中に、外国ベンダーのテクニカルサポートに相談する際には、決定のソースコードを開示する必要があるため、知的財産の保護の保証はありません。

URSUS SDKの利点は、パートナーに保証する次の機能です。

- URSUS SDKアーキテクチャにより、24時間365日の動作モードを備えた本格的なストレージシステムを構築できます。

- 開発チームは、ストレージシステムを作成する資格がありません。 LinuxおよびC / C ++用のプログラムを開発するスキルがあれば十分です。 有資格者を見つけるのに問題はありません。

- 独自のストレージソリューションを作成するためのハードウェアプラットフォームを自由に選択できます。

- SDKコードを任意のアーキテクチャ、特にARM、Elbrusに移植する機能

- 他のソリューション、特にLIO、SCSTなどのオープンソースソリューションと比較して、URSUS SDKに基づく高速開発。 その結果、パートナーは既製のソリューションを使用して市場に早く参入できるようになります。

- ソリューションのソースコードが利用できると、さまざまなセキュリティ標準のソリューションの認証が簡単になります。

私たちのOSでは、Vanilla KernelsアーカイブのLinuxカーネルの安定バージョンのみを使用しています。

開発者キットの説明は、当社のWebサイトのリンクにあります。

StoreQuant Velocity ScaleストレージでRAIDはどのように編成されていますか?

StoreQuantストレージのプライマリストレージ要素はRAIDグループです。

表1にリストされているさまざまなRAIDグループ構成があります。

表1-RAIDグループ構成

| RAIDタイプ | 4枚 | 16枚 | 64枚 | 128枚 | 256枚のディスク |

|---|---|---|---|---|---|

| RAID10 | 2D + 2D | 8D + 8D | 32D + 32D | 64D + 64D | 128D + 128D |

| RAID50 | 3D + 1P | 12D + 4P | 48D + 16P | 96D + 32P | 192D + 64P |

| RAID60 | 2D + 2P | 8D + 8P | 32D + 32P | 64D + 64P | 128D + 128P |

パリティデータは、ディスクの障害(3D + 1Pなど)がRAIDの動作やデータの可用性に影響を与えないように、ラウンドロビン方式に従ってディスクグループ全体に分散されます。

常に4つのディスクのRAIDグループ(基本グループ)に焦点を当て、これを使用して、より複雑なRAID構成をより多くのディスクにアセンブルできます。 たとえば、24D + 8P構成の32個のディスクのグループは、3D + 1P構成の8つのRAIDグループで構成されます。 パリティは、4つのディスクの基本グループの一部として計算されます。これにより、ディスクの負荷を大幅に分散し、入出力の速度を上げることができます。

Unite and Conquerアプローチを使用します

「Unite and Conquer」と呼ばれるアプローチを使用すると、クライアントはストレージシステムに少なくとも4つのディスクを一度に追加してRAIDグループを構成できますが、個別に使用するか、既存のRAIDグループに追加するかを決定できます。 表1に示す8、16、32などの区分。 ドライブは純粋に任意であり、4台のドライブの最小RAIDグループでも組み合わせを実行できますが、単一のRAIDグループ内で256台を超えるドライブは実行できません。

表2の以下のモデルのSSDのNVMeプロトコルをソフトウェアに統合したため、各ディスクのライフサイクルを個別に管理し、そのステータス、可用性、マイクロコードの更新などを制御しました。

現時点では、バージョン1.2までのNVMeプロトコルをサポートしています。

表2-NVMeプロトコルに基づいたStoreQuantストレージディスクの利用可能なモデル

| 駆動モデル | フォームファクター | データ量、TB |

|---|---|---|

| StoreQuant DataFusion 500 | 2.5インチ/ U.2 | 2 |

| StoreQuant DataFusion 550 | 2.5インチ/ U.2 | 3.6 |

| StoreQuant DataFusion 600 | 2.5インチ/ U.2 | 4 |

| StoreQuant DataFusion 650 | 2.5インチ/ U.2 | 8 |

| StoreQuant DataFusion 700 | 2.5インチ/ U.2 | 11 |

StoreQuantストレージでバックエンドが必要なのはなぜですか?

ストレージシステムの主なエンジニアリング上の問題は、ストレージシステム内でのデータ交換のための生産的で耐障害性のあるチャネルを作成することです。 I / O操作はストレージシステム内で多くの操作を生成するため、最小限のレイテンシでデータを転送するにはバスを使用する必要があります。

入出力操作について説明すると、ストレージシステムには基本的に1つのアトミック操作があります。データの変更には、データのプリフェッチ(読み取り)とそれに続くディスクへの変更の記録が含まれます。 転送されるデータの量とRAIDの種類に応じて、変更されたデータを書き込むと、RAIDグループの一部である各ディスクに対して多くの内部I / O操作が生成されます。

Intel Non-Transparent Bridgeとは何ですか?

このアーキテクチャでは、Intel Non-Transparent Bridge(NTB)テクノロジを積極的に使用しています。これにより、組み込みのプロセッサ機能を使用して、PCI Expressバスを使用して外部プロセッサシステムとやり取りできます。

ロシア市場で独自のインテルNTBベースのソリューションの発売に努めています。現在、光マルチモードケーブルを使用して最大100メートルの距離で任意の2つのインテルシステム間のネットワーク接続を作成するための既製のアダプターがあります。

ストレージコントローラー間でデータを同期するためにInfiniBandまたはイーサネットプロトコルを使用しないことが重要です。これにより、タスクに十分な最小レイテンシとPCI Expressバス帯域幅を取得できます。

Intel NTBの結果が許可するものを理解するために、そのテストの定量データ(RAM内のデータを同期するためのピンポン)を提供します:2つの8Kbストレージコントローラー間でx16 PCIeリンクを介してデータを転送すると、 10 115 MB / s ( 0.81μs(マイクロ秒)の平均遅延を持つメガバイト/秒)。

なぜファイバーチャネルインフラストラクチャを使用する必要があるのですか?

ただし、ほとんどのお客様はファイバーチャネル(FC)テクノロジーとFCインフラストラクチャに大量の機器を使用しているため、StoreQuant Velocity Scaleストレージシステムでバックエンドバスを編成するためのFCプロトコルもサポートしています。 HBAアダプターのほとんどのベンダーのFCプロトコルの実装は、ストレージシステムを開発する際のコストを大幅に削減できることに注意する必要があります。 私たちの戦略は、StoreQuant Velocity Scaleでバックエンドバスの少なくとも2つの標準をサポートすることです。

ストレージにデータを転送するためのプロトコルを選択するときは、メモリの量(メモリはマルチチャネルであるためDIMMの数)、メモリの種類(周波数と速度)、およびCPU能力に依存するRAM帯域幅を考慮する必要があります。

バスのバックエンドの組織にInfinibandインフラストラクチャを選択すべきではないのはなぜですか?

Intelベースのプラットフォームのさまざまなバージョンをテストすると、実際には、Intel Xeon E5 v3を搭載した標準のデュアルソケットマシンでのDDR3 RAMの平均スループットは20GB / s(ギガバイト/秒)以下であるため、プラットフォームの上限速度はプラットフォームメーカーによって既に設定されています。

Intelアーキテクチャで最も広く使用されているのは、PCI Expressデータバスです。 PCI Express v3.0バスの機能に基づいて、データスループットの下限が得られますが、どのプロトコルを使用するのが適切かという疑問が生じます。 100Gb / s以上の転送速度を備えたPCI Express v3.0に基づくアダプターを提供する市場のさまざまな企業のマーケティングの動きを考慮すると、少なくともIntelベースのプラットフォームの標準機器では、そのような速度を達成することは困難であることがわかります-理由上記のように。

いずれにせよ、PCI Express v4.0標準の準備が整い、可能性が大幅に拡大しているため、状況は改善されます。

標準PCIエクスプレスプロトコルを介したInfinibandアドオンは、余分なオーバーヘッドを追加します-データスループットを削減し、レイテンシを増加させます。

さらに、SCSIプロトコルに基づいた論理レベルのデータ転送がある限り、Infinibandプロトコルに基づく開発コストはファイバーチャネルに比べて非常に高くなります。

バックエンドストレージバスにはどのプロトコルを選択する必要がありますか?

Non-Transparent Bridgeを使用すると、顧客にとってより大きな機会が生まれ、ITインフラストラクチャのコストが大幅に削減されることを理解しています。

データ転送プロトコルまたはプロトコルの完成した実装のいずれかを選択した場合、オプションは販売および実装の段階で間違いなく安くなるため、コントローラー間のパケット交換をサポートする独自のプロトコルを開発しました。

その結果、次の利点が得られました。

- 私たち自身がプロトコルの開発戦略を決定し、サードパーティの外国メーカーの製造アダプター(ファームウェア)の実装と微妙さに依存していません。

- 市販されている他の高速規格と比較して、プロトコルのはるかに安価なバージョンを作成しました。 したがって、より良いオファーをお客様に提供するという点で、当社はより競争力があります。

次の記事では、Intel NTBに基づいた新しいStoreQuant製品とその使用方法について説明します。

StoreQuantストレージのリソースをどのようにスケーリングしますか?

負荷の増加に伴うストレージのスケーリング、およびQuality of Service(以下QoS)ポリシーの順守は、どのクライアントにとっても重要なタスクです。 私たちの調査によると、多くの外国ベンダーは、ストレージ負荷が増加した場合に追加の財政投資をせずに重要なアプリケーションを明確に保護するのに役立つQoS機能を備えていません。

QoSの用語では、外国のベンダーでは利用できない次の機能を使用しています。

- 特定のアプリケーションのキャッシュを保護する機能。 クライアント自身がCacheのボリュームを設定します。これにより、アプリケーションで使用できることが保証されます。

- 特定のボリュームの特定のアプリケーションに対して、RAIDグループレベルでデータチャネル幅を割り当てる機能。

- I / Oポートレベルでデータへの外部アクセスのバランスをとる機能。

- I / Oポートの仮想WWNベースのデータアクセス。

ストレージの基本的なアーキテクチャ要素は、Intel Xeon用の2つのソケット、NVMeディスク用のスイッチを搭載したコントローラーです。また、キャッシュでアクティブに使用する「ウィング」の下で最大1,500 MBのRAMを搭載できます。 コントローラーの高さは2ユニットまたは1ユニットで、標準ラックに取り付けるように設計されています。 コントローラには、NVMeディスクをインストールするための10〜24のスロットが含まれています。

例:2TBドライブを使用する単一の2ユニットコントローラー内の保存データの最大未処理容量は48 TBです。

StoreQuantの既製のオファーの例、および可能な製品構成は、 こちらの Webサイトで見つけることができます 。

1つのコントローラーには、最大4つの外部(フロントエンド)および2つの内部(バックエンド)I / Oポートがあり、特に16 Gb / sおよび32 Gb / sでFCをサポートします。

表3-StoreQuantストレージコントローラーの仕様

| StoreQuantストレージコントローラータイプ | I / Oポート(BE / FE) | データ量(最小/最大) | RAM容量(キャッシュ) |

|---|---|---|---|

| DataFusion SmartNode v1.0 | 2/4 | 1.6TB / 110 TB | 1,500 MB |

データ保護の観点からは、常にペアのコントローラーにデータの同期コピーを実装しています。 したがって、データは2つのコントローラーのメモリに格納され、ハードウェアレベルでの障害に対する保護が保証されます。

スプリットブレインの状況が発生した場合の保護のために、データ転送専用の回線がいくつかあるバックエンドバスを使用します。

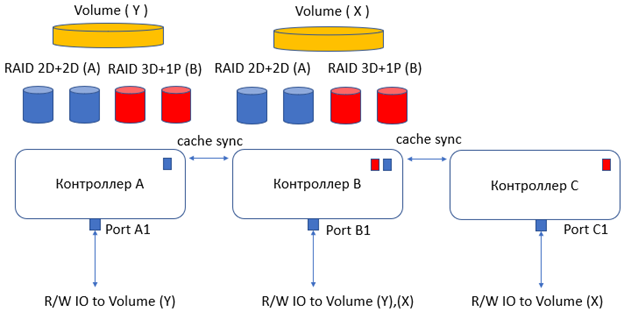

このアーキテクチャの特徴は、ストレージ管理システムのレベルでコントローラーを組み合わせることができることです。したがって、コントローラーレベルで1 + 1の保護を提供し、クライアントがサーバーから専用の入力/出力ポートにトラフィックを転送し、コントローラー間で負荷を共有できるようにします。 したがって、コントローラーは常に別のコントローラーと連携して動作し(以下、ベースモジュールと呼びます)、ストレージシステムの一部として単一の複合体を表します。 現時点では、ストレージソリューションの一部として512ベースモジュールのみをサポートしています。 512個のベースモジュールすべての動作を考慮した最大の技術的能力を表4に示します。

表4-最大構成のStoreQuantストレージ仕様

| フロントエンドのI / Oポート(FC)の数 | キャッシュの数(最大) | 最大データ量 |

|---|---|---|

| 4096 | 1536 TB | 112 640 TB |

ストレージのアップグレードの観点から、クライアントは少なくとも1つのコントローラーをインストールし、ストレージ構造に含めることができます。 図 図3は、クライアントが追加のコントローラーCをインストールした場合の3つのコントローラーのストレージの例を示しています。これにより、追加の入出力ポートによりストレージシステム全体のIOPS(入出力操作)の量を増やすことができます。 この場合、コントローラーBはコントローラーAおよびコントローラーCと2つのペア(基本モジュール)を形成し、すべてのデータ書き込み操作は、すべてのコントローラーのキャッシュ内のデータの同期コピーによって保護されます。 クライアントはコントローラーCを使用して、アプリケーションのボリューム(X)への代替アクセスパスを提供し、I / Oポートレベルでボリューム(X)を使用するアプリケーションを他のアプリケーションから分離できます。

図3. StoreQuant基本モジュールのストレージ構成

ボリュームとRAIDグループは、ストレージサービスを停止することなくオンラインで管理されることに注意してください。 スナップショットメカニズムを使用すると、1つのRAIDグループから別のコントローラー内の別のRAIDグループにボリュームを転送できます。 COW(コピーオンライト)スナップショットとフルスナップショットの2種類のスナップショット、および変更されたデータを複製してスナップショットの作成にかかる時間を短縮するためにスナップショットを時間的に同期する機能をサポートしています。

本質的にはコントローラーがJBODの機能を実行するため、アーキテクチャではJBODのようなシステムを使用しません。 データを保存し、それらへのアクセスを提供するとともに、コントローラー機能、つまり データ保護を提供し、RAIDグループを管理します。

このアーキテクチャでは、クライアント自体がRAIDグループのフォールトトレランスを管理します。 ストレージを使用すると、任意のコントローラーで特定のディスクを選択し、それらに基づいてRAIDグループを形成できます。 したがって、クライアントは、ストレージの次回のアップグレード時に財務リソースを大幅に節約できます。

StoreQuantストレージのアクティブ/アクティブ構成とは何ですか?

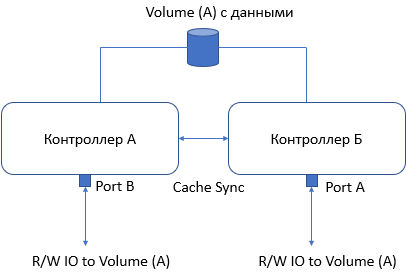

ロシア市場のほとんどのストレージシステムは、少なくとも2つの異なる物理コントローラー内のアクティブなI / Oポートを介してデータ(ボリューム)にアクセスする機能を提供します。 ただし、ロシア市場では、アクティブ/アクティブという用語を異なる方法で理解し、マーケティング資料に誤解を意図的に導入するストレージシステムがあります。アクティブ-アクティブ構成がどのように見えるかを説明してみましょう。以下の図のグラフィック例を参照するのが最善です。4。

「キャッシュ同期」により、バックエンドバスを使用してコントローラー間ですべての書き込み操作を同期できます。

図4.アクティブ-アクティブなStoreQuantストレージ構成

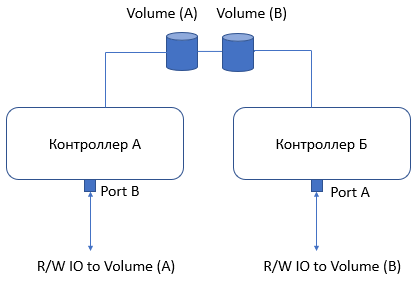

図の構成が簡単にわかります。5は、ストレージコントローラーに障害が発生した場合、データへのアクセス拒否につながります。これは、確かに受け入れがたいイベントです。製品ではこの構成を使用しません。

図5.データアクセス保護なしの構成

StoreQuantストレージでLUNデータアクセスのバランスをとるにはどうすればよいですか?

LUN, .. SCSI. Active-Active , , . , Master, Slave, Slave «» , .. Master , .

StoreQuant, -, . 50/50 (Base Module), .

, StoreQuant :

- 247 8 call-to-repair.

- .

- StoreQuant .

次の記事では、お客様の現在の問題に対する技術的解決策についてお話します。