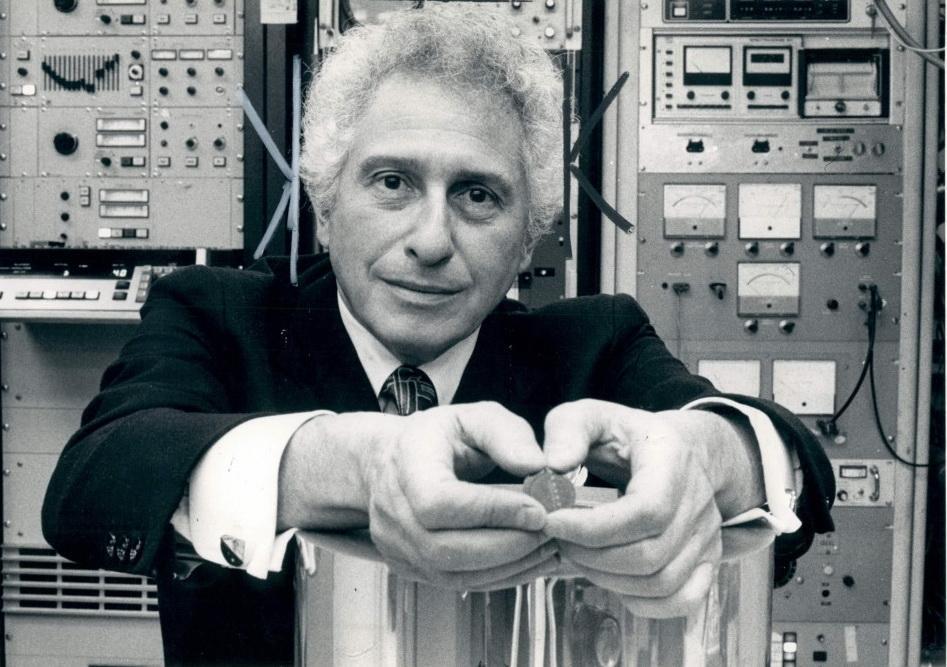

Intelは、公開されたデータに基づいて、新しいチップの根底にある物理的プロセスを正確に世界に伝えることを拒否していますが、3D XPointの起源は1960年代にあると結論付けることができます:この技術は、彼の人生で400件以上の特許を登録したアメリカの科学者Stanford Ovshinskyの業績に基づいていますエネルギーおよび情報技術の分野。 彼の発明はPRAM(相変化メモリ-相転移に基づくメモリ)と呼ばれていました。

PRAMの発明者、スタンフォード・オブシンスキー

フラッシュメモリとは異なり、PRAMは、アモルファス(値「0」)および結晶(値「1」)状態のカルコゲンのバイナリ化学化合物を使用して、バイナリ値を表します。 このアプローチの物理的基礎は、カルコゲナイドの電気抵抗の根本的な違いであり、物質の凝集状態に依存しますが、フラッシュメモリはフローティングゲートの電荷の変化により機能します。 後者のレベルに応じて、トランジスタのしきい値電圧も変化し、より高くまたはより低くなり、したがって1または0をコーディングします。異なる値を記録するには、蓄積電荷の放電を開始する必要がありますが、フローティングゲートから電子を「引き出す」ためには、比較的高い電圧が必要です。 、順番に、スワッププロセスを通じて達成されます。 エネルギーの蓄積には一定の時間が必要なため、フラッシュメモリはかなり「遅い」。同じSRAMと比較して、データブロックの読み取り時間はほぼ10万倍です。 それどころか、PRAMにはこの欠点はありません。個々のビットの値は最初に情報を削除せずに変更できるためです。

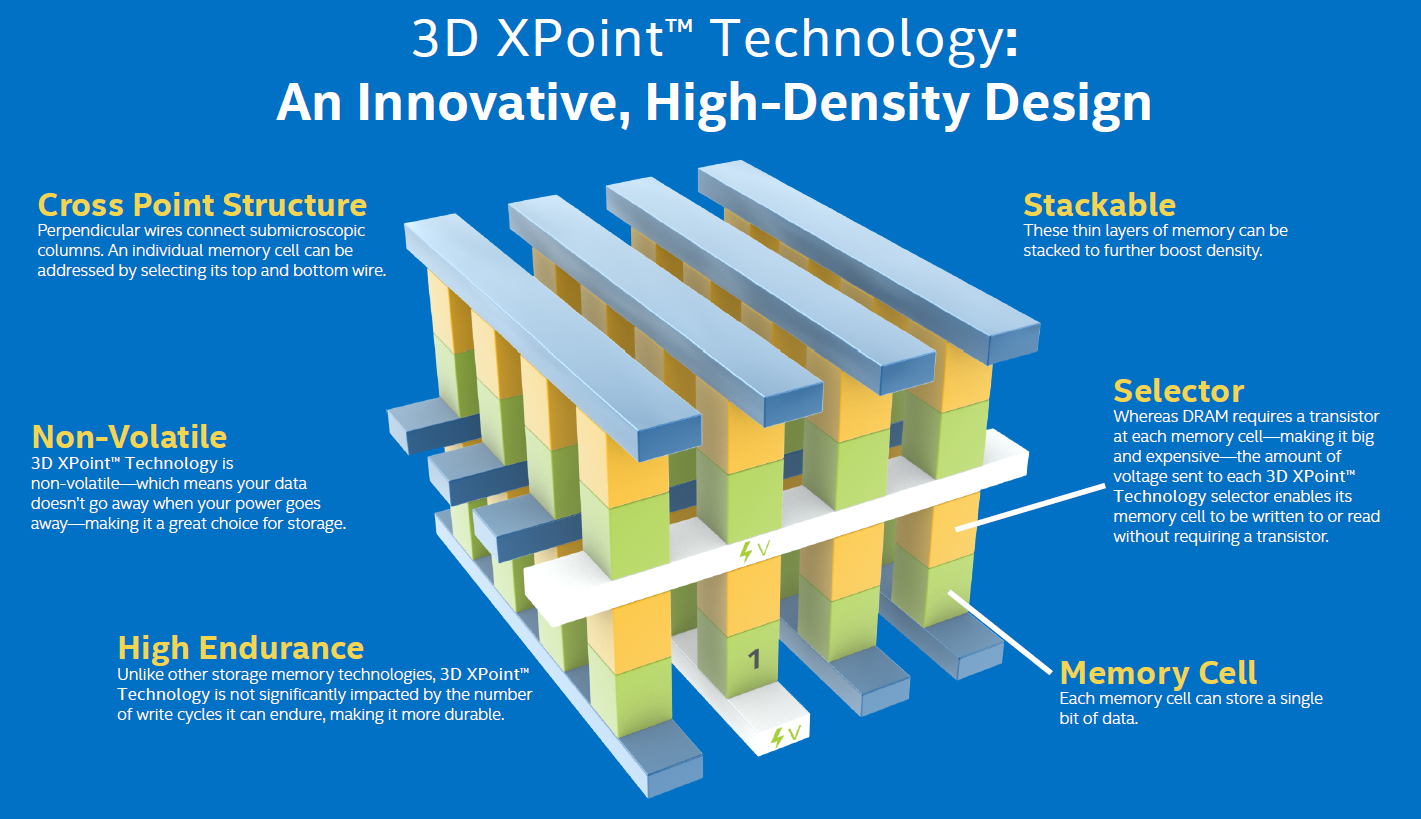

3D XPointの基盤を形成したのはPRAMです。 名前が示すように(XPointは「交差点」を意味するクロスポイントと読む必要があります)、新しいサンプルのメモリクリスタルはクロス構造を受け取りました。

3D XPoint構造

ペア「セレクタ-メモリセル」は、垂直導体の交差点にあります。 セレクターは、特定の電圧が印加されるとアクティブになりますが、セル内の物質の集約状態が変化し、ビットが記録されます。 トランジスタの関与なしにアドレス指定が行われるため、データ記憶密度を高めることでチップ面積を大幅に削減することができました。開発者によると、DRAMと比較して、ゲインは4〜10倍です。

第1世代の3D XPointチップは、20ナノメートルのプロセステクノロジーに従って実行され、超小型回路自体は2層です。 EUVリソグラフィーへの移行により、生産が10 nmに複雑化する可能性があり、構造が3次元に成長するため、チップの容量が大幅に増加するだけでなく、読み取り/書き込みプロセスの速度が向上することがあります。 また、物質の境界状態を使用して1つのセルに2ビットを格納する可能性もあります。それぞれの境界状態には独自の電気的特性があります。 これらの研究は、IntelとST Microelectronicsによってすでに実施されていますが、まだ商業製品に実装されるにはほど遠い状態です。

すべての利点にもかかわらず、3D XPointを含む不揮発性PRAMメモリにも弱点があります。 その中でも、相転移領域と誘電体の直接接触に注意を向ける必要があります。これは、時間の経過とともに誘電体の層間剥離を引き起こし、電荷リークを引き起こす可能性があります。 もう1つのニュアンスは、カルコゲナイド抵抗の増加です。これは、べき法則〜t ^ 0.1で説明されています。 マルチレベル構造では、中間状態で下層と上層の物質の混合が発生する可能性があり、チップがしきい値電圧値からの最小の偏差に敏感になります。 明らかに、Intelは水晶をより安定させることでこれらの問題を解決できましたが、技術の詳細は明らかにされていませんでした。

Intel Optane SSD DC P4800X-3D XPoint用の最初の商用ドライブ

上記のすべては非常においしいように見えますが、実際のシナリオで3D XPointがどのように優れているかを理解するには、既製のデバイスを手に持っている場合にのみ可能です。 そして、それらはすでに存在します:2017年3月20日に、Intelは、PCI Express HHHL形式のOptane SSD DC P4800Xと呼ばれる革新的なメモリに基づくストレージドライブのラインを導入しました。 デバイスは128ギガビット20ナノメートル3D XPointチップを使用し、375または750 GBの容量を持ち、一度に1つのチャネルで4つのクリスタルを制御できるIntel NVMe ASICコントローラーを搭載し、驚異的なパフォーマンスを提供します:4 KBブロックを処理すると、デバイスのパフォーマンスは550,000に達します読み取り時のIOPSおよび書き込み時の500,000 IOPS。遅延は10μsを超えません。 最大順次読み取り速度は2400 MB /秒に達し、書き込み-2000 MB /秒に達します。 リソースオプタンも非常に高く、Intelは約12.3 PBの書き換えを宣言しています。

Intel Optane SSD DC P4800X

印象的? 間違いなく! 急いで注文しないでください:Optaneの推奨価格は1520米ドルで、2018年2月の時点で、ロシアのドライブのコストは106から118千ルーブルまでさまざまです。 これはすべて、Apple II用のAxlon RAM Diskのリリースを思い起こさせます。これは、コンピューター自体よりも数百ドル高いことが判明しました(記事「 ソリッドステートドライブの進化:70年代の最初のモデルから現在まで 」でこの他の興味深いデバイスについて書いています )。唯一の違いは、Intelの発案者は、情報処理の速度が最重要視される企業部門とハイテク産業に焦点を合わせていることです。

3D XPointに基づいた消費者向けのソリューションはありますか? はい この製品はIntel Optane Memoryと呼ばれ、16 GB(平均価格-約3200ルーブル)と32 GB(5100ルーブル)の2つのバージョンがあります。 両方のドライブは、M.2 2280-S3-BMフォームファクターで作成されたNVMe SSDであり、次のパラメーターが特徴です。

ボリュームGB | 32 | 16 |

順次読み取り速度、MB / s | 1350 | 900 |

順次書き込み速度、MB / s | 290 | 145 |

ランダム読み取り速度、IOPS | 240,000 | 190,000 |

ランダム書き込み速度、IOPS | 65,000 | 35,000 |

指標(および1ギガバイトのコスト)は期待できませんが、Intel Optane Memoryは、本格的なソリッドステートドライブとしてではなく、「HDDアクセラレータ」のようなものとして位置付けられています。 第7世代以降のプロセッサー、Intel 200シリーズチップセット以降、REF 15.5 UEFIドライバー以上を搭載したBIOS、Windows10。Ryzenでプラットフォームを構築したことがありますか。Corei7 2700を使用していますか、それともLinuxファンですか。 この場合、この技術はあなたのためではありません。 そして、あなたの車がリストされた要件に完全に準拠していても、急いで購入しないでください。

キャッシングアルゴリズムの容量と機能が小さいため、デバイスは、オペレーティングシステムがロードされ、アプリケーションの固定セットを使用している場合にのみ、顕著な加速を提供できます。 同時に、容量が限られているため、Intel Optane Memoryはマルチメディアファイルの操作(ドライバーが拡張子をチェックする)を無視するため、コンテンツメーカーはパフォーマンスの向上に気付かないでしょう。 プログラムのインストールと更新も同じ速度で実行されます。これは、実行可能ファイルが少なくとも3回連続してアクセスされたキャッシュに送信され、インストーラーが1回起動されるためです。 このゲーマーは熱心なゲーマーにアピールしますか? 利用可能なスペースが最新のAAAゲームの「重量」の5倍少ないという事実を考えると、答えは明らかです。

ただし、再び歴史を振り返ると、最初の小売製品(IBM DiskOneKeyフラッシュドライブ)が技術の登場からわずか10年で登場したとき、フラッシュメモリでも同様の状況が観察されました。 おそらく3D Xpointでも同様のことが起こります。しばらくすると、チップのコストが下がり、だれでも適切な価格でDC P4800Xレベルのモデルを購入できるようになりますか?

複雑すぎて高価すぎる

IM Flash(2006年にIntelとMicronによって設立された合弁会社)のディレクターであるGuy Blelockは、新しいデバイスの価格についてコメントし、有名な業界誌EE Timesにインタビューしました。 彼によると、近い将来、3D XPointメモリーを使用した本格的な消費者グレードのドライブは間違いなく待つ価値がありません。

ガイ・ブロック、IM Flashディレクター

完全に客観的な理由がいくつかあります。 その1つは、新しいチップを作成するには100を超える原材料の名前が必要であり、一部の職種は非常にユニークであり、世界で唯一の企業によって生産されていることです。 これは、投資を誘致する上で問題を引き起こします。 「多くの投資家にとって、この状況は容認できません。彼らは不可抗力の場合に途切れることのない供給を確実にしたいのです」とブロックは言いました。

別の問題は、プロセスの機能によるものです。 クロスアーキテクチャはセル内の材料の相互汚染のリスクを高めるため、3D XPointのリリースには生産チェーンでの追加手順が必要です。 真空蒸着や蒸着などの複雑な段階が追加され、工場の生産性が大幅に低下します。これはすでに完成したデバイスのコストに影響を与えます。 生産量の減少を補うことは可能ですが、Intelのような大企業でも喜びは非常に高価です。

予備的な計算によると、生産されるプレートの数は、条件付きの2平方メートルの面積により、1時間あたり180から1000に増やす必要があります。 技術開発のこの段階では、生産密度を上げることはほぼ不可能であるため、生産能力を5倍にするには、工場自体を少なくとも5倍に拡張する必要があり、これには重大な資本コストが伴います。 最も不快なことは、第2世代と第3世代の3D XPointへのさらなる移行には、同等の投資が必要になることです。 そして、ここで3D NANDメモリの利点が明らかになります。その場合、製造プロセスの変更は20〜30%以内のコストの増加につながります。

3D NANDおよび3D XPointの生産の近代化のコストの比較

さらに、Guy Bllockは、3D XPointのスケーリングは非常に難しいと指摘しました。 理論的には4層チップでも作成できますが、量産には商業版が存在しない極端紫外線リソグラフィのEUVスキャナーが必要です。 上記のすべては、テクノロジーのさらなる進化にとって深刻な制約であるため、近い将来、3D XPointドライブの価格を許容可能なレベルにすることを夢見る必要はありません。

誰もが注意を引いたわけではないもう1つのニュアンスがあります。 新しいOptaneの現在の保証期間は3年ですが、将来、企業は5年に延長することを約束します。 原則として、このような大きな広がりは、十分な統計データがないことを示しており、これに基づいて、誤動作の頻度または機器の完全な故障を判断できます。 そして、これは1つのことしか意味しません。3DXPointドライブの信頼性とフォールトトレランスについて話すのは時期尚早であり、実際の12.3 PBWインジケーターははるかに少ないことがわかります。

3D NAND-価格と性能の最適な組み合わせ

幸いなことに、従来のNANDを埋めるのは時期尚早です。なぜなら、平面チップが垂直の3次元チップに置き換えられたためです。 14ナノメートルプロセスへの切り替えにより、フラッシュメモリメーカーは岐路に立っています。 結晶の密度を上げるには、生産を完全に近代化する必要があります。したがって、さらなる科学研究への投資ははるかに収益性が高く、結果として多層マイクロ回路が作成されました。

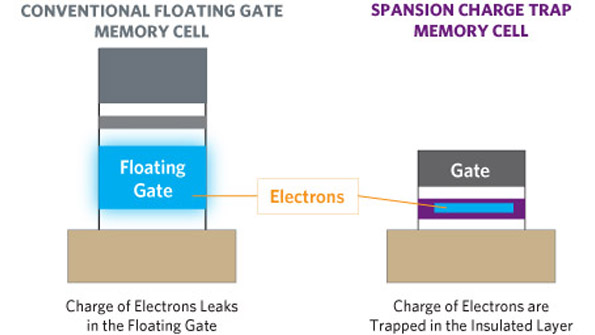

NANDメモリの基礎は、電荷を長時間保持できるフローティングゲートを備えたトランジスタであることを思い出してください。 サイズを小さくすると、あるセルから別のセルへのリークが発生し、保存されたデータが破損する可能性があります。 3次元クラスターを構築しようとすると同様の問題が発生しますが、解決がはるかに簡単であることが判明しました。電荷が保存される非導電性物質から分離領域を作成するだけで十分です。 この技術はCTF(Charge Trap Flash-「充電用トラップ」)と呼ばれ、窒化ケイ素(SiN)が絶縁層の材料として使用されました。

CTFデバイス

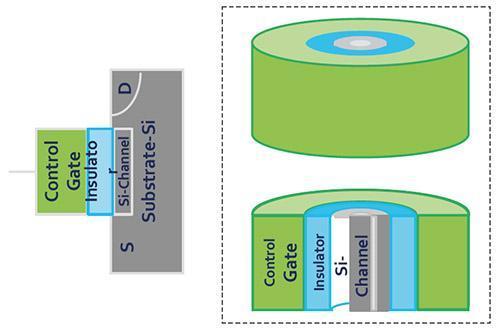

平面チップとは異なり、3D NANDでは各セルは多層シリンダーで表されます。 その外側の層は制御シャッターにすぎず、内側の層は絶縁体です。 互いの上に配置されたセルは、多結晶シリコンの共通チャネルが通る軸に沿ってスタックを形成します。 したがって、スタック内のセルの数は、結晶内の層の数に等しくなります。

3D NANDのセル設計原理

このようなアーキテクチャには、多くの重要な利点があります。

- 単位面積あたりのセル数を増やすことにより、データストレージ密度が増加し、その結果、より容量の大きいドライブを作成することが可能になります。

- セル間の干渉は実質的にないため、読み取り/書き込み速度を大幅に上げることができます。 このため、データの保存および読み取り時には、3つではなく1つの操作のみが実行されます(追加の検証は不要です)。

- 記録には高電圧が必要ないため、3D NANDの寿命はずっと長くなります。

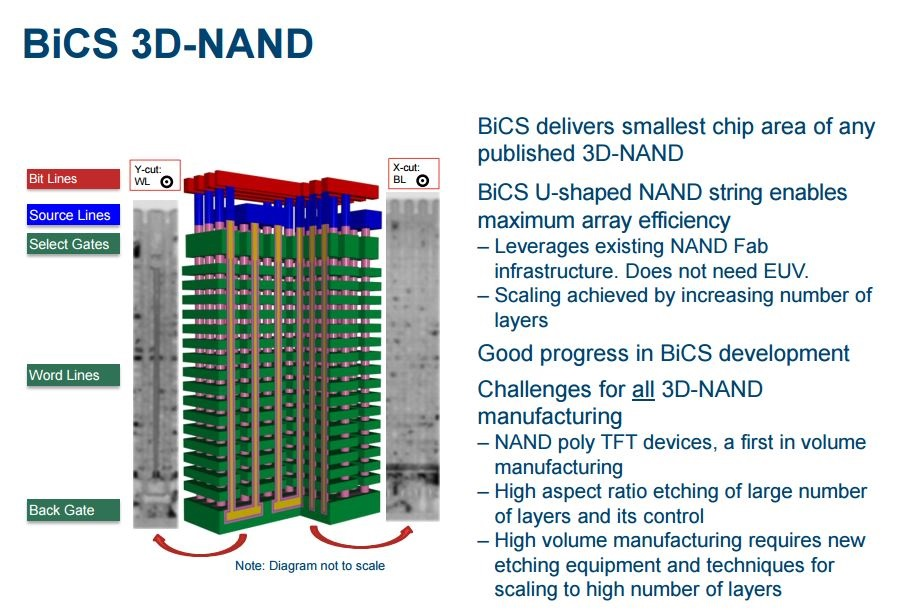

現在Western Digitalが所有しているSanDiskの努力により、3D NANDテクノロジーがさらに発展しました。 その配置の原理は同じままでしたが、U字型のものが線形弦に取って代わりました。 この場合、スイッチングトランジスタとソースラインがシーケンスの最上部に移動され、高温による損傷の可能性が排除されたため、読み取り/書き込み操作中のエラー数が減少しました。

3D NAND BiCSの回路図

新世代の3D NANDはBiCSと呼ばれ、Bit Cost Scalableの略で、この名前は完全に正当化されました。 実際、この技術により、機能性の高い40ナノメートルの生産に基づいて大容量の64層チップを作成できるようになり、遠紫外線(EUV)での高価なフォトリソグラフィーの必要性がなくなりました。

3D NAND BiCSは、個人消費者に焦点を当てた手頃な価格の生産的なソリューションの基盤を形成しました。 2017年8月、Western Digitalは最新の3次元チップに基づいたソリッドステートSATAドライブの生産に切り替えました。現在、SSD Blueの最新ラインをお客様に提供できることを嬉しく思います。 3D NAND BiCSは3D XPointよりも低速ですが、価格と品質の点では、このオファーは市場で最高です。 以下の数字は、それ自体を表しています。

シリーズ | WD Blue SSD | |||

フォームファクター | 2.5ʺ、7 mm / M.2 2280 | |||

インターフェース | SATA 6 Gb / s | |||

収容人数 | 250 GB | 500 GB | 1 TB | 2 TB |

順次読み取り速度、MB / s | 560まで | |||

順次書き込み速度、MB / s | 540まで | |||

ランダム読み取り速度(4 KBブロック)、IOPS | 最大95,000 | |||

ランダム書き込み速度(4 KBブロック)、IOPS | 最大85,000 | |||

TBW、TB | 500まで | |||

MTTF mln h | 1.75まで | |||

幅広い製品により、ニーズを完全に満たすオプションを選択できます。 コンピューターの速度を上げたい場合は、OSに250 GB SSDで十分です。OSはオペレーティングシステムとインストールされたソフトウェアに対応できます。 コンテンツメーカーであり、速度だけでなく利用可能なボリュームも重要な場合、容量が2 TBのBlueシリーズの主力製品に注意することをお勧めします。 フォールトトレランスについては、毎日最大80 GBの上書きが発生しても、ドライブは少なくとも7年間は正常に動作します。このクラスのデバイスの記録です。

妥協せず、自分のPCまたはラップトップを最大限に活用したい人のために、8Gb / sの帯域幅を備えたPCIe Gen3 NVMeインターフェイスの使用によりパフォーマンスが大幅に向上した、プレーナチップに基づいた高速WD Black SSDを用意しました。 負荷の高いシナリオ(3Dモデリング、ビデオエンコーディング、「重い」ビデオゲーム、VR)の大部分では、WD Blackの可能性は十分以上です。SSDは、シーケンシャルリーディングで2050 MB / s、シーケンシャルレコーディングで800 MB / sの安定した速度を示します。ランダム読み取りで最大170,000 IOPS、ランダム書き込みで最大130,000 IOPS(4 KBブロック)。 ドライブには、256 GBと512 GBの2つのバージョンがあります。

結論の代わりに

現時点では、ソリッドステートドライブを作成するアプローチの完全な再考について話すのはまだ時期尚早です。 それどころか、市場のセグメンテーションには前提条件があります。3DXPointが企業セクターを支配できる場合、3D NANDは自信を持って小売をマスターしています。 PRAMの子孫に基づくソリューションの高コストのため、特にそのようなパフォーマンスはほとんどの国内および専門的なタスクに対して過度であるため、対立の話はありません。つまり、価格を考慮に入れると、エンドユーザーは何も受け取りません利点。 最も可能性が高いのは、両方のテクノロジーが並行して開発され、根本的に新しいものが研究室の腸に現れるまで、互いに競合することはないということです。 しかし、次のブレークスルーが発生すると、推測することしかできません。