TMS320C66xxデジタルシグナルプロセッサはKeyStoneアーキテクチャに基づいて構築されており、固定小数点と浮動小数点の両方で動作する高性能マルチコアシグナルプロセッサです。 KeyStoneアーキテクチャは、チップ上でマルチコアシステムを製造するためにテキサスインスツルメンツが開発した原則であり、多数のDSPおよびRISCタイプのコア、アクセラレータ、および周辺機器の効果的な共同作業を整理し、ハードウェアに基づく内部および外部データ転送チャネルに十分な帯域幅を提供しますコンポーネント:Multicore Navigator(内部インターフェイスデータ交換コントローラー)、TeraNet(内部データ転送バス)、Multicore Shared Memory Controller(共有メモリーアクセスコントローラー) )ハイパーリンク(外部機器オンチップレート)とのインターフェース。

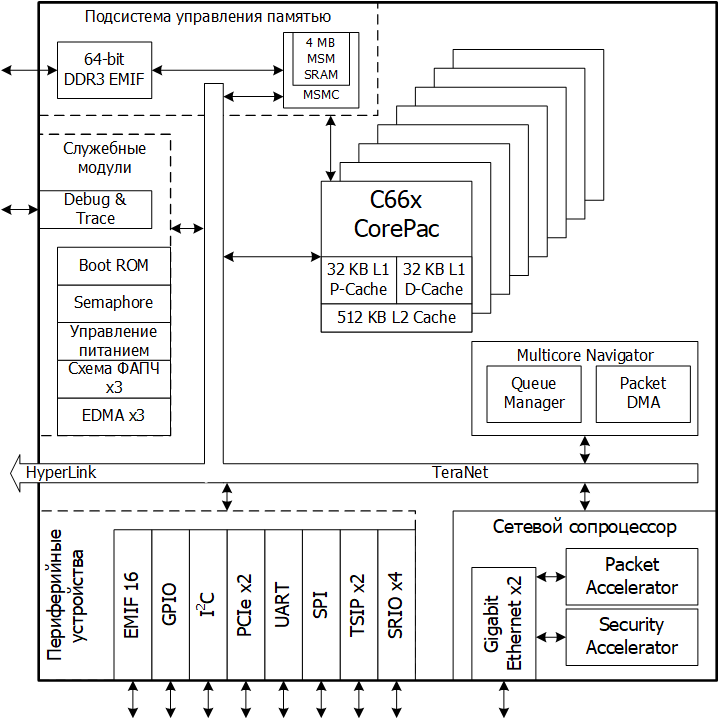

TMS320C66xxファミリーの中で最も高性能なプロセッサーであるTMS320C6678プロセッサー[2]のアーキテクチャーを図1に示します。このアーキテクチャーは、次の主要コンポーネントに分割できます。

- 動作コアのセット(CorePack);

- 一般的な内部および外部メモリを使用する作業のサブシステム(メモリサブシステム);

- 周辺機器;

- ネットワークコプロセッサー

- 内部フォワーダーコントローラー(マルチコアナビゲーター);

- サービスハードウェアモジュールおよび内部TeraNetバス。

図1. TMS320C6678プロセッサの一般的なアーキテクチャ

TMS320C6678プロセッサは、1.25 GHzのクロック周波数で動作します。 プロセッサは、一連のC66x CorePackオペレーティングコアに基づいており、その数と構成は特定のプロセッサモデルによって異なります。 DSP TMS320C6678には、8つのDSPタイプのコアが含まれています。 コアは基本的なコンピューティング要素であり、コンピューティングブロック、レジスタセット、プログラムマシン、プログラム、およびデータメモリが含まれます。 カーネルの一部であるメモリはローカルと呼ばれます。

ローカルメモリに加えて、すべてのコアに共通のメモリ、マルチコアプロセッサの共有メモリ(マルチコア共有メモリ-MSM)があります。 共有メモリへのアクセスは、プロセッサと外部メモリチップ間でデータを交換するための外部EMIFインターフェイスを含むメモリサブシステムを介して行われます。

ネットワークコプロセッサは、さまざまな種類の通信デバイスの一部としてプロセッサの効率を向上させ、この領域のデータ処理ハードウェアに典型的なタスクを実現します。 コプロセッサーは、Packet AcceleratorとSecurity Acceleratorに基づいています。 プロセッサの仕様には、これらのアクセラレータでサポートされる一連のプロトコルと標準がリストされています。

周辺機器には以下が含まれます。

- Serial RapidIO(SRIO)バージョン2.1-回線(チャネル)数-最大4で、回線ごとに最大5 GBaudのデータ転送速度を提供します。

- PCI Express(PCIe)バージョンGen2-1行あたり最大5 GBaudのデータ転送速度、最大行数(チャネル)-最大2。

- HyperLink-KeyStoneアーキテクチャ上に構築されたプロセッサを相互に直接切り替え、チップ内の速度で交換できる内部バスインターフェイス。 データ転送速度-最大50 Gbaud。

- ギガビットイーサネット(GbE)は、10/100/1000 Mbpsの伝送速度を提供し、ハードウェアネットワーク通信アクセラレーター(ネットワークコプロセッサー)によってサポートされます。

- EMIF DDR3-外部メモリインターフェイスタイプDDR3。 64ビットのバス容量を持ち、最大8 GBのアドレス可能なメモリスペースを提供します。

- EMIF-汎用外部メモリインターフェイス。 16ビットのバス幅を持ち、256MB NANDフラッシュまたは16MB NORフラッシュの接続に使用できます。

- TSIP(Telecom Serial Ports) -通信シリアルポート。 回線数が最大8で、回線あたり最大8メガビット/秒の伝送速度を提供します。

- UART-ユニバーサル非同期シリアルポート。

- I2C-内部通信バス。

- GPIO-汎用入出力-16ピン;

- SPI-ユニバーサルシリアルインターフェイス。

- タイマー -定期的なイベントを生成するために使用されます。

サービスハードウェアモジュールは次のとおりです。

- デバッグおよびトレースモジュール -実行中のプロセッサの内部リソースにデバッグツールからアクセスできるようにします。

- ブートROM(ブートROM)-ブートプログラムを保存します。

- ハードウェアセマフォ(セマフォ) -共有プロセッサリソースへの並列プロセスの共有アクセスの編成に対するハードウェアサポートを提供します。

- 電力管理モジュール -プロセッサが全容量で動作していない場合のエネルギー消費を最小限に抑えるために、プロセッサコンポーネントの電力モードの動的制御を実装します。

- PLL-外部基準クロック信号から内部プロセッサクロック周波数を生成します。

- ダイレクトメモリアクセスコントローラー(EDMA) -データ転送プロセスを制御し、DSPオペレーティングコアをアンロードします。これは、Multicore Navigatorの代替です。

内部転送のコントローラー(マルチコアナビゲーター)は、さまざまなプロセッサーコンポーネント間のデータ転送の調停を担当する強力で効果的なハードウェアモジュールです。 TMS320C66xxチップに基づくマルチコアシステムは非常に複雑なデバイスであり、そのようなデバイスのすべてのコンポーネント間の情報交換を整理するには、特別なハードウェアユニットが必要です。 Multicore Navigatorは、コア、周辺機器、ホストデバイスがデータ交換の管理機能を引き継がないようにします。 プロセッサコンポーネントがデータの配列を別のコンポーネントに送信する必要がある場合、それは単に何を転送するかをコントローラに伝えます。 Multicore Navigatorは、送信者と受信者の送信と同期のすべての機能を処理します。

TMS320C66xxマルチコアプロセッサのコアは、多数のプロセッサコンポーネントすべてと外部モジュール間の高速データ交換の観点から、内部TeraNetバスです。

次の記事では、C66xオペレーティングコアのアーキテクチャについて詳しく説明します。

1.マルチコアプログラミングガイド/ SPRAB27B-2012年8月。

2. TMS320C6678マルチコア固定および浮動小数点デジタルシグナルプロセッサデータマニュアル/ SPRS691C-2012年2月。