最新のルーターは、毎秒数百万パケットを処理し、複数のFVルーティングテーブルで動作し、膨大な数のサービスを実装できます。 異なるベンダーは、機器の構築に異なるアプローチを使用しています。 この記事は、膨大な数の結論ではありません。 今日は、ジュニパーのハードウェアアーキテクチャについてお話します。

ルータは、CPUがパケット転送に関与するルータ-つまり、ソフトウェアベースのアーキテクチャ(Cisco 7200など)と、CPUを直接関与せずにパケット転送をハードウェア(ASICまたはFPGA)で実行するルータの2つの大きなクラスに分けることができます-ハードウェアベース(例:Cisco 65/76)。 これらのクラスの機器にはそれぞれ長所と短所があります。 ソフトウェアルーターは自然に非常に安価です。たとえば、フラッグシップのMiktotik ccr1072-1g-8sのコストは20万ルーブルを少し上回り、ベンダーからは1MルーブルのJuniper MX80より高いパフォーマンスが宣言されています。 さらに、このようなルーターでは、新しいソフトウェアバージョンに何らかの機能を追加することにより、さまざまな機能を実装するのが簡単です。 しかし、彼らは蜂蜜の樽で言うように、軟膏にもハエがあります-ソフトウェアソリューションは高性能を誇ることはできません(たとえば、72と76のTsiskiを比較できます)。

インターフェースに約25個のフィルターを掛けると、前述の同じMikrotikのパフォーマンスはほぼ20倍低下します(気になる人はここで確認できます )が、同じMX80はフィルターの実行をハードウェアで実装するため、パフォーマンスが低下することはありません。 ソフトウェアソリューションのもう1つの大きな欠点は、CPUがコントロールプレーンを処理し、同時にデータプレーンの処理に関与することです。 たとえば、インターフェイスの使用率が高いためにプロセッサの負荷がクリティカルな値に上昇した場合(異なるモデルでは異なる-一部の場合は80%が正常であり、35歳の人はすでにdr死しています)コマンドを入力するか、タブをクリックした後、コントロールプレーンが崩れ始める可能性があります。

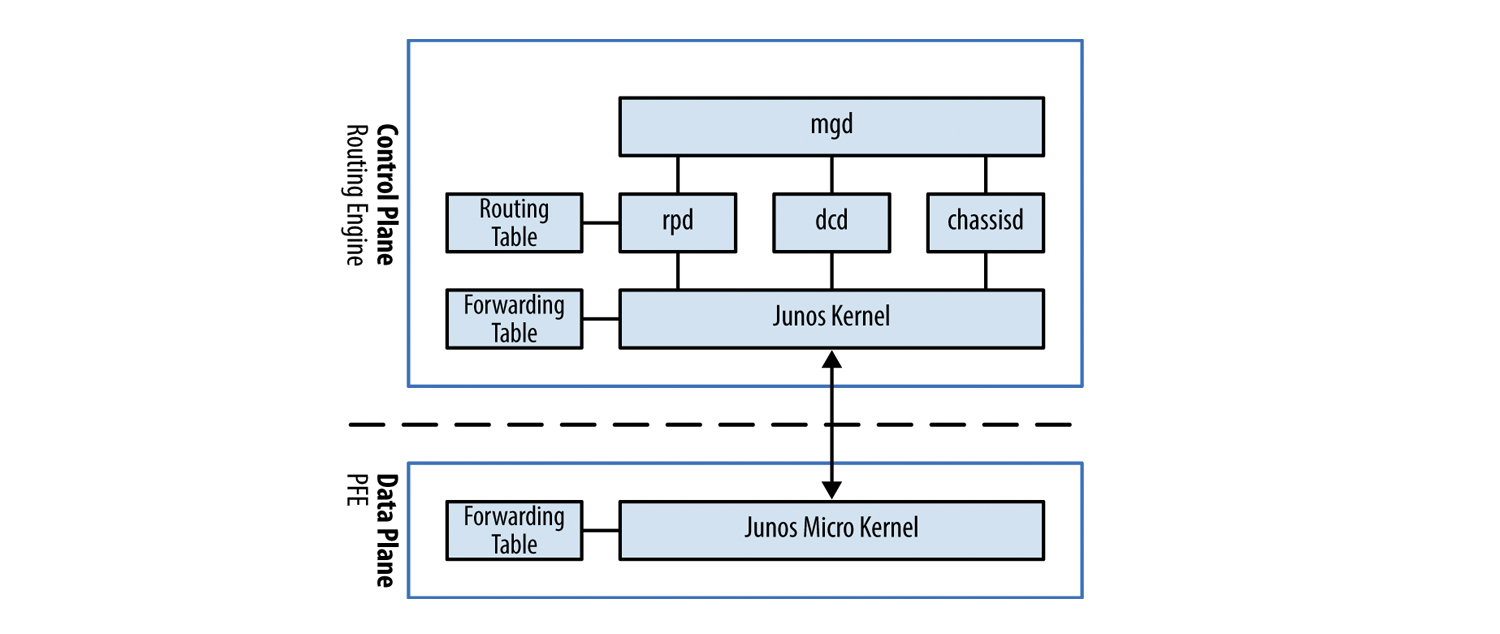

ジュニパーのルーターは、ハードウェアベースのソリューションです。 上記に加えて、ジュニパーのルーターには個別のコントロールプレーンとデータプレーンがあり、これについては後で説明します。

ソフトウェアについて少し話しましょう:JunOS OS

JunOS OSは、ジュニパーのエンジニアによって再設計されたFreeBSDです。 JunOSは、IOS(IOS XRではない)とは異なり、モジュラーアーキテクチャを持ちます-カーネルと、個別の機能のみを担当するプロセスで構成されます。 メモリの一部は各プロセスに割り当てられます。 これにより何が得られますか? プロセスのいずれかが故障した場合、そのプロセスがvrrpの原因であると仮定すると、それは他のすべてのプロセスを一緒にプルせず、同じrpdまたはppmdプロセスが機能します。 フォールトトレラントな機器にとっては当然、これは大きなプラスです。

注:同じIOS XRを見ると、元のIOSとは異なり、モジュール方式で構築されています。

そのため、JunOS OSの最も重要な要素の1つはカーネルです。FreeBSDではモノリシックです。 モノリシックコアの長所と短所については、ここでは検討しません。興味がある人は、例えばWikipediaで読むことができます。 カーネルは、メモリ、プロセッサ、その他のリソースへのプロセスアクセスを共有するために、OSの基本機能であるプロセスの管理とプロセス間の相互作用を実行します。 その他の機能-機器管理、ルーティング、鉄の状態の監視など システムの起動時に開始する特別なプロセス(デーモン)が応答します。

起動時のプロセスのいずれかが何らかの理由で起動できない場合、再起動されます。 再起動しても肯定的な結果が得られない場合、このプロセスの問題に関する情報がログに生成されるため、エンジニアは問題の原因を把握して修正できます。

JunOS OSにはさまざまなプロセスが存在するため、最も重要なものを分析します。

mgd-管理デーモン。 このプロセスは、機器やその他のプロセスの管理を担当し、CLIはそのクライアントです。 mgdのおかげで、ロールバック、プライベート構成モードなどの機能を使用したり、構成の一部を非アクティブに表示したり、適用グループを適用したりできます。

dd-デバイス制御デーモン。 このプロセスは、インターフェースの構成を担当します。 存在しないインターフェイスを設定できるのは彼です。 このデーモンは、rpdがその後ルーティングテーブルにルートを追加できるように、設定されたインターフェイスに関する情報をルーティングソケットに送信します。

たとえば、次のコマンドを入力すると:

インターフェイスxe-0 / 0/0ユニット0ファミリinetアドレス10.0.0.1/30を設定します

次に、cddはIFD、IFL、IFF、IFA、ネットマスク、フォードアドレスをルーティングソケットに送信します。

IFD-インターフェイスデバイス-ルーターの物理ポート(xe-0 / 0/0);

IFL-論理インターフェイス-論理インターフェイス番号(ユニット0)。

IFF-インターフェイスファミリ-アドレスのファミリ(ファミリinet)。

IFA-インターフェースアドレス-アドレス自体(10.0.0.1)。

chassisd-シャーシデーモン。 JunOSで最も重要なプロセスの1つ。 ルーターのすべてのコンポーネントの状態(ルーターのさまざまなノードの電圧からファンの速度まで)の監視を担当するのは彼です。 問題が発生した場合、このデーモンはボードおよび/またはルーターを切断して損傷を回避したり、問題に関する情報をデーモンに送信したり、デーモンに送信したりします。そして、デーモンはログにメッセージを生成し、ルーターのクラフトパネルのインジケーターをオンにします。

rpd-ルーティングプロトコルデーモン。 このプロセスは、ripからbgpまでのすべてのルーティングプロトコルを担当します。 彼は、デバイス間の近隣を維持し、デバイス間でルーティング情報を交換し、最適なルートを選択し、ルーティングテーブルをコンパイルし、パケットを促進するために直接使用される転送テーブルを担当します。

注: rpdにはppmdヘルパーがあります。これは、BFDプロトコルなどの定期的なメッセージの生成と受信を行うプロセスです。 次の記事では、ジュニパーの機器の耐障害性について説明します。

興味深い場合は、他のプロセスを検討しません。次に、JunOSの簡単な説明を含むすべてのプロセスのリストをここに示します 。 自然に英語でプロセスの説明。

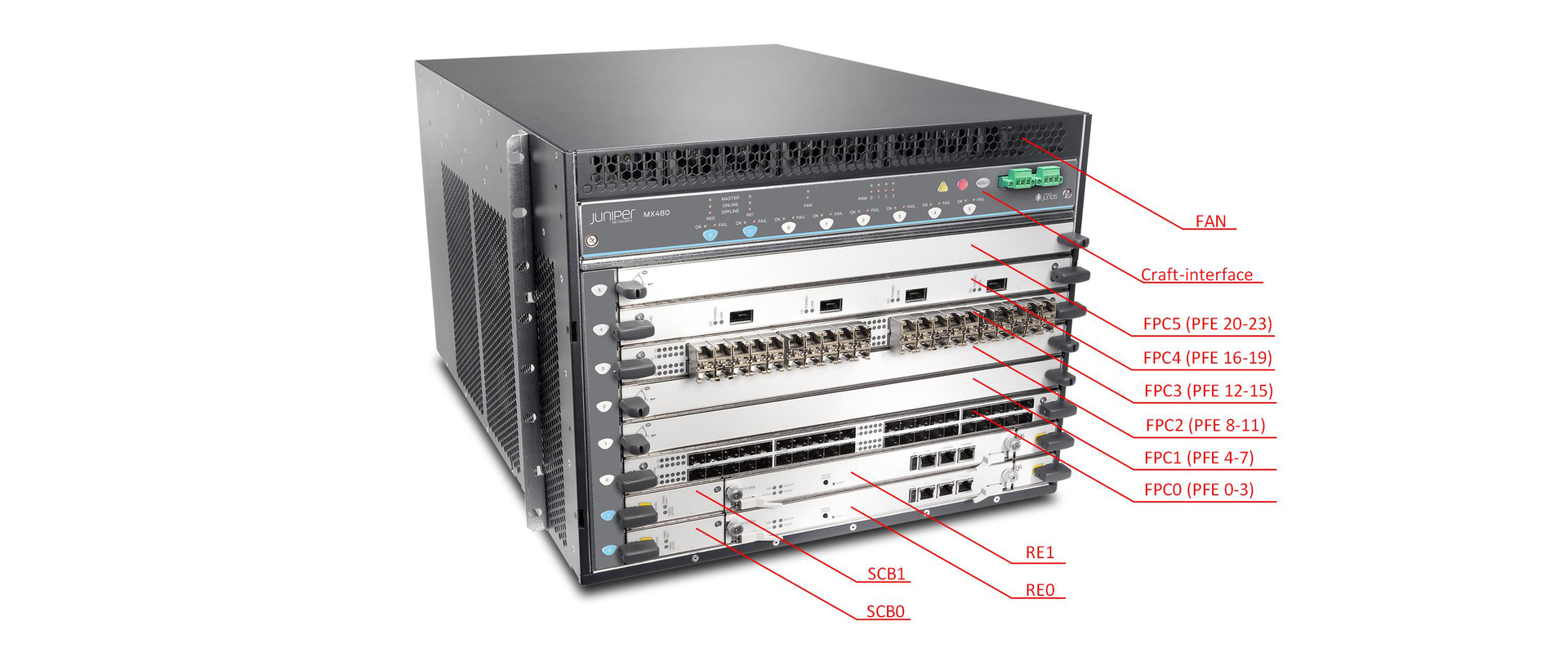

次に、ジュニパールーターの構成要素を見てみましょう(MXシリーズの例を見ていきます)。

そのため、ジュニパーのルーターはいくつかの主要部分で構成されています。

-RE(ルーティングエンジン)

-PFE(パケット転送エンジン)

-SCB(スイッチおよび制御ボード)

-ミッドプレーン

当然のことながら、ルータはファンユニットや電源装置がないと動作しません。 ただし、これらの部分は厳密に定義された機能を実行するものであり、インテリジェントなデバイスではありません。

各要素の目的と構成を個別に検討してください。

ルーティングエンジン

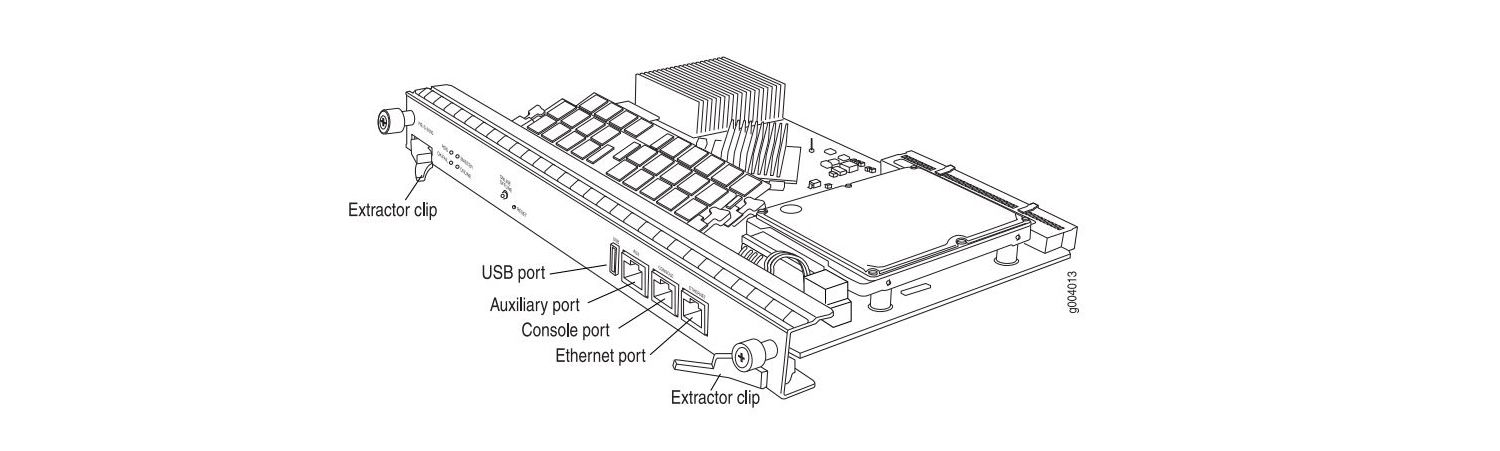

RE-ルーターの頭脳です。 彼は、ルーティングプロトコルの操作(近隣の維持、ルーティング情報の交換、最適なルートの選択など)を担当します。 ルーターを管理するため。 インターフェイスの統計を収集および保存し、ログを収集し、必要なファイルを保存します。

REの仕様は、 ジュニパーの Webサイトで確認できます。

JunOSでは、ポリシーは非常に強力なツールですが、ほとんどの場合、ポリシーはルーティングプロトコルに関連付けられているため、受け入れられるもの、発表されるものはREで実行されるものです。 REは、処理がハードウェアに実装できない(または非常に難しい)パケットも処理します。これらは、オプション付きのIPパケット、ラベル1のmplsフレーム、ルーターへのICMP要求、telnetまたはssh制御です。

実際、REはCPU、RAM、HDD / SSD、イーサネットポート、USBポートなどを備えた本格的なサーバーです。CPUとRAMが必要なのはなぜですか、説明する必要はないと思います。残りのコンポーネントの目的を説明する必要があります。

Routing Engine 0 REV 06 740-031116 9009103533 RE-S-1800x4 ad0 3831 MB UGB30SFA4000T1 SFA4000T1 0000079B Compact Flash ad1 30533 MB UGB94ARF32H0S3-KC UNIGEN-478612-001183 Disk 1 usb0 (addr 1) EHCI root hub 0 Intel uhub0 usb0 (addr 2) product 0x0020 32 vendor 0x8087 uhub1 DIMM 0 SGX55N72N2SS2SA-BB DIE REV-52 PCB REV-54 MFR ID-ce80 DIMM 0 SGX55N72N2SS2SA-BB DIE REV-52 PCB REV-54 MFR ID-ce80 DIMM 0 SGX55N72N2SS2SA-BB DIE REV-52 PCB REV-54 MFR ID-ce80 DIMM 0 SGX55N72N2SS2SA-BB DIE REV-52 PCB REV-54 MFR ID-ce80

CFカード -メモリカード。 このカードは、使用されているJunOS OSの現在の構成とバージョンを保存するように設計されています。

ad0 3831 MB UGB30SFA4000T1 SFA4000T1 0000079B Compact Flash

HDD / SSD-ハードドライブまたはソリッドステートドライブ。 このメディアは、ログとファイルを保存するように設計されています。

ad1 30533 MB UGB94ARF32H0S3-KC UNIGEN-478612-001183 Disk 1

USBポート。 このポートは、システムの起動や復元などに使用される外部メディアを接続するように設計されています。 JunOSの起動順序は次のとおりです。最初にUSBフラッシュディスク、次にCFカード、最後にHDD / SSDです。 RE MX104など、一部のREには2つのUSBポートがあります。

イーサネットポート。 このポートの目的は、ルーターを制御することです。 原則として、REには1つではなく3つのポートがあります。

-イーサネット

-コンソール

-AUX

イーサネット -ポートは機器管理(帯域外管理)に使用されます。 このポートは、システムでfxp0としてマークされています。

fxp0インターフェイスに加えてshow interfaces terseコマンドを使用すると、em0およびem1インターフェイスも表示できます。 これらのインターフェイスは、ルータの他の要素(サービスカード、ラインカード)とREを通信するように設計されています。

{master} bormoglotx@test-mx480> show interfaces terse | match em Interface Admin Link Proto Local Remote demux0 up up em0 up up em0.0 up up inet 10.0.0.4/8 em1 up up em1.0 up up inet 10.0.0.4/8

fxp0インターフェイスは常に使用されるわけではありません-fxp0テストルーターで見られるように、インターフェイスはダウンしています。警告で示されているように、パッチコードがこのポートに接続されていないためです。

{master} bormoglotx@test-mx480> show interfaces terse | match fxp fxp0 up down {master} bormoglotx@test-mx480> show chassis alarms 2 alarms currently active Alarm time Class Description 2011-01-14 12:32:38 MSK Major Host 0 fxp0 : Ethernet Link Down 2011-01-14 12:32:38 MSK Major Host 1 fxp0 : Ethernet Link Down

コンソール -ポートはコンソールアクセス用です。

補助-補助ポート。 実際、これはコンソールポートに似ていますが、大きな違いがあります。ブート時にコンソールポートでルーターに接続すると、JunOS OSブートログが表示されます。 OSのロード時の補助ポートは使用できません。ルーターをロードした後にのみ、機器にアクセスできます。 さらに、このポートを使用して、コンソールポートの別のデバイスに接続できます。

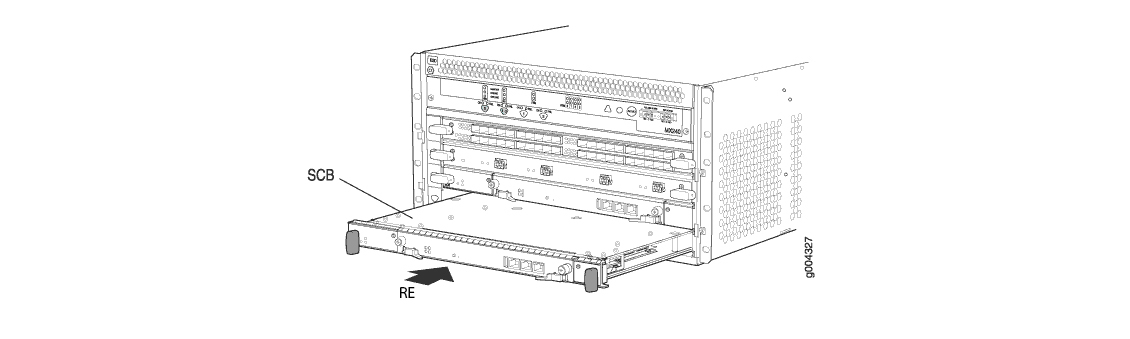

MXシリーズルーター(より新しいMX5-MX80ラインを除く)では、REがスイッチングファクトリーにインストールされています(SCB-詳細は以下)。 原則として、高い耐障害性のために、REは2つにインストールされます-1つはマスター、2つ目はバックアップです(これについては次の記事で説明します)。 REが現在マスターである場合、ホットスワップはサポートされていません(より正確には、それを引き出して「ライブ」に挿入できますが、GRES / GRまたはGRES / NSRが設定されていない場合、トラフィックが失われます)。 ただし、バックアップREはホットスワップをサポートしています。

このプロセスでは、マスターREからバックアップに移動できます。 RE間のハードドライブに保存されているファイルは同期されず、1つのREのハードドライブにファイルを削除または追加する場合、2番目のREにファイルを削除または追加しません。 これは、たとえば、ソフトウェアを更新するときに考慮する必要があります(REの1つに場所がない、2番目のREがいっぱいになっているなど)。

パケット転送エンジン

REがルーターの頭脳である場合、PFEには腕と脚があります。 PFEを介して、管理トラフィックを含むすべてのトラフィックを処理します(RE自体のコンソールまたは管理ポートを介して制御が行われない場合)。 PFEは、ハードウェアの生産を可能にするプログラム可能なチップで構成されています。

-ネクストホップの検索。

-ip / mpls / macルックアップを実行します。

-QoSを適用します。

-ポリサーを適用します。

-フィルタリングを適用します。

-トンネリング。

PFEはインターフェイスカードにインストールされています。 1、2、または4個のPFEを備えたボードがあり、各PFEは独自のインターフェイスグループのみに対応し、SCBを介して他のPFEと相互作用します。 インターフェイスカードには、すべてのPFEを制御するCPUがあります。 PFEとRE間の通信は、SCBボードに統合されたギガビットスイッチを介して行われます。

注:すべてのインターフェースカードはホットスワップをサポートしています。

Trioチップセットを例として使用して、PFEの組成を見ていきます。 論理的には、チップセットはいくつかのブロックで構成されています。

メモリおよびバッファリングブロック -このブロックは、他のすべてのブロック間の相互作用を提供します。 通常のボード(Qインデックスなし)では、キューブロックの機能も実行されます(当然のことながら、より簡略化されたバージョンで)。大容量のボードでは、インターフェイスブロックの機能を実行します。

ルックアップブロックは、IPまたはMPLSルックアップを実行し、パケットヘッダーを変更し、フィルター、シェーパー、QoSを適用するマルチコアチップです。 このブロックはPFEの中心です。 このブロックはパケットヘッダーで機能し、最大256バイトのサイズのヘッダーを分析できます(これにより、DDOSに対する保護など、さまざまなサービスを実装できます)。

インターフェイスブロック -このブロックは、低帯域幅のボード上に存在し、着信パケットの予備分類の機能を実行します。 このブロックが存在しない場合、この機能はバッファリングブロックによって実行されます。

密キューイングブロック -拡張キューのブロック。 ボード上にQインデックスが表示され、H-QoSを実装できます。 このブロックがない場合、その機能(当然、切り捨てられた形式)はバッファリングブロックに分類されます。

これらのブロックのハードウェアは、次のチップで表されます。

バッファリング-MQ(メモリおよびクエリ)またはXM (このチップの拡張バージョン)

ルックアップブロック-LU (ルックアップユニット)またはXL (拡張バージョン)

インターフェースブロック-IX

クエリ-QXまたはXQ (詳細)

ブロックはHSL2リンクによってリンクされているため、データをすばやく交換できます。

市場には、MPC1からMPC9Eまで、多数のMPCラインカードがあります。

すべてのラインカードの完全なリストは、ジュニパーのWebサイトで入手できます。 バージョンによって、インストールされているPFEの数が異なります(MPC1-1 PFE、MPC2-2 PFE、MPC3E-1 PFE、ただし拡張バージョン)。 これらのカードにインストールされているPFE自体は、インストールされているチップのバージョン(標準または拡張)とインストールされているチップの数が異なります(たとえば、MPC4Eカードは2つのPFEを使用し、4つのLUユニットがインストールされます)。 もちろん、インストールされているチップとその数を改善することに加えて、SRAM / DRAMメモリの量も変化します。そうでなければ、パケットは単にバッファリングする場所がなくなります。 1つのボード上のPFEの最大数は4です;合計で、1つのラインカードの一部として1、2、または4つのPFEがあります。

スイッチと制御ボード

ただし、ルーター全体のスループットはPFEだけでなく、SCBも重要なリンクです。 このカードがボトルネックになることがあります。 このボードは、異なるPFE間のパケットスイッチングと、REとPFE間の接続を担当します。 さらに、REはSCBにインストールされます。 このボードにREマスターが含まれていない場合は、ホットスワップをサポートします(カードが冗長性なしのモード3 + 0で動作する場合、トラフィック損失を取得できます)。

SCBには、2つのスイッチングファクトリと統合されたギガビットスイッチの3つの主要コンポーネントがあります。 それぞれについて個別に話しましょう。

組み込みのギガビットスイッチは 、ルーターのすべての要素間の通信を整理するように設計されています。 MXルーターの各ボードには2つのギガビット内部インターフェイスがあり(上記の出力では、REに2つのemインターフェイスがあります)、2つのスイッチ(メインに1つ、バックアップSCBに2つ)に接続されています。 このインターフェイスを介して、REとPFE間(およびRE間)で情報が転送されます。 PFEがREで処理されるパケットを受信すると、このギガビットリンクを介してパケットがREに送信されます。たとえば、フォワーディングテーブルはREからPFEに転送され、カウンター値はインターフェイスからPFEからREに転送されます。 SCBには、インストール済みのボードに接続できるギガビット外部インターフェイスがあります。

次の出力から、スロット0と1に2つのラインカードがインストールされていることがわかります。

{master} bormoglotx@test-mx480> show chassis fpc Temp CPU Utilization (%) Memory Utilization (%) Slot State (C) Total Interrupt DRAM (MB) Heap Buffer 0 Online 26 10 0 2048 15 16 1 Online 25 14 1 2048 15 24 2 Empty 3 Empty 4 Empty 5 Empty

内蔵スイッチのリンクの状態を見ると、0と1のリンクがラインカード0と1、および12と13がRE1とRE0に接続されていることがわかります。

{master} bormoglotx@test-mx480> show chassis ethernet-switch Displaying summary for switch 0 Link is good on GE port 0 connected to device: FPC0 Speed is 1000Mb Duplex is full Autonegotiate is Enabled Flow Control TX is Disabled Flow Control RX is Disabled Link is good on GE port 1 connected to device: FPC1 Speed is 1000Mb Duplex is full Autonegotiate is Enabled Flow Control TX is Disabled Flow Control RX is Disabled Link is down on GE port 2 connected to device: FPC2 Link is down on GE port 3 connected to device: FPC3 Link is down on GE port 4 connected to device: FPC4 Link is down on GE port 5 connected to device: FPC5 Link is down on GE port 6 connected to device: FPC6 Link is down on GE port 7 connected to device: FPC7 Link is down on GE port 8 connected to device: FPC8 Link is down on GE port 9 connected to device: FPC9 Link is down on GE port 10 connected to device: FPC10 Link is down on GE port 11 connected to device: FPC11 Link is good on GE port 12 connected to device: Other RE Speed is 1000Mb Duplex is full Autonegotiate is Enabled Flow Control TX is Disabled Flow Control RX is Disabled Link is good on GE port 13 connected to device: RE-GigE Speed is 1000Mb Duplex is full Autonegotiate is Enabled Flow Control TX is Disabled Flow Control RX is Disabled Link is down on GE port 14 connected to device: Debug-GigE

スイッチファブリック

スイッチングファクトリは、PFE間でトラフィックを転送するように設計されています。 すべてのPFEをフルメッシュトポロジに接続します。 現在、SCBにはSCB、SCBE、SCBE2の3つの世代があります。 これらのカードは帯域幅が異なります。 メーカーのウェブサイトによると、SCBはスロットあたり少なくとも120 Gbps、SCBE-160 Gbps、SCBE2-スロットあたり340 Gbpsの帯域幅をサポートしています。 これらのボードは、SF(SCB)およびXF(SCBE、SCBE2)チップ上に構築されています。

注: SCBE2は340 Gbps /スロットの帯域幅を提供しますが、ボード上のPFEの数と各PFEによって処理されるインターフェースの数を忘れないでください。 MPC4E 8x10GE + 2x100GEボードを例にとると、このボードの合計帯域幅は280 Gb / sです。 ただし、2つの高度なPFE(スループット130ギガビット/秒)のみがインストールされているため、このボードのスループットは2x130ギガビット/秒= 260ギガビット/秒です。 ここでは、WANグループの概念が重要に見えます。 インターフェイスはグループ化されています。 このボードには2つの組み込みPICがあります。1つの8x10GEインターフェイスと2つ目の2x100GEインターフェイスです。 PFEの場合、それらはWANグループ0および1に結合されます(8x10GE-グループ0、2x100GE-グループ1)。 最初のPFEは、グループ0の最初の4GEインターフェイスとグループ1の最初の100GEインターフェイスに対応します。PFE1についても同様です。 つまり、1つのPFEが140ギガビット/秒を処理しますが、スループットは130ギガビット/秒です。 合計で、2つの10GEを除くすべてのポートがインターフェイス速度で動作できることがわかります。

論理的に、SCBへのPFEの接続は次のようになります。

MX960の場合

MX240 / 480の場合

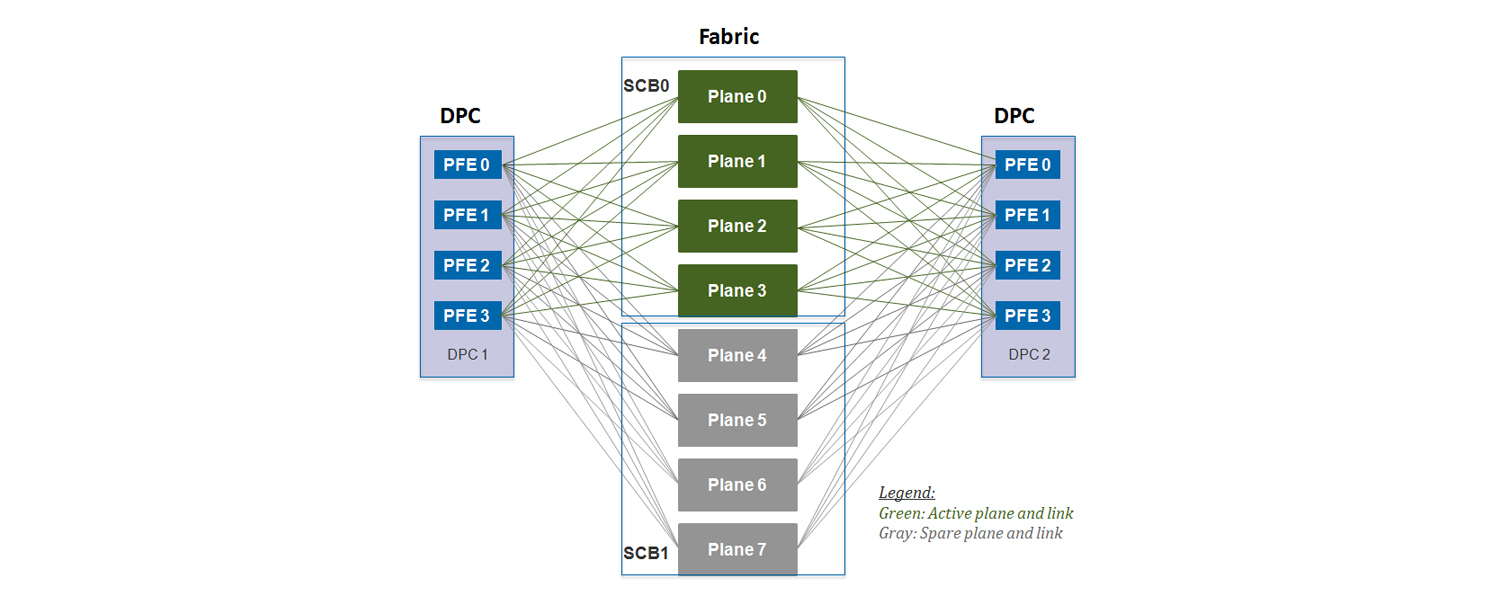

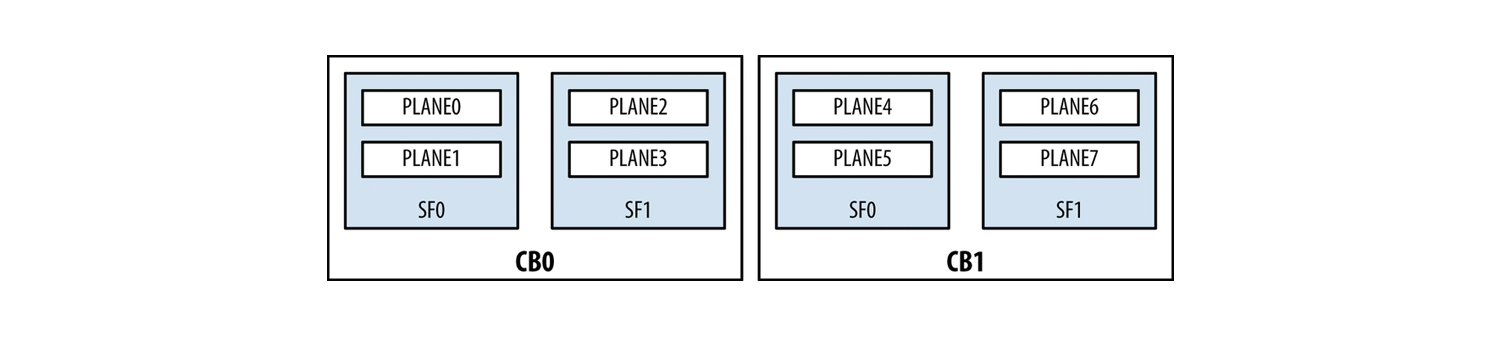

図からわかるように、各SCBはプレーンに分割されています。 飛行機とは何ですか? なぜ、SCBをmx480に挿入すると4つのプレートがありますが、同じボードをMX960に挿入すると2つのプレートしかありませんか? これを理解するには、スイッチングファクトリをN番目のポートを持つスイッチとして想像する必要があります。 ポートはいくつ必要ですか? カードあたりのPFEの最大数は4メートルです。 次に、必要なポート数を計算してみましょう。

したがって、PFEの最大可能量は48であることがわかります。 そのため、PFE全体の間に完全に接続されたトポロジを作成するには、1つのスイッチングファクトリに48個のポートが必要です。 MX960にSCBをインストールすると、48個すべてのインターフェイスが関与します(関与する可能性があります)が、MX480にボードを挿入すると、48個のポートのうち24個しか必要ないことがわかります-つまり、24個のポートがアイドル状態になります。 (MX240を使用する場合-比率はさらに大きくなります)。 したがって、playneの概念が導入されました。 1つのプレインは、すべてのPFE間に完全に接続されたトポロジを提供する仮想スイッチです。 MX960にインストールされた場合、1つのスイッチングファクトリーがプレーンを1つしか持たず、MX480 / 240にはすでに2つのスイッチングファクトリーがある理由が明らかになったと思います。 1つのSCBには2つのスイッチングファクトリーがあるため、1つのボードがMX960に2つのプレートを、MX480 / 240に4つのプレートを提供することがわかります。 その結果、予約を考慮して、次のようなプレーンが取得されます。

MX960の以下の出力からわかるように、6つのプレーンがあります。

{master} bormoglotx@test-mx960> show chassis fabric plane-location ------------Fabric Plane Locations------------- Plane 0 Control Board 0 Plane 1 Control Board 0 Plane 2 Control Board 1 Plane 3 Control Board 1 Plane 4 Control Board 2 Plane 5 Control Board 2

ただし、現在アクティブなリプレイアンは4つだけです。2つのSCB3プレイリストは、フォールトトレランスを高めるように設計されています(2 + 1)

{master} bormoglotx@test-mx960> show chassis fabric summary Plane State Uptime 0 Online 543 days, 13 hours, 34 minutes, 24 seconds 1 Online 543 days, 13 hours, 34 minutes, 23 seconds 2 Online 543 days, 13 hours, 34 minutes, 23 seconds 3 Online 543 days, 13 hours, 34 minutes, 23 seconds 4 Spare 543 days, 13 hours, 34 minutes, 22 seconds 5 Spare 543 days, 13 hours, 34 minutes, 22 seconds

注: 6つのプレイナンがすべてオンラインになる可能性があります。これは、2つのSCBのスループットがインストールされているすべてのカードを処理するのに十分でない場合に必要です。 その後、予約はありません(3 + 0)。

MX480とMX240の場合、出力は若干異なります。

{master} bormoglotx@test-mx480> show chassis fabric plane-location ------------Fabric Plane Locations------------- Plane 0 Control Board 0 Plane 1 Control Board 0 Plane 2 Control Board 0 Plane 3 Control Board 0 Plane 4 Control Board 1 Plane 5 Control Board 1 Plane 6 Control Board 1 Plane 7 Control Board 1

2つのマップに8つの平野があります。 1 + 1の冗長性を使用しているため、4つのオンラインペイアウトのみです。

{master} bormoglotx@test-mx480> show chassis fabric summary Plane State Uptime 0 Online 698 days, 2 hours, 17 minutes, 31 seconds 1 Online 698 days, 2 hours, 17 minutes, 26 seconds 2 Online 698 days, 2 hours, 17 minutes, 26 seconds 3 Online 698 days, 2 hours, 17 minutes, 20 seconds 4 Spare 698 days, 2 hours, 17 minutes, 20 seconds 5 Spare 698 days, 2 hours, 17 minutes, 15 seconds 6 Spare 698 days, 2 hours, 17 minutes, 14 seconds 7 Spare 698 days, 2 hours, 17 minutes, 9 seconds

ミッドプレーン

ミッドプレーンはシャーシの背面壁に取り付けられており、電源からルーターの各要素へのすべてのボードと電源間の電気接続を提供します。

MX80

また、若いMX5-MX80ラインについても言いたいと思います。 この行には4つのルーターがあります-MX5、MX10、MX40およびMX80。 ハードウェアでは、これらは完全に同一のルーターです。つまり、すべてMX80と同じ詰め物を持ち、違いは色(MX104のように灰色)と銘板のみです。 ライセンスを購入すると、ポートと機能がソフトウェアによってブロックされるため、MX5をMX80にいつでも変更できます。 多くのメーカーがこのプラクティスを採用しています。たとえば、シスコはASRまたはHuaweiでも同じことをしています。

MX80自体は、その兄とは異なります。 そのアーキテクチャにより、Trioチップセット(MQ、QX、LUユニットがそれぞれ1つ)に基づいたPFEが組み込まれ、REが組み込まれています。 SCB機能はREとPFEの間にリンクを作成するようになったため、開発者はそれを別のSCBボードとして拒否しました。 大まかに言えば、MX80はラインカードであり、REは2ユニットのパッケージに組み込まれています。 当然、このルーターにはフォールトトレランスを向上させるメカニズムはありませんが、そのコストは最も近い兄弟MX240のコストよりはるかに低くなっています。

たとえば、Juniper MXシリーズルーターはNATの実行方法を知らないことを付け加えておきます。 これらの目的のために、ラインカード用に設計されたスロットのいずれかに挿入できる特別なマルチサービスDPCサービスカード(MS-DPC)があります(ボックスあたりのカード数には制限があります)。 MS-DPCは次のサービスを提供できます。

-NAT(すべての形式で);

-セッションボーダーコントロール(SBC);

-ディープパケットインスペクション(DPI);

-ファイアウォール機能。

サービスカードはすべてのMXシリーズルーターをサポートします(MX80を含む-ルーターの背面に特別なカード用のスロットがあります)。 これらのカードについては、 メーカーのウェブサイトで読むことができます。

ジュニパーMXパッケージトラベル

今週に基づく:MXシリーズ3Dのエキスパートパケットウォークスルー

ルーターの構成を把握しましたが、あるインターフェイスから別のインターフェイスにパケットがどのように転送されるのでしょうか? パッケージの処理方法は、そのタイプによって異なります。

-通過パケット、1つのPFE上の着信および発信インターフェイス。

-異なるPFE上の中継パケット、インバウンドおよびアウトバウンドインターフェイス。

-CPU REで処理されるパッケージ。

-インターフェースカードのCPUで処理されるパッケージ。

-CPU REによって生成されたパケット。

-CPU PFEによって生成されたパケット。

トランジットパケットが1つのPFEの責任のゾーンにインバウンドインターフェイスを持ち、別のPFEのアウトバウンドインターフェイスを持つ最も難しいケースを分析します。

そのため、パケットは着信インターフェイスで受け入れられます。 パケットは、物理層とチャネル(MACサブ層)の間の層であるMACコントローラーに届きます。 このコントローラは、物理インターフェイスとPFEを相互接続します。 コントローラの重要な機能の1つは、受信したフレームのチェックサムをチェックすることです(計算された量の合計がFCSで指定された量と一致しない場合、パケットはドロップされます。

次に、Trioチップセットが作業に含まれます。 低帯域幅のボード(たとえば、20ギガビットポート)がある場合、PFEにはインターフェイスユニット(IXチップ)が含まれます。 このブロックは、パッケージの予備分類を行います。 この分類は、各インターフェイスにリアルタイム(RT)、ベストエフォート(BE)、および制御の3つのクラスしかないため、非常に粗雑です。 最後のクラスには、管理トラフィック(ルーティングプロトコル、vrrpなど)が含まれます。 より容量の大きいボード(たとえば16)がある場合、このブロックはボード上にありません。 したがって、インターフェースユニットのタスクはバッファリングユニットにかかっています。

バッファリングブロックは、いくつかのブロックで構成されます(それらの機能は、パケットが進むにつれて考慮されます)。 予備分類後、パケットはWAN入力ブロックに入ります。 このブロックは他のすべてのブロックをそれ自体に接続し、受信パケットのセグメンテーションと、その後のバッファリングと、ルックアップブロックに送信するためのヘッダーの分離を行います。 より詳細に。 このブロックに入ると、ヘッダーはパケットから分離され、パケットは特別なコンテナである小包に入れられ、残りのパケットはOnChipメモリ(SRAM)にバッファされます。

パーセルは、サイズが256〜320バイトのコンテナーです。 ほとんどの場合、パケット長は256バイトです。 サイズが320バイト以下のパケットがWIブロックに到達した場合、このパケットは完全に区画に配置されます。 パケットのサイズが320バイトを超える場合、最初の256バイトはパケットから分離され、残りのパケットはOnChip-memory(SRAM)にバッファリングされます。

パーセルは、バッファリングブロックからルックアップブロックに送信するとき、特別なM2L(MQ to LU)ヘッダーを持ち、これはクラス番号(このパケットが予備分類中に割り当てられた)を示します。 問題はすぐに発生します。なぜパッケージを2つの部分に分割してパーセルを生成するのですか? ソースパッケージを使用する方が簡単ではありませんか? この場合、チップセット内を流れるデータが多すぎます(たとえば、バッファリングブロックからルックアップブロックへ、またはその逆)。 チップセット要素間のパケットのバッファリングには困難があり、それらの間の接続の負荷が増加します。 この場合、パケットの内容はバッファに格納され、小包はチップセットの残りのブロックで処理されます。

注: WIブロックは、受信したパケットのヘッダーの数と数を知りません。 256バイトを分離すると、データの一部がパーセルのヘッダーと共に配置されます。ヘッダーのみが変更される可能性があり、ユーザーデータ自体は変更されません。

要約すると、現時点では、着信パケットは2つの部分に分割されています。ヘッダーはパーセルに配置されてルックアップブロック(より正確には、パケットの最初の256バイト)に送信され、残りはSRAMバッファーに配置されます。

先に進みます。Lookupブロックはマルチコアチップであり、複数のPPE(パケットプロセッサエンジン)で構成され、転送テーブルを格納する特別なRLDRAMメモリを備えています。 Lookupブロックは、受信データとその構成内のすべてのPPEのバランスを取ります。パーセルを受信すると、ルックアップブロックはパーセルをPPEに送信し(PPEからM2Lヘッダーを削除した後)、処理を開始します(この場合、ソースパケットのヘッダーの処理と言えます)。

最初に、IPv4パケットのルーターはチェックサムをチェックし(IPv6にはチェックサムフィールドがないことを思い出してください)、パケットで指定されたチェックサムとPPE自体によって計算された量が一致しない場合、パケットはドロップします。 (Lookupブロック自体はパケットをドロップせず、それらをマークし、バッファリングブロックに送信します。バッファリングブロックは既にパケットをドロップします)。チェックサムが正しい場合、ヘッダーの処理が続行されます。フィルターが適用されます(ファイアウォールフィルター)、速度制限(ポリサー)、DSCP / EXPによるトラフィック分類(トラフィックは管理者の構成に従って色付けするか、DSCP / EXPフィールドを書き換えることができます)、次ホップを検索します。 RAGまたはECMPを使用する場合、RPFチェックを実行し、発信インターフェイスを決定するためにハッシュが計算されます。最終的に、元のパッケージヘッダーは小包でしたが、変更が行われ(ttlフィールドが必ず変更され、ipv4ヘッダーのチェックサムが再計算されます)、小包がバッファリングユニットに送り返されます。新しいL2M(LU to MQ)ヘッダーがパーセルに追加されます。これには、パケットが入るべきキューの番号が含まれています。

キューは、スイッチングファクトリまたは出力インターフェイスに向かうことができます。この場合、出力インターフェイスは別のPFEの責任範囲内にあるため、L2Mヘッダーは、スイッチングファクトリの側に送信するキューの番号を示します。

発信インターフェイスがL2Mヘッダーに加えて別のPFE上にある場合、別のヘッダー-FABが表示されます。このヘッダーには、パッケージクラス、リセット優先度、およびネクストホップIDに関する情報が含まれています。この情報は、パケットをスイッチングファクトリの側にキューイングするため、およびリモートPFEのLookupブロックに必要です(そうでない場合、PFEは再びネクストホップを検索する必要があります)。

さらに、Lookupブロックは、パーセル、L2M、およびFABヘッダーをバッファリングブロックに戻します。このデータはLIブロック(ルックアップ入力ブロック(バッファリングブロックのサブブロック))に分類され、FABとパーセルをオフチップメモリ(DRAM)に配置し、対応するソースパケットセグメントをOnChipからOffChipメモリに転送し、このデータの位置へのポインタをOffChipメモリに格納しますスイッチングファクトリへのディスパッチのためにキューに入れられます。

データは、要求/応答スキームに従って割り当てられたPFEに送信されます。最初に、発信PFEはデータ転送要求をリモートPFEに送信します。リモートPFEからデータを受信するための同意を得た後、発信PFEは、スイッチングファクトリへのすべてのリンクのバランスを取りながらデータの送信を開始します。データは、Jセル(64バイトセル)の形式でスイッチングファクトリを介して転送されます。転送を開始する前に、発信PFEはOffChipメモリ、パーセル、およびFABに保存されているパケットをJセルに分割し、ヘッダーを添付します。ヘッダーには、発信PFE、宛先PFE(PFE ID)、シーケンス番号に関する情報が含まれます(リモートPFEがこのシーケンスからソースパケットとチェックサムを再構築できるようにします。J出力ストリームは、ファブリック出力ブロックによってファブリックファクトリに送信されます。各セルFOは転送要求を送信し、応答を受信した後にのみ送信を開始します。このメカニズムは、スイッチングファクトリの過負荷を防ぐように設計されています(要求に対する応答が受信されるまで送信は実行されません)。

パケットが着信インターフェイスからスイッチングファクトリに至る経路を把握しました。次に、スイッチングファクトリから発信インターフェイスへの2番目の部分に移りましょう。発信PFEについて説明します。

PFEにはFabric入力ブロックがあり、スイッチング工場からJセルを受け取るのは彼です。 FIは、Jセルからのパーセル、FAB、およびパケットの残りを再構成し、その後パーセル、FAB、およびM2Lヘッダーがルックアップブロックに送信され、元のパケットの残りがオフチップメモリに書き込まれます。

FABのLookupブロックは、ネクストホップIDを認識し、小包内のパケットヘッダーを分析し、arpレコードを使用して実際のネクストホップアドレスを見つけ、必要に応じてvlan-tag(または2つのタグ)を追加し、mplsラベル(ラベル)をハングアップします)当然、発信LookupブロックはQOS、フィルター、ポリサーなどのルールを適用し、発信パケットのヘッダーを変更することもできます。これらの操作の後、Lookupブロックは、パケットが入るキューを示す新しいL2Mヘッダーを作成し、パーセルとL2Mヘッダーをバッファリングブロックに送信します。

パーセルブロックとL2Mのルックアップから、ヘッダーはバッファリングブロックのLI(ルックアップ入力)サブブロックに移動します。このブロックは、パーセルをオフチップメモリ(パケットの残りの部分が既に格納されている)に送信し、インターフェイスに送信するためのキューへのポインターを送信します。このパッケージを配置するキューは、ルックアップブロックから受信したL2Mヘッダーに示されています。

パケットをネットワークに送信する番になるとすぐに、Wan出力(WO)ブロックはParcelとパケットの残りをOffChipメモリから取得し、それらを1つのパケットに収集して、発信インターフェイスのコントローラーに送信します。コントローラはパケットのチェックサムを計算し、ネットワークに送信します。

REとの間で送信されるパケットの場合、処理は多少異なります-スイッチングファクトリに送信する代わりに、パケットはラインカードCPUのキューに入れられ、フィルターとポリサーがパケットに再度適用され、その後、パケットは内部経由でREに送信されますギガビットスイッチ。

追加がある場合は、PMにご記入ください。ご清聴ありがとうございました!