パリの年次テーマフォーラムIEEE International Memory Workshopで、当社の専門家が、相転移 (相変化メモリ、PCM)に基づくメモリのプロトタイプを発表しました。 各メモリセルには3ビットのデータが含まれています。 テストサンプルは90 nm CMOSプロセステクノロジを使用して作成され、32 Mビットの容量を持つアレイとして提示されます。

開発者によると、このようなメモリは数百万の書き込みサイクルに耐えることができるため、非常に有望です。 同時に、通常のフラッシュメモリ-3000サイクル以下の書き換え。 PCMメモリの速度は、RAMの速度とほぼ同じです。 開発を量産に向けて開始できる場合、これにより、普遍的な記憶を得ることが可能になり、それほど遠くない将来になります。 さて、現在同社はSSDにPCMチップを使用するとともに、NANDフラッシュをベースにしたSSDにバッファメモリを使用する予定です。

興味深いことに、PCMメモリだけでは新しいものではありません。 しかし、この開発は、主な問題である低記録密度のため、まだ広く配布されていません。 3ビットPCMセルはこの問題を解決します。 以前、IntelとMicronは、3D XPointメモリの形式で多層3D構造を導入することにより、PCMメモリの低記録密度の問題を解決しようとしました。 はい、これは問題の解決策でもありますが、3ビットメモリは安価で、製造が多少簡単です。 さらに、単層構造は多層構造よりも信頼性が高く、後者の場合、大量生産には大量の欠陥要素のリスクが伴います。

PCMメモリはどのように機能しますか?

このタイプのメモリで使用される化合物には、2つの物理状態があります-アモルファス(明確に定義された結晶構造なし)と結晶(この構造がはっきりと見える場所)です。 ある状態から別の状態への遷移は、電流が化合物に印加されると発生します。 高抵抗のアモルファス状態はバイナリ0を表すために使用され、低レベルの抵抗の結晶状態は1です。

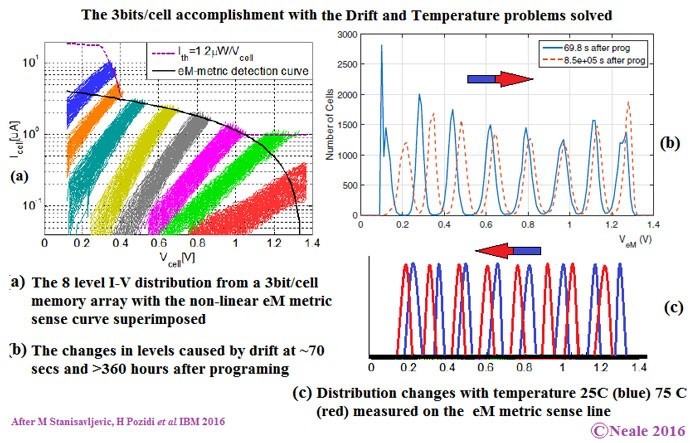

0または1をメモリに保存するには、電気信号を使用する必要があります(それぞれ0と1に対して強い信号と中信号)。 少しの情報を読み取るには、低電圧を使用する必要があります。 メモリセル内で初期のアモルファス状態から結晶状態へと大幅に移動する物質の体積は、印加される電流強度に依存します。 このようなメモリからの読み取りは、低電流を使用して行われます。 1つのセルに3ビットを書き込むには、かなり複雑な8レベルの信号を使用する必要があります。

前述のように、さまざまな研究チームはメモリセルに1ビットの情報を保存しようとしました。 しかし、今では、当社の専門家がセル内の3ビットを節約することができました。

PCMメモリに対する温度の影響

新しい開発では2つのアプローチを使用します。 1つ目は、細胞内の記録レベルを決定するための基準信号の開発です。 2つ目は、録音レベルのプログラミングに特別な方法を使用することです。 以前は、PCMメモリは、それを操作する一定の複雑さに加えて、別の問題-温度への露出-を抱えていました。 このため、時間の経過とともに、セルのレコードレベルが「浮動」し、情報が読みにくくなりました。 現在、当社のスペシャリストがこの問題を解決し、温度は以前ほど深刻な問題を示していません。

この技術の商用利用についての話はありませんが、近い将来、おそらく新しいタイプのPCMメモリが標準になるでしょう。 最初は、いくつかのテストサンプルをリリースし、商用システムの生産を手配する予定です。