インテルは、Xeon E5-2600 v4プロセッサー(Broadwell)とアルテラArria 10 FPGAで構成されるデュアルチップ開発プラットフォームの出荷を開始しました。この情報は、中国で開催されたIDF 2016カンファレンスでのスピーチで、ダイアンブライアント副社長によって表明されました 。 そのようなハイブリッドの助けを借りて、同じ電力消費と周波数で性能を70%向上させることが可能になると想定されています。 インテルとアルテラの協力の成果は、最初の1年とは大きく異なりますが、 プロトタイプの5Gプラットフォームですでに見られました。FPGAとインテルコアはそこにまたがりました。 そして今-新しいデュエット。 将来の計画には、両方のコンポーネントを1つのチップに完全に統合することが含まれます。 ハイブリッドの最初の消費者は、最大のクラウドサービスとデータセンターになります。 Intelの予測によると、2020年までにデータセンターのサーバーの最大30%にFPGAを搭載したプロセッサが搭載される予定です。

インテルは、Xeon E5-2600 v4プロセッサー(Broadwell)とアルテラArria 10 FPGAで構成されるデュアルチップ開発プラットフォームの出荷を開始しました。この情報は、中国で開催されたIDF 2016カンファレンスでのスピーチで、ダイアンブライアント副社長によって表明されました 。 そのようなハイブリッドの助けを借りて、同じ電力消費と周波数で性能を70%向上させることが可能になると想定されています。 インテルとアルテラの協力の成果は、最初の1年とは大きく異なりますが、 プロトタイプの5Gプラットフォームですでに見られました。FPGAとインテルコアはそこにまたがりました。 そして今-新しいデュエット。 将来の計画には、両方のコンポーネントを1つのチップに完全に統合することが含まれます。 ハイブリッドの最初の消費者は、最大のクラウドサービスとデータセンターになります。 Intelの予測によると、2020年までにデータセンターのサーバーの最大30%にFPGAを搭載したプロセッサが搭載される予定です。

ここで言及する価値があるのは、昨年、IntelとeASICが、特定の事前に指定された負荷用にプロセッサをカスタマイズするためのXeon + ASICプラットフォームを作成する共同プロジェクトを開始したことです。 本当に、より多くのXeonsがあり、それぞれに違いがあります!

猫の下-FPGAアルテラArria 10に関するいくつかの情報。

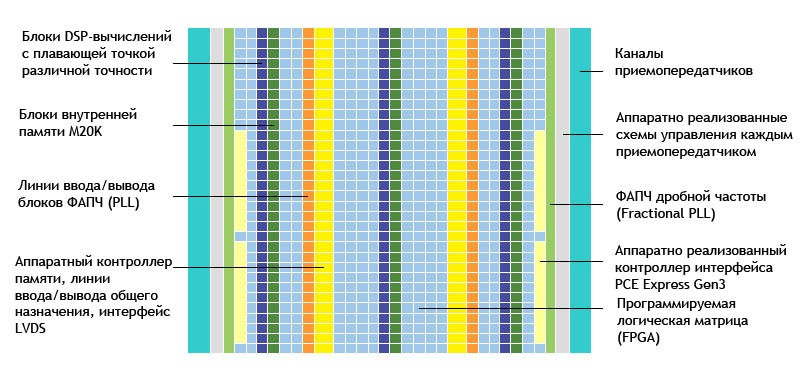

Arria 10 FPGA

Arria 10ファミリの新しいFPGAは、20 nmの技術標準に従って製造されています。 Arria 10ファミリデバイスは、前世代のFPGAよりも最大40%電力効率が低く、1,500 GFLOPS(10億浮動小数点演算)の容量を持つ浮動小数点信号用のハードウェアベースのデジタル信号処理ユニットを備えた業界で唯一のプログラマブルロジック回路です。

- 最大28.3 Gbpsの統合トランシーバ帯域幅

- 2666 Mbpsの高性能外部メモリインターフェイス

- 浮動小数点DSPハードウェアブロックがIEEE 754仕様に適合

- 最大96のトランシーバーチャネルが、最大3.6 Tbpsのスループットでシリアルデータパスを提供します。

FPGA機能のプログラムによる使用は、 Altera OpenCL SDKを通じて実装されます。