この記事では、浮動小数点数、特にプログラマブルロジック集積回路(FPGA)での特殊なFP23フォーマットの実装に焦点を当てます。 特定のプロジェクトの一環として、特定のニーズに最適な浮動小数点データ形式を実装するというアイデアがありました。 その結果、このアイデアは実際のプロジェクトに変わり、その後、デジタル信号処理のいくつかの興味深いタスクでアプリケーションを見つけました。 この記事では、ザイリンクスFPGAに浮動小数点データ形式を実装する際の主な問題について説明し、FP23形式での基本的な数学演算について検討します。 また、記事の最後にプロジェクトのソースコードがあります。これは、タスクで自由に使用したり、それに基づいて同様のデータ形式を実装したりできます。

データ形式

浮動小数点数は、最新の信号プロセッサ、ビデオカード、さらにはFPGAでも積極的に使用されています。 IEEE 754標準に従って、それらは指数(指数)、仮数、および記号の組み合わせとして表されます。 IEEE 754標準の数値には32ビット( float )があります。 明確にするために、フロートへの数値の書き込みは通常の形式で書き込まれるか、数学的操作と数値の変換後に正規化された形式に縮小されます。 可能な値の範囲は、仮数と指数のビット数によって異なります。 フロートは、固定相対精度と可変絶対精度によって特徴付けられます。 float形式の数値の主な長所と短所:

- +非常に広範な可能な値が提供されます。

- +高精度の計算を実現。

- -非常に大きな数値をグリッドの可能な値に丸める。

- -互いに異なる数を何度も合計すると、精度が低下します。

- -FPGAでの実装とアプリケーションの複雑さ。

最新のFPGAチップでは、浮動小数点数の実装は難しくありません。 大手メーカー-ザイリンクスおよびアルテラには、標準に従ってフロートを実装する既製のSOFT IPコアがあります。 アルテラの最新ファミリには、DSPブロックでIEEE 754フォーマットを実装するHARD IPコアがあります。

デジタル部

デジタル信号処理の数学的操作とタスクを実行するための主要な要素ベースは、高度なFPGAファミリです。 この作業は、構成可能なセルのベクトルのブロックを含むFPGA会社ザイリンクスで実行されます。 まず、これらはデジタル処理および数学の汎用ブロックです-DSP48E1(Virtex-6シリーズおよび7ファミリのFPGA用)およびDSP48E2(UltraScaleファミリのFPGA用)。 これらのブロックにより、数値の加算と減算、シフトと転送、高速乗算、累積乗算(MACC)、チェックサム検索などの機能を実行できます。 最新のFPGAのDSP48セルでは、多くのタスクが実行されます-CICおよびFIRフィルターの開発、FFT / IFFTの高速計算、デジタル周波数シンセサイザー(DDSおよびCORDIC)の実装、データを提示するためのさまざまな形式の作成、およびそれらの操作セット。

FPGAの2番目の基本コンポーネントはブロックメモリです。 ザイリンクスFPGAの場合、これらはRAMB36E1(またはRAMB18E1)セルです。 これらは、同一ブロックの列の形で水晶内部に実装された2ポートメモリ要素です。 内部メモリの列数は、チップのサイズに依存します。 メモリブロックの最大容量は36Kビットですが、それぞれ18Kビットの2つの独立したブロックとして構成できます。 メモリは、1〜72ビットのデータ幅で使用できます。 FPGAブロックメモリの空きリソースがない場合、特別なSLICEMセルで分散メモリを使用できます。 Ultrascale FPGAの場合、このようなメモリの量は最大512x1で、バスの深さとビット深さを再構成する可能性があります。

問題の声明

アナログおよびデジタルパーツの実装に関する上記の機能を考慮すると、タスクは次のように形成されます。 ADCチップを使用してFPGAチップに入力するデータのビット容量を16ビットにします。 FPGAが最小チップKintex-7を選択したため。 タスクは、16ビットの符号付き整数FIX16を特殊な浮動小数点形式FP23に変換し、その逆を行いながら、水晶リソースを最小限に抑えてFPGA内の最大処理速度を確保することです 。 また、加算、減算、乗算などの一連の基本的な数学演算を指定して実装する必要があります。

FP形式の実装

FP23は、浮動小数点数を表すための特別な形式です。 IEEE 754標準とは異なり、FP23形式の語長は32ビットではなく、23ビットのみです。 次の簡略化された形式の式は、FP形式での数値「A」の表現を反映しています。

FP23形式の仮数は、17ビットの正数です。 すべての変換の結果として、常に正規化された形式で表示されます。 仮数の最上位ビットは常に「1」です。 クリスタルリソースを節約し、書き込みを簡素化するために、仮数の17番目のビットは、パックされた結果の23ビットワードに表示されません(図を参照)。 したがって、算術演算を計算し、ある形式から別の形式に変換する場合、仮数が正規化され、値216が16ビットのゼロ以外の数値に加算される必要があることを覚えておく必要があります。仮数がどれだけ乗算されるか。 残りの1ビットは符号の下で強調表示され、ゼロの値は正の数に対応し、単一の値は負の数を決定します。 したがって、FP23形式の数値Aは、3つのビットフィールド「exponent」 (EXP(A)) 、「sign」 (SIGN(A)) 、および「mantissa」 (MAN(A))によって記述されます。

表1は、データのビット深度、仮数と指数の可能な値の範囲などを示しています。

そのため、FPGAで浮動小数点データ形式を開発する最初のステップは、FPGA内部の最大処理速度を確保しながら、符号付き固定桁整数をFP23浮動小数点形式に変換することです。 2番目のステップは、FP23形式から固定小数点形式への数値の逆変換であり、出力を特定の除算係数にスケーリングする機能があります。 最後に、第3段階で、FP23形式の能力を最大限に活用するには、加算、減算、乗算などの数学演算を実装する必要があります。

FP23モジュールについて説明する前に、「なぜデータ容量が23ビットの形式になっているのですか?」という自然の質問に答える必要があります。答えはいくつかのコンポーネントで構成されています。 まず、1ビットが文字に使用され、残りの15ビットが整数部分に使用されるため、仮数と文字は少なくとも16ビットを占有します。 指数の場合、式のオフセットを考慮して、最低5ビットが必要です。 指数に割り当てられるビットが多いほど、結果は大きくなります(可能な値の範囲が拡張されます)。 指数が6桁であり、仮数が16ビット数として表され、1桁が符号に割り当てられているとします。 次に、FP23形式で数値を表すために、正確に23ビットが使用されます。 仮数の非表示ビットを使用すると、非ゼロ値の場合は1に、2進数のゼロ値の場合は0に等しい場合、ビット容量は24です。

さらに、値「23」はランダムに選択されませんでした。 将来、FPGAメモリは複素数値のベクトルを保存するために必要です。 隠しビットを表示しない値のペアの合計容量は46であり、隠しビットは48です。これは、幅がちょうど3つのRAMB18E1メモリブロックに適合します。 また、値のペアに対して、DSP48E1¬ブロックの追加機能を使用できます。2つの数値の迅速な比較、パリティ、SIMDモードでの迅速な合計です。

FIX16からFP23への変換

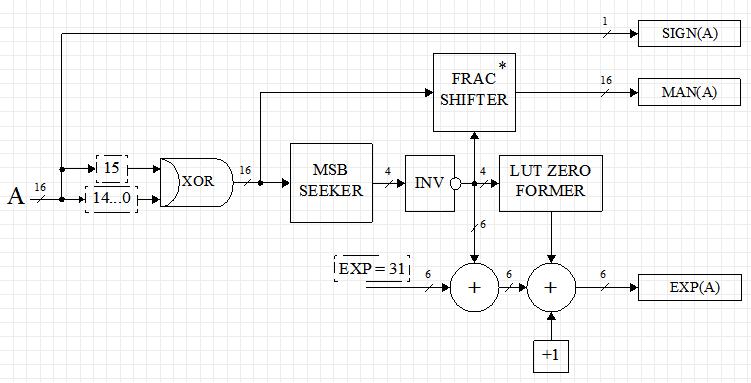

データを整数文字型FIX16からFP23形式に変換するには、FPGAチップロジックと組み込みDSP48E1乗算器を使用する必要があります。 この図は、データをFP23形式に変換するブロック図を示しています。

DSP48E1ブロックファクターの最大ビット深度は、それぞれ25および18であり、最上位ビットが重要です。 DSP48E1モジュールの符号に関係なく数値を乗算するには、入力データの有効ビット深度を1ビット減らします。 コンバーターはRAMB18E1ブロックメモリを使用しません。

したがって、数値の符号を見つけるには、入力データの最上位(符号付き)ビットを取得する必要があります。 FPGAプリミティブに基づく仮数MAN(A)の検索アルゴリズムは次のとおりです。

- 入力番号のモジュールを取得します(操作「排他的OR」)。

- 最上位ビット(MSB SEEKER)を検索し、

- 最上位ビットで仮数のシフト値を形成し、

- 数値のモジュラスとシフト値を乗算して、正規化された仮数(FRAC SHIFTER)を取得します。

指数EXP(A)を検索するには、次が必要です。

- 入力番号のモジュールを取得します(操作「排他的OR」)。

- 最上位ビット(MSB SEEKER)を検索し、

- 数値「32」から有効ビットの反転インデックスを減算し、

- 0以外の入力値を検索するロジックを考慮して、結果に1を追加します(LUT ZERO FORMER)。

仮数は実数のモジュラスに符号なし入力数のシフトが依存する「マスク」を乗算することで取得されるため、それを見つけるにはDSP48E1ブロックが必要です。 仮数を検索して形成する手順は、FRAC SHIFTERノードで発生し、図に示されています。

ご覧のとおり、仮数は2つの段階で形成されます。 最初の段階では、入力番号の論理リソースLUTを使用して、2 16-MSBの乗数が作成されます。 第2段階では、入力データにDSP48E1ノードのシフト量が乗算されます。 乗算器の出力で、正規化された仮数が形成されます。 説明によれば、符号なしの数値を乗算する場合、DSP48E1ブロックの要因の1つの最大ビット深度は17であるため、仮数と生成されたシフトのビット深度を大きくすることはできません。 この制限により、FP23形式の数字の仮数のビット容量は17になります。非ゼロの数字の仮数の最上位ビットは1です。予約され、結果の仮数の検索操作で使用されますが、正規化形式の数字の出力表現には表示されません。 このビットを推測してワードの一般的な表現で使用すると、出力ワードのビット深度は24ビットになります。

消費される水晶リソースの量を減らすために、DSP48E1ブロックを除外できます。 次に、仮数検索ノードが高速シフトレジスタ(バレルシフタ)に変換されます。 一部のFPGAクリスタルでは、DSP48E1の数が少なく、リソースの余分な浪費が重要であるため、FP23ブロックを使用する場合、1つまたは別のオプションを選択できます。 さらに、高速シフトオプションの場合、完全な変換操作の合計遅延が1クロックサイクル短縮されます。

出展者を検索するための加算ノードは、完全なバイナリ加算器の形式で作成され、その実装には、ベースセルSLICELおよびSLICEMに含まれる論理コンポーネントMUXCY、XORCYおよびCARRY CHAINが使用されます。 詳細な説明は、プログラマブルロジックに関する文献に記載されています。

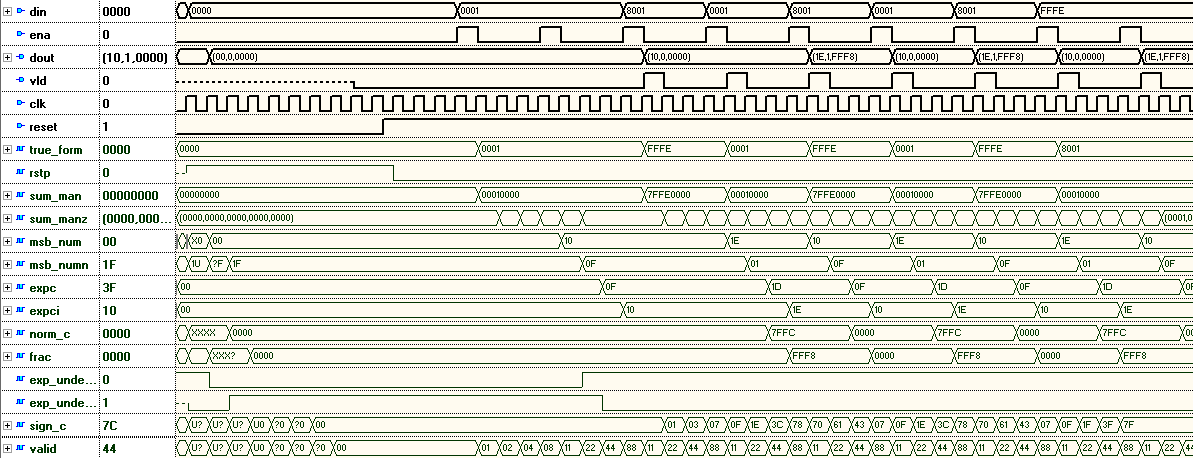

タイミングチャートの例

FIXからFLOAT FP23へのデータの変換:

DIN-入力データ、16ビット。 DOUT-3つのフィールド{EXP、SIGN、MANT}に分割されたFP23形式の数値。

DIN-入力データ、16ビット。 DOUT-3つのフィールド{EXP、SIGN、MANT}に分割されたFP23形式の数値。

FP23からFIX16への変換

データをFP23形式からFIX16に変換するには、4つのステップが必要です。

2進数の符号付き数値検索アルゴリズムは、いくつかの連続したアクションで構成されています。

- 指数EXP(A)から値SCALE(出力データのスケーリング)を引きます。

- シフトマスク2(EXP(A)-SCALE)を形成します。

- 隠しビットIMPL(A)を仮数に追加し、結果にシフト量を掛けます。

- 操作「排他的OR」を使用して、番号SIGN(A)の符号を考慮します。

このスキームでは、FP23形式への直接変換のノードに関して、FPGAリソースを節約するために、DSP48E1ブロックをSLICEMセルで実行される高速シフトレジスタに置き換えることができます。

乗算

FP23形式の数値の乗算は、最も単純で最も論理的な演算の1つです。 ハードウェア乗算アルゴリズムは、次のように実装されます(図を参照)。

- ノードDSP48E1の仮数乗算、

- 仮数の正規化(最上位ビットの値に応じて、ビット[32 ... 17]または[31 ... 16]を仮数として使用)

- 出展者の追加

- 指数の合計から数値16を引く

- 仮数積の33番目のビットが「0」の場合、結果の指数から別の1が減算されます。

- 「排他的OR」操作を使用した作品のサインの決定。

ゼロ数による乗算の論理はスキームに反映されませんが、アルゴリズムにより、入力数の指数がゼロに等しい場合、出力結果もゼロに等しいという事実に還元されます。 FPGAでは、LUTベースユニットのANDおよびOR論理関数を使用してゼロ検索が編成されます。

入力数の仮数の隠れビットを説明するために、指数の合計から数値16が減算され、指数が増加します。 浮動小数点の数値を乗算するノードの加算器と減算器も、バイナリ全加算器スキームに従って実装されます。

加算と減算

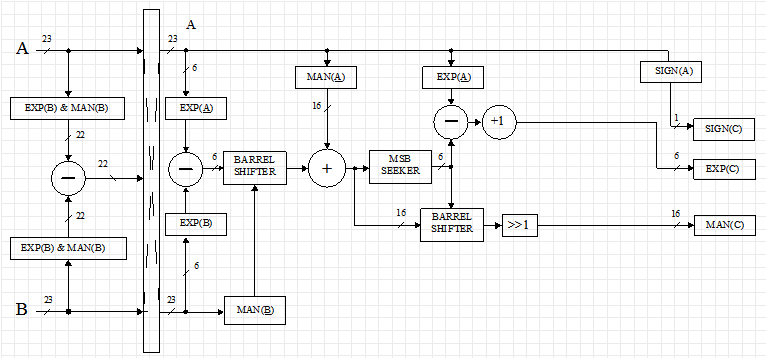

FP23形式の数値の加算と減算は、最もリソースを消費する操作です(図を参照)。 FP23形式での数値の追加は、次の基本的な段階で構成されています。

- オペランドを1つの指数に縮小(アライメント)、

- 仮数の追加

- 結果の正規化(16ビットの仮数が「1」に等しくなるような指数の選択)。

ハードウェア追加アルゴリズムは次のように実装されます。

- オペランド「A」と「B」は、| A | <| B |の場合、モジュロで比較され、数値が交換されます。

- オペランドの指数の差が計算され、その結果により、数字「B」の仮数を右にシフトして数字を1つの指数にするために必要な桁数が決まります。

- 指数の差に従って、数「B」の仮数に乗算される数が形成されます。

- 乗算の結果が数字「A」の仮数に加算されます。

- 受信した番号では、MSBの最上位ビットの番号が決定され、番号が形成されます。

- 仮数の合計に数値を乗算することによる仮数の正規化、

- 数の指数EXP©= EXP(A)-MSB + 1。

減算は加算と同様に実装されます。 唯一の違いは、減算されたオペランドの符号SIGN(B)が反転されることです。 DSP48E1ユニットは、高速シフトレジスタに置き換えることもできます。

資源

各ノードの操作の合成結果と伝搬遅延を表2にまとめます。この表は、最も単純で最速の操作がFP23形式の2つの数値の乗算であることを示しています。

すべてのノードの合成後の占有リソースの量は、共通のログファイルに記録されます。 fp23乗算器の合成結果の例:

Top Level Output File Name : fp23_mult_m1.ngc Primitive and Black Box Usage: ------------------------------ # BELS : 106 # GND : 15 # INV : 1 # LUT2 : 25 # LUT3 : 16 # LUT4 : 6 # LUT6 : 14 # MUXCY : 14 # VCC : 1 # XORCY : 14 # FlipFlops/Latches : 75 # Shift Registers : 8 # SRLC16E : 8 # DSPs : 1 # DSP48E1 : 1

ソースコード

FP23形式のすべてのノードはVHDL言語で記述されています。 利便性と検証のために、FPGAの浮動小数点で実装された操作の機能を含む小さなプログラムがC ++で記述されています。 その助けを借りて、指数と仮数の他の次元を持つ他の浮動小数点形式をデバッグおよび実装できます。

VHDLでデータを読みやすくするために、浮動小数点形式で数値を定義する型が作成されています。 FP23のすべてのコンポーネントとタイプは、fp_m1_pkg.vhdファイルに収集されます

type fp23_data is record exp : std_logic_vector(5 downto 0); sig : std_logic; man : std_logic_vector(15 downto 0); end record;

RTL記述のソースコード、テストプログラム、および合成結果は、 githubリンクにあります。

テストケース

開発したすべてのノードをテストするために、小さな回路を思いつきました。 これは複素数の乗算器であり、入力と出力ではデータが整数形式で表示され、中間結果は浮動小数点になります。 つまり、入力はFP23形式に変換されます。 この形式では、複素乗算が実装され、結果がFP23から固定小数点に転送されます。 RTL-Viewerのブロック図は次のとおりです。

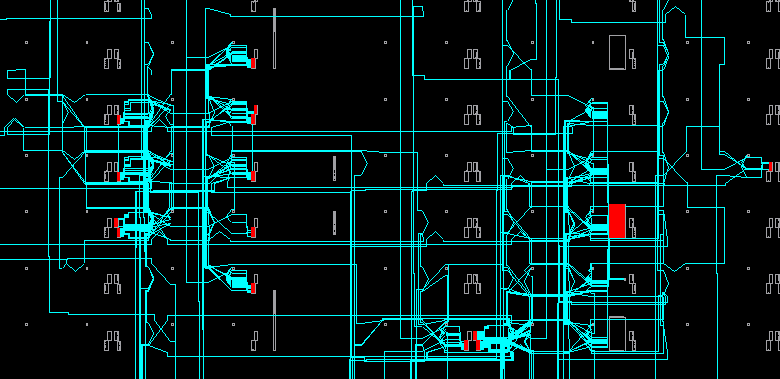

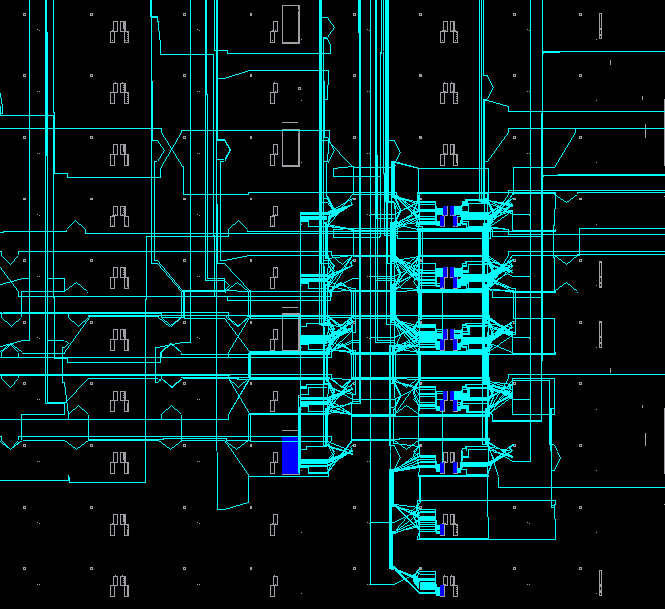

PlanAheadでは、次の図に複素乗算器の配置を示します。 FPGA Kintex-7、 XC7K70TFBG484-1C

プロジェクトの完全なトレースの結果として、 約300 MHzのオーダーの処理周波数が達成されていることがわかります。 実際には、この数値は約30%高くなっています。

FPGA Editorでは、従来のFP23乗算器のブロックは次のようになります。

おわりに

この作業の結果、FP23浮動小数点FPGA用の特殊なデータ形式が開発されました。 従来のIEEE 754形式とは異なり、最大速度でのFPGA処理用に強化されています。 ザイリンクスおよびアルテラの標準ソリューションとは異なり、FP23形式のノードは水晶リソースを大幅に削減します。 FP23の加算および乗算操作は、FIRフィルターとFPGAのFFT / IFFTノードの実装に用途を見出しました。

必要に応じて、仮数と指数の任意のビット深度を持つ特定のタスク用に独自のデータ形式「 FP_X 」を作成できます。 この場合、特定のFPGAの機能と構造を考慮する必要があります。

同様のトピックに関する私の記事:

文学

ご清聴ありがとうございました! 続行するには...