動作しないキーエンスLK-G407レーザー距離センサーを入手した後。 動作しなかっただけでなく、特別な制御ユニットなしでは使用できませんでした。 しかし、センサーには、ミクロン単位の正確な距離測定と、50キログラム/秒の作業速度という興味深い特性があります。 したがって、それを実行するには、センサー自体をより深く掘り下げると同時に、貴重な経験を積む必要があります。

センサーの内部には何がありますか?

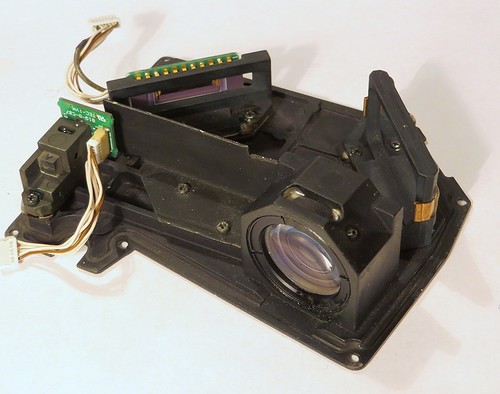

センサーの光学部分は下の写真に示されています:

写真の左側にはレーザーモジュールがあり、その後ろには感光性の定規があり、右側にはレンズとミラーがあります。

設計から、このセンサーは、距離を測定する三角測量方式のレーザー距離計として分類できることが明らかになります。 このような距離計の動作原理は、 ここで詳しく説明されています 。 原則として、それは非常に簡単です-レーザーが照射される物体までの距離を変更すると、レンジファインダーレンズとレーザースポットの間の角度が変化します。 レンズの焦点面に感光性ルーラーまたはマトリックスを設置する場合、最大出力信号の位置によってこの角度を決定できます。 レーザーとレンズ間の角度と距離がわかれば、物体までの距離を判断できます。

この方法の利点は、短距離での非常に高い精度です。特定の条件下では、0.1ミクロンよりも優れている場合があります。

高速で距離を測定することも問題ではありません。高速の感光性ルーラーを使用するだけです。

このような距離計の回路も非常に単純です-デバイスには高周波がなく、一次信号増幅はライン自体にあるためです。

ただし、欠点があります。距離が長くなると、メソッドの精度が急激に低下します。

このセンサーは望遠レンズ(焦点距離約150 mm)を使用するため、センサーのサイズを小さくするために、ミラーがその構成に含まれています。

そして今、センサーの電子機器に移る価値があります。

センサーの2番目の部分は次のとおりです。

そして、ボード自体:

そして他方で:

プリント基板は4層のようです-信号導体のほとんどは外側の層にあり、電力線は内側の層にあります。

すでに述べたように、センサー用のコントロールユニットはなく、センサーなしでは動作しませんでした。 センサー用の回路も存在せず、ケーブルのピン配列とセンサーの供給電圧も不明であったことは明らかです。 結論-リバースエンジニアリングスキームを行う必要があります。

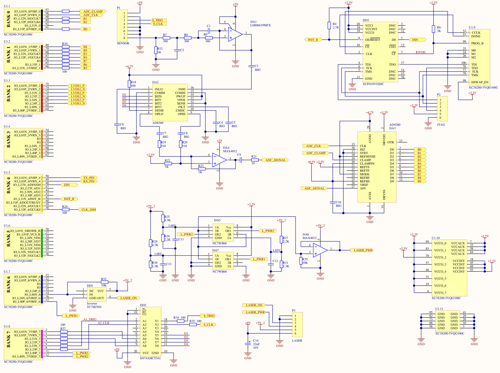

結果はそのようなスキームです:

もちろん、センサー回路全体を描画するのではなく、FPGAに関連する部分のみを把握しました。 回路上の要素の数は、ボード上の数に対応していません。

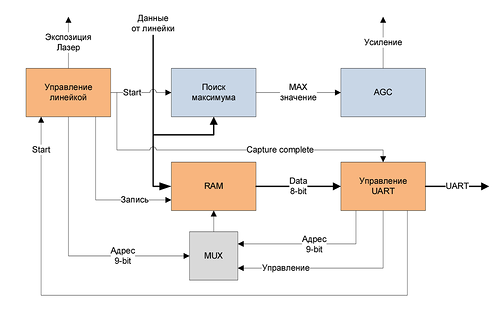

したがって、センサーの構造図:

このことから、センサー全体の動作は、FPGA Xilinx Spartan-3Aと特定のカスタムマイクロ回路という2つのマイクロ回路によって制御されていることが明らかです。 しかし、私は非常に幸運でした-図から、カスタムのマイクロ回路がFPGAのみで接続されていることがわかります。 したがって、FPGA自体がセンサー内のすべての信号を制御できます。

デザイン全体の重要な要素は、感光性ルーラーです。 このラインは明らかにカスタムメイドです。 顕微鏡の下で、その端の1つに碑文が見えます:

25〜512

LI004-02

512はルーラーのピクセル数、25はピクセル幅(ミクロン)であると想定しました。 後で判明したように、私は正しかった。

小さなボードをラインの後ろにはんだ付けします:

ラインからの信号を2倍にするオペアンプと、いくつかの抵抗とコンデンサを備えています。 このボードはコネクタP1に接続します。 図からわかるように、3本の信号線のみがその線に行きます。 それらの1つは、明らかにその出力からのアナログ信号です(別の同軸ワイヤを介して送信されます)。 残りの2行はデジタルであり、ルーラーの制御に使用されます。 回路を分析するとき、私は再び幸運でした-回路に電圧を印加すると、10 MHzの周波数がこれらの線の1つに現れます(4)。 この回線が回線のクロッキングを担当していることがすぐに明らかになりました。 明らかに、定規のすべての制御は残りの行(3)に沿っています。 回線をSTM32F4マイクロコントローラーに接続し、さまざまな信号を回線(3)および(4)に送信し始めました。 判明したように、ルーラーは非常に単純に動作します-ライン(3)に高レベルがある間、露出があります-ルーラーは光を受け取ります。 ライン(3)に低レベルを設定した後、14クロックパルスをラインに適用する必要があります。その後、次の512クロックパルスのアナログ信号を生成します。 ラインは5VおよびFPGA-3.3Vで動作するため、DD2チップを使用してレベルを一致させます。

ラインからのアナログ信号は、ローパスフィルターを介してDA1チップ上に組み立てられたリピーターに送信されます。 次に、信号はプログラマブルゲインAD8369を備えたPGAアンプに供給されます。 このチップの最大ゲインは40 dBであり、入力BIT0-3に目的のコードを設定することにより、プログラムで調整できます。 この超小型回路は差動信号を増幅するように設計されており、その出力も差動であるため、両方の出力はオペアンプDA4に接続されます。オペアンプDA4は信号を2倍に増幅し、単一の信号を形成します。

次に、アナログ信号が10ビットAD9200 ADCの入力に供給されます。 このチップは、 SDRレシーバーからすでに私に馴染みがありました。 この場合、デジタル化する電圧の範囲が(0.5-2.5)Vになるように接続されます。ADC出力からのデジタル化された信号はFPGAに送信されます。

このADCのCLAMP入力に注意する価値があります。 この入力もFPGAによって制御されます。 入力信号の一定成分を特定のレベルにするように設計されています。

データシートからのADCの入力段の回路は次のとおりです。

CLAMP入力に高レベルが印加されると、「CLAMP IN」入力の電圧に等しい出力がアンプ出力とAINに表示されます。

この場合、CINコンデンサは、電圧が等しくなるまで(Uin-Uclamp_in)充電されます。 その後、CLAMP入力はLowに設定され、アンプはADCの動作に何らかの影響を与えなくなります。 このセンサーでは、入力「CLAMP IN」はADCの低い基準電圧+ 0.5Vに接続されています。 したがって、特定の定数成分がDA4の出力に存在する場合、CLAMP機能を使用することにより、ADC動作の結果への影響を排除することができます。

FPGAの最初のテスト構成を作成した後、CLAMP信号を実際に制御する必要があることがわかりました。そうしないと、ADCからの信号に非常に大きなDC成分が含まれます。 私の実装では、ADCを使用してデータがキャプチャされるまで、一度に1ずつ適用するだけでした。

この回路は、多数の供給電圧を使用することを示しています。 センサーに含まれるさまざまな電源とさまざまな平滑コンデンサの図は作成しませんでした。 判明したように、電源ピン(2つのピンを備えた別のコネクタに出力されます)は、TPS62050 DC-DCコンバーターに接続されています。 最大電圧は10Vで、6Vから電子機器はまだ起動していないので、センサーの動作電圧は8Vであると判断しました。

このモジュールで使用されるレーザーダイオードは、別のボードに搭載された電子機器によって制御されます。

私はこのボードの図を描きませんでした。 P3コネクタを介してメインボードに接続します。 ご覧のとおり、レーザーは2本の線に沿って制御されています。 そのうちの1つ(3)は、インバーターを介してFPGAに接続されており、レーザーをオンにする役割を果たします。FPGA出力で低レベルによってオンになります。 レーザー出力を制御するには、別のライン(4)が必要です。 これはアナログラインであり、その電圧を変更するために、回路にはDA5-7マイクロ回路上に組み立てられたDACが含まれています(開発者が完成したDACマイクロ回路を取得するのではなく、なぜこのような混乱した回路を積み上げたのかはまだわかりませんでした)。

ご存知のように、ほとんどのFPGAには不揮発性メモリが含まれていないため、FPGA構成は外部チップに保存する必要があります。 この場合、それはDD3 XCF01-特殊なフラッシュメモリチップです。 オンにすると、FPGAは構成をメモリから自動的に読み取ります。 FPGA自体とXCF01は、P2コネクタに接続されているJTAG回路で接続されています。 その結果、このコネクタを介して、XCF01をインサーキットでプログラムし、FPGAを構成し、デバッグすることができます。

したがって、センサーの電子回路がどのように機能するかを理解し、その回路の一部を取得しました。 これで、実験を開始できます。 FPGAプログラミング。 それ以前は、ザイリンクス製のFPGAを扱っていませんでした。 必要なプログラマーもいなかったので、いくつかのオープンソースプロジェクトを組み合わせて、 自分でやらなければなりませんでした。

プログラマーはうまく機能し、FPGA出力を切り替えるだけで、FPGAで簡単なプロジェクトを実行できました。 しかし、将来的にはコンピューターとの接続が必要になりました。 LVDSインターフェイス(LVDSラインが2.5Vに接続されているポート)と通信したくないので、FPGAとASICを接続する2つのトラックを切断しました。 ボードには、明らかにASICのセットアップまたはテスト用のコネクタがあり、使用できなかったため、2つのトラックを切断し、コネクタのピンをFPGAピンに接続しました。 これで、USB-UARTアダプターをこのコネクターに接続できます。

改訂後のボードのタイプ:

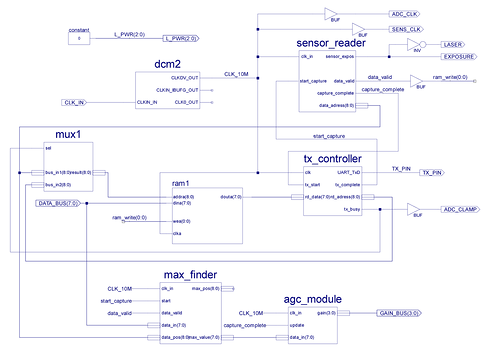

その後、UARTの動作をテストする簡単なプログラムを作成しました。 うまくいきました-コンピューターは、FPGAからUARTを介して送信された単一バイトを正しく受け入れました。 次のステップは、感光ラインからコンピューターへのデータの転送です。 FPGAプログラムの次のブロック図を使用しました。

ISEの回線のタイプ:

プロジェクトの最上位は回路エディターで描画され、それに含まれるすべてのモジュールはVeriolgで書かれています。 プロジェクトの原理は非常に単純です-ADCによってデジタル化されたラインからのデータは、FPGAによってキャプチャされ、RAMに保存されます。 512個の信号要素がすべてキャプチャされた後、それらはUARTを介してコンピューターに送信されます。 すべてのデータが送信された後、サイクルが繰り返されます。 このプロジェクトのsensor_readerモジュールは、ルーラー、レーザー、およびクランプ信号を制御します。 制御は最も簡単な方法で実装されます-クロックカウンターがすべての信号を制御します。 tx_controllerモジュールには、UART送信モジュールが含まれています。 モジュールが外部メモリから受信するデータを転送するように設計されています。

このプロセスでは、ライン上の有用な信号のレベルは大きく変化する可能性があります-オブジェクトまでの距離の変化とその反射係数の変化によります。 信号が小さすぎると測定が不可能になり、信号が大きすぎると測定の精度が低下します。 このため、アナログ信号のゲインを調整する必要があります。 当初、プロジェクトにはUARTレシーバーモジュールが含まれていたため、手動でゲインを変更できました。後で削除し、自動ゲイン制御(AGC)を行いました。

信号最大検索モジュール(「max_finder」)とAGCモジュール自体(「agc_module」)が含まれます。 このモジュールも非常にシンプルです-信号レベルが170未満の場合、ゲインは250を超えると増加します-減少します。

すべてのモジュール、ラインアップ、ADCは10 MHzでクロックされます。 露出時間を5μsに設定します。 したがって、FPGAでの露光プロセスと信号キャプチャ全体は(5 + 51)μsを占有します。 データ転送時間ははるかに長くなります-500,000 bpsのクロック周波数では、512バイトの送信には10ミリ秒かかります。

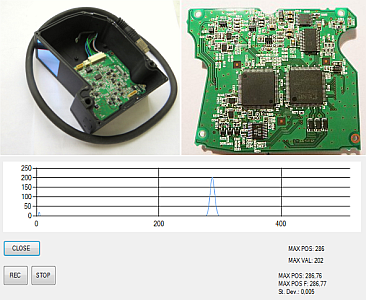

送信されたデータをリアルタイムで表示するために、C#で簡単なプログラムを作成しました。

レーザービームに沿ってオブジェクトを移動すると、最大ピークの位置が変化します。 ルーラーには512ピクセルしか含まれていないため、単純に最大位置を計算すると、測定精度が低くなります。 したがって、最大信号の位置をより正確に測定するには、重心検索アルゴリズムを使用する必要があります。これにより、サブピクセル精度で最大信号の座標を決定できます。

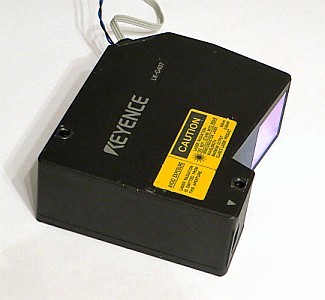

次の式を使用して、ピークの重心を見つけました。

ここで、nはピクセルの総数、Int [i]はiピクセルの強度です。

信号に存在するさまざまなノイズが動作の精度を損なわないようにするには、特定のしきい値を超え、ピーク最大値に近いサンプルのみを処理することが役立ちます。 これは、ゲインが十分でなく、有用な信号がADCスケールの半分を超えない場合に特に重要です。 さらに、ゲインが増加すると、ノイズレベルが増加し、状況が悪化します。 上記のプログラムでは、これが考慮されます。

上の図では、MAX POSはこの式を使用して計算された値であり、MAX POS Fは最後の50回の測定の平均値です。

すでに述べたように、結果の測定周波数は100 Hzであり、UARTを介したデータ転送速度によって制限されます。 ただし、コンピューターで信号を処理する必要はありませんが、これはFPGAでも実行できるため、測定速度を繰り返し上げることが可能です。

その結果、次の構造スキームを持つFPGA用のプログラムが開発されました。

ISEの回線のタイプ:

ご覧のとおり、一部のモジュールは前のプロジェクトから取得されています。

この場合、centroid_finderモジュールは、信号の重心(重心)の位置を計算します。 データ分析の領域を制限するために、最大位置とその振幅の大まかな値がモジュールに送信されます。

これらの値は信号全体を分析することによってのみ計算できるため(つまり、512クロックパルスの遅延で表示される)、デジタル化されたデータは同じ遅延で入力 "centroid_finder"に供給する必要があります。 512クロックサイクルだけデータを遅延させるために、FIFOバッファが使用されます。 fifo_logicモジュールは、最初のFIFO充填に使用されます-充填されていない場合、FIFOからの読み取りを禁止します。

tx_controller_3bytesモジュールは3バイトを順番に転送します。最初のバイトはゼロで、残りの2つには計算された重心位置が含まれます。 50,000ビット/秒の速度では、3バイトの送信には60μsかかります-信号キャプチャとほぼ同じです。 ゼロバイトは、データの同期に使用されます-常に最上位バイトになります。

UARTデータ転送とデータキャプチャは、start_capture信号によって同時にトリガーされます。 この信号は、以前の送信が終了し、重心の新しい位置が計算されると同時に生成されます。 その結果、距離測定とデータ送信の時間は60μs近くになり、16.6 KSPSの座標測定速度が得られます。 これは、センサーの製造元が述べているものよりも少ないです。 これは最小測定時間-20μs(これは50 KSPSに対応)を示しますが、この時間の取得方法は明確ではありませんが、AD9200の最大速度-20 MSPSでも、512ピクセルからの信号キャプチャ時間は25.6μsになるためです。 そして、これは露出時間を考慮しなくてもです。

先ほど言ったように、このセンサーは機能しませんでした。 私の知る限り、問題は振動の激しい工業施設に設置されていて、振動のためにセンサーレーザーが故障したことです(センサーは暗い表面に反応しなくなりました)。

残念ながら、ネイティブダイオードにはマーキングがありませんでした。 レーザーモジュールのレーザーダイオードを購入した5 mWのレーザーダイオードに交換しようとしましたが、しばらくすると強度が低下しました。 最も可能性が高いのは、レーザーモジュールの電子機器がより強力なダイオード向けに設計されていることです(ただし、パルスモードで動作するため、平均放射レベルは非常に低くなります)。

センサーをどういうわけか起動するために、私はレーザーダイオードドライバーを一定の放射モードで動作させました:

センサーのネイティブレーザーダイオードはレーザーモジュールの金属製ハウジングに組み込まれているため、新しいレーザーダイオードをモジュールに簡単に接着する必要がありました。 同時に、使用したダイオードの全体の寸法は、ネイティブダイオードの寸法とわずかに異なりました。そのため、定性的にレーザーモジュールに焦点を合わせることができませんでした。

組み立てられたセンサーは次のようになります。

センサーを使用して距離を測定できるようにするには、距離を調整する必要があります。 センサーから返された結果と実際の距離をリンクする法則を決定します。 キャリブレーションプロセス自体は一連の測定であり、その結果、センサーから特定のオブジェクトまでの一連の距離が形成され、対応する結果が得られます。

センサーと対象物の間の距離は、非常に正確に測定する必要があります。 キャリブレーションのために、 リニアエンコーダーとレーザーセンサー自体を含むスタンドを作成しました。

距離は、エンコーダーの端に取り付けられたプレートまで測定されます。

すべてのデータが収集されたら、Mathcadで回帰分析を実行できます。

その結果、次の式が得られました。

value_mm = 70.0 / Tan(-0.000277757 * max_pos + 0.28355)-366.23554

明らかに、センサー部品の位置に関する定数の値。 わずかなディテールシフトにより、計算された距離が不正確になります。 したがって、すべての部品を非常にしっかりと固定する必要があります。

以下のビデオは、センサーからのデータを処理する方法を示しています。

ビデオの最初の部分は、感光ラインからの信号がどのように見えるかを示しています。 オブジェクトが暗い場合、振幅は変化しませんが(AGCの動作により)、ノイズレベルは大幅に増加することがはっきりとわかります。

ビデオの2番目の部分では、プログラムはセンサーから重心を取得し、距離までカウントします。 また、プログラムはエンコーダーから受け取ったオブジェクトまでの距離の値を受け取ります。 エンコーダー距離の下に、これらの距離の差が表示されます。 動いている場合、差は1 mm以上になります(これは距離とその表示の伝送の遅延によるものです)が、任意の距離での停止中、差は0.03 mmを超えません。

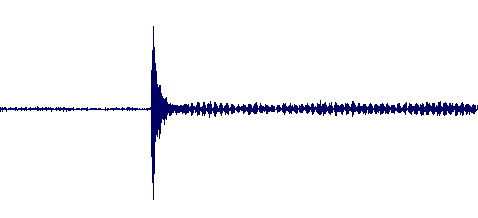

センサーから受信したデータを分析しやすくするために、センサーから受信したデータをwav形式で保存するプログラムを作成しました。 このようなファイルはサウンドエディターで開き、さまざまなフィルターを適用できます。

ここでは、たとえば、変圧器の電源の壁に向けられたセンサーからの信号のように見えます:

電源を入れると、電源が振動し始めたことがわかります。

センサーを音楽が再生されているスピーカーコーンに向けようとしました-処理後、サウンドエディターで実際に聞こえるようになりました。

そのため、非稼働センサーに新しい命を吹き込むことができました(将来のプロジェクトで必要になる可能性があります)と同時に、ザイリンクスFPGAの使用経験を積むことができました。

FPGAのプロジェクト