同期回路の最新の設計ルートでは、2つの主要なタイプの分析が使用されます。時間モデリングと静的時間分析です。

時間的モデリングは主に機能検証に使用され、プラグイン遅延(sdfのファイル、tlf規格など)を使用した論理要素のverilogモデルに依存します。 時間モデリングの利点は、精度と大規模な回路をシミュレートできることです。 トランジスタレベルでのモデリング(スパイスモデリング)の場合よりも確かに精度は低くなりますが、同時にかなり許容可能であり、最も重要なことには、桁違いに高速です。 一時的なモデリングの欠点は、回路ロジックテストの全範囲をチェックするリソースを大量に消費することです。 そして、ほとんどの場合、テストによるロジックの100%のカバレッジは達成できません。

静的時間分析は、ダイナミクスにおける回路の動作をモデル化せず、要素のVerilogモデルを使用しません。 また、静的解析は、回路とその構成要素の機能を扱いません。 静的解析の主なタスクは、回路内のすべての(可能な組み合わせの100%未満の)信号遅延を考慮し、指定された検証ルール(定数)に従って違反を検索することです。 静的解析は、スキームに従って構築された接続グラフに従って、静的解析で実行されるため呼び出されます。 または、より正確には、非循環有向グラフ上。

グラフ理論に入ることなく、有向グラフは有向グラフであると言えば十分です。 グラフのアークには方向があります(ワイヤ内の信号がソースからレシーバへの一方向に「流れる」ように)。 グラフの弧は、要素間の配線であり、要素内の「仮想」信号経路(弧-アーチ)です。 たとえば、要素2 OR NOTには、各入り口から出口までの2つのアーチのみがあります。 グラフの頂点は、要素の入力と出力、および回路の入力と出力です。 その結果、取得したグラフを使用して、頂点を介してグラフアークに沿って通過する信号パスを構築できます。 可能なすべての信号経路が有限である場合、グラフは非循環と呼ばれます。 静的時間分析は、非循環有向グラフでのみ機能し、その結果、有限信号パスでのみ機能します。 たとえば、回路にフィードバックが含まれている場合、信号パスの一部がループし、分析できません。 松葉杖はフィードバックに対抗するために使用されます-CADは、1つ以上の弧を投げることでグラフを非循環にしようとすることができます(原則として、これらは要素内のアーチです)。 結果はフィードバックのないグラフですが、捨てられたアークは分析に関与しなくなります-それらの遅延は計算で考慮されません。

言われたことをよりよく理解するために、テキサス大学オースティン校の学生に与えられた静的時間分析に関する講義から選ばれたスライドについてコメントします。

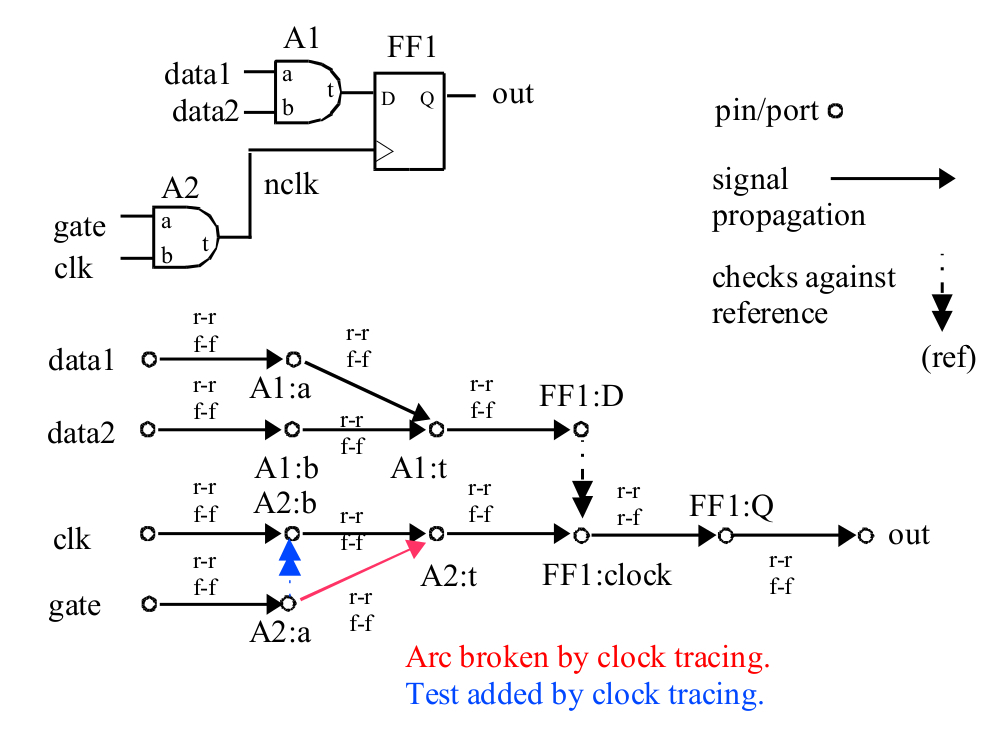

左上隅は、Dトリガー(フロップ)、クロックゲートシャットダウン要素、およびフロップ入力の論理要素で構成される図です。 右上隅はグラフ構築規則です。

•円は、要素の入力と出力、および回路の入力と出力を示します。

•矢印はグラフの端を示します。ワイヤとの接続、およびアーチ(要素内)

•点線の二重矢印は、いわゆるコントロールアーチを示します。遅延は含まれません。静的解析では、信号遅延の計算ではなく、信号の設定と保持(セットアップ/ホールド)の監視に使用されます。

図の下部は、結果のグラフを示しています。 すべての頂点は署名されています(スキームとの一致を簡単に見つけることができます)。 すべてのアークは反転または非反転としてマークされます。たとえば、「rr」と「ff」は立ち上がりと立ち下がりを表し、表示されているアークは信号の反転を伝えません。 アーク(OR-NOT要素のアーチなど)が反転している場合、マークは「rf」と「fr」になります。これは、立ち上がりと立ち下がり、つまり、通過中の信号のポジティブエッジの変化を意味します。アークを介して負に、またはその逆。 すでに述べたように、静的解析の要素の機能は考慮されず、要素の等張性(非反転)関数、または反トーン(反転)関数のみが重要です。

注目すべきこと。 同期回路の信号パスの開始点(過渡プロセスの本質)は、常にインターフェイス信号またはクロックパルスです。 上記の例の回路が大きい場合、グラフ上のアーク全体がクロック入力(clk)のままになります。 また、同期回路内の信号パスのエンドポイントは、インターフェイス、トリガーデータ入力、またはクロックゲート解像度です。 この場合、信号経路の終点は、受信信号のチェックを実行する必要があることを示す1つ以上の制御アーチで終わります。 この例では、クロック入力(FF1:D-FF1:クロック)に対するトリガー情報入力での信号のインストールと保持(セットアップとホールド)、およびクロックゲート要素でのイネーブル信号の同様のチェックがチェックされます。

グラフに定数がどのように反映されるか。 インターフェイスのレイテンシに影響する制約( set_input_delay、set_output_delay、set_drive、set_loadなど)は、グラフの外部アークの遅延値を変更するだけです。 グラフを変更する定数があります。たとえば、 set_disable_timingまたはset_false_pathです 。 多くの制約は、要素のライブラリから自動的に取得されます。たとえば、コントロールアーチの場合-セットアップ/ホールドのチェック。 私は定数に集中したくありません。彼らの理解のために、同じSynopsys DC [2]のドキュメントの説明、またはインターネット上の教育記事、たとえばedacafeやsemiwikiを読むだけで十分です。

次に、遅延を計算するアルゴリズムについて説明します。 静的時間解析では、要素と回路の遅延広がりの2つの極端なポイントのみが考慮されます。クロックに対する信号のセットアップ時間制限をチェックするために使用される最悪のケースと、ホールドを保持するために使用されるベストのケースです。 いわゆる 統計的静的時間分析(SSTA)。これはより知的に質問にアプローチしますが、それについては(特にFPGA開発者はまったく関係ないので)それについてです。

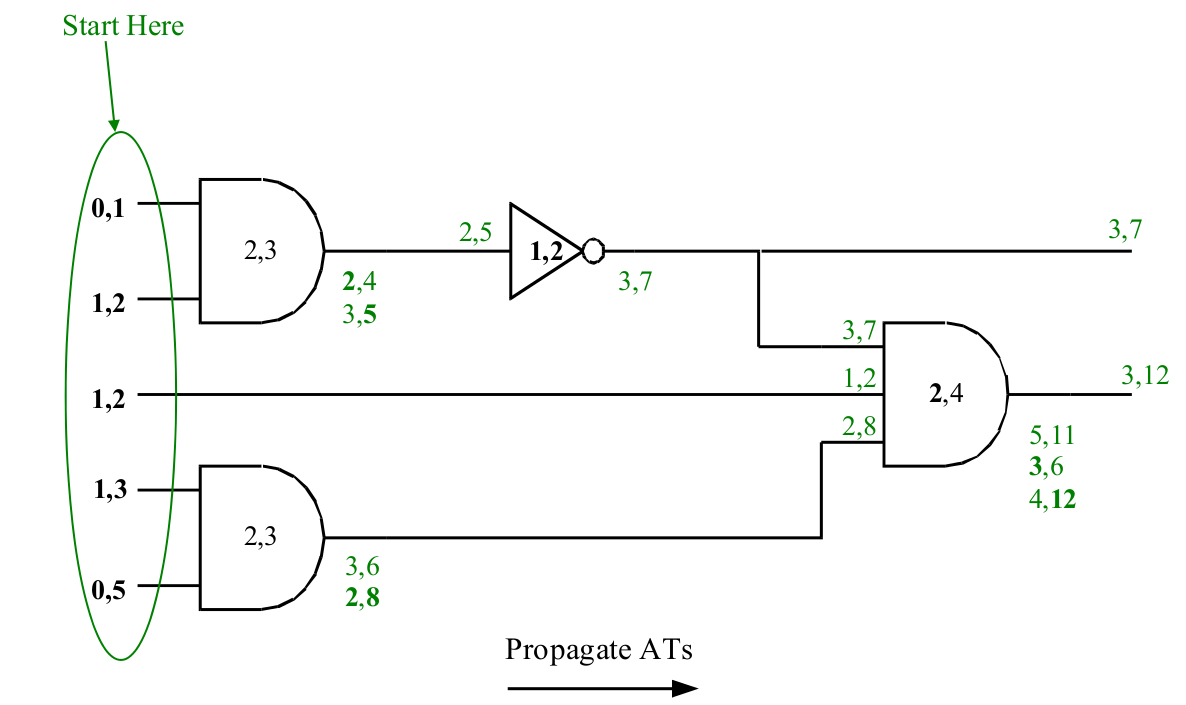

遅延を計算するとき、2つの戦略が使用されます。信号の実際の到着時間(AT-到着時間)の計算、および信号の必要な到着時間(RAT-到着時間)に基づいた計算です。 まず、ATと見なされるもの:

簡単にするために、リーディングエッジとトレーリングエッジの遅延は同じであると仮定します(ただし、通常、両方のオプションに対して個別の計算が実行されます)。 また、グラフの代わりに、ダイアグラム上に遅延を直接描画します。これは視覚的であるためです。 全体として、上記の図では、ワイヤの遅延は要素の遅延に考慮され、コンマで区切られた2桁で示されます:最初の桁は信号の最も早い到着を示し、2番目の桁はその到着の最新の瞬間を示します。 たとえば、入力の「1.2」は、信号が1 ns以上2 ns以下で到着することを意味し、ロジックエレメント内の「2.3」は、2〜3 nsの範囲の遅延を意味します。 入力信号の遅延は、計算のどこで発生しますか? たとえば、 set_input_delayで-minおよび-maxキーを使用して指定できます。 要素の遅延は、要素ライブラリから取得されます(ライブラリ開発者が測定)。 緑色の数字は計算の進行状況を示しています。 左上の要素の場合、2〜3 nsのネイティブ遅延で、出力信号は2〜4 nsで受信できます(要素が最初の入力でトリガーされた場合)。 両方の範囲が単純に加算され(要素の機能が考慮されていないため)、結果は「2.5」または2〜5 ns(つまり、2 nsより早く、5 nsより遅くない)です。

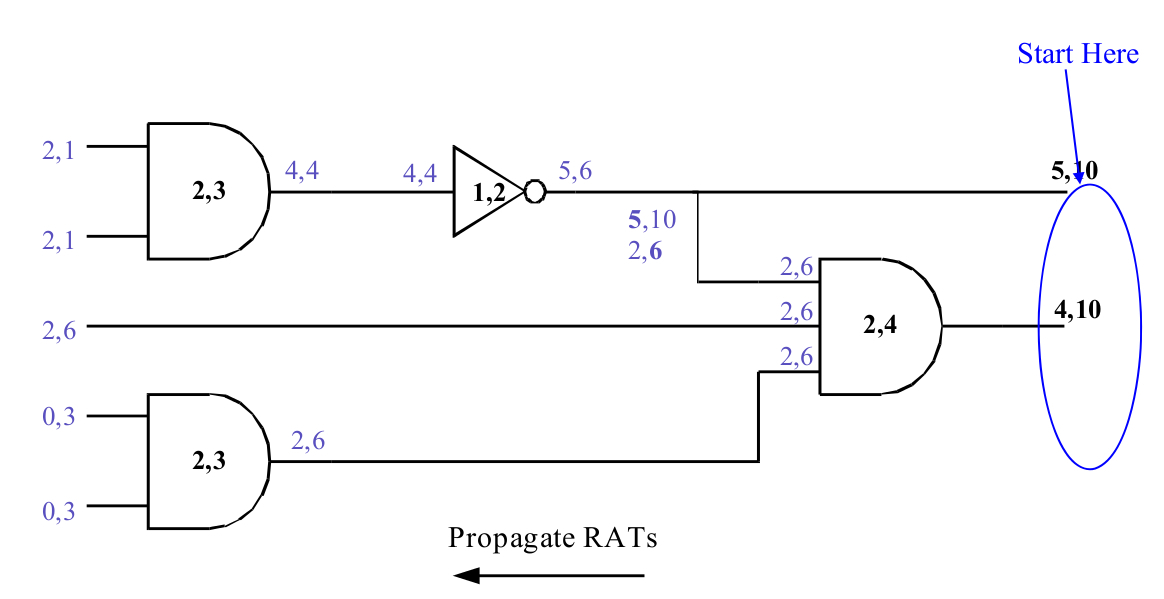

さらに、必要な時間を計算するには:

これで計算は反対方向に実行されます。 出力信号の到着がそれぞれ「5.10」と「4.10」の範囲に制限されているとします。 これらの制限は、 set_output_delayを-minおよび-maxスイッチとともに使用して設定できます。 次に、計算は反対方向に実行されます。たとえば、要素2-4の遅延が範囲4-10から差し引かれた場合、これは信号が要素の入力に2ns以上6ns以下で到達できることを意味します。 この場合、5〜10の制限があったインバータの出力は、5〜6のより厳密な範囲に自動的に制限されます(5〜10と2〜6の交差によって得られます)。

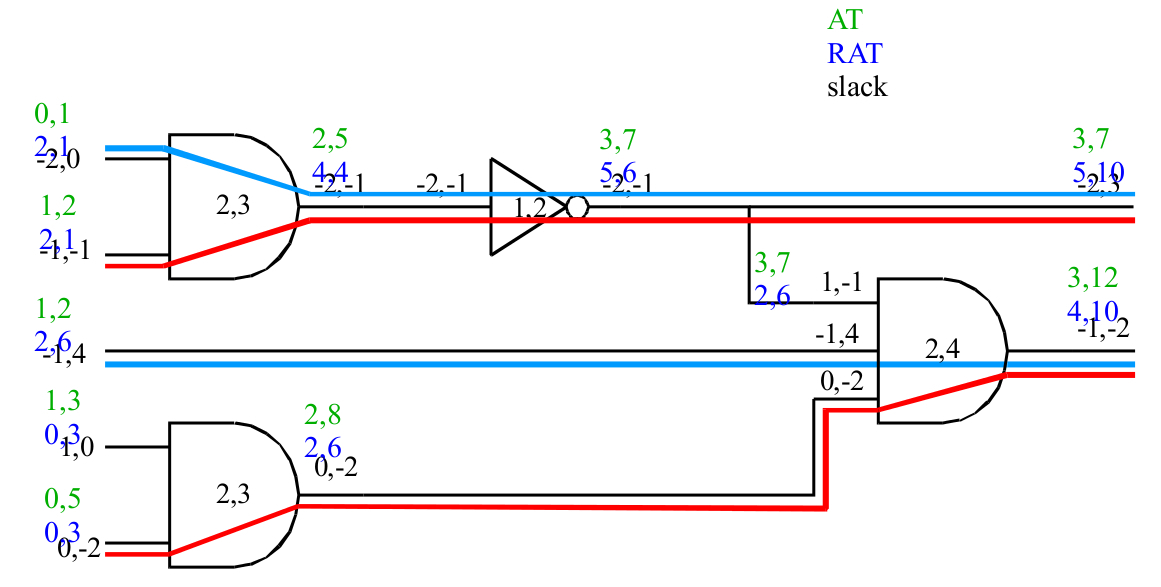

最終的に、必要な信号の伝播時間と実際の伝播時間が受信されると、違反(スラック)を計算することができます。

緑は実際の所要時間を青で示します。 差(スラック)が計算され、図に黒で表示されます。 同時に、差の負の値は違反、正の値-マージンと見なされます。 静的解析の結果のレポートには、実際の時間の計算、必要な計算、差の計算、および合計-METまたはNOT METの 2つのテーブルが表示されます。

結論として、静的時間分析の成功した結果は、設計の操作性を保証するものではないことを付け加えます。 これは、グラフが(定数を使用して)開発者の積極的な参加によって構築され、エラーを伴って構築できるという単純な事実によって示されます。 グラフのエラーは、回路内の制御されていないパスになります。これは、時間制約のチェックによる一時的なモデリング(つまり、インターフェイスでの遅延の使用)によってのみ捕捉できます。 一時的モデリングの違反は、多くの場合、定数のエラーを示しています。 したがって、単純な結論-静的時間分析は機能モデリングに代わるものではなく、それを補完します。

提示された資料が静的時間分析をよりよく理解し、「内部から」それを見て、設計のためにより意味のある定数を書くことを願っています。 さらに掘り下げたい場合は、英語の「ナノメータ設計の静的タイミング解析:実用的なアプローチ」[3]を読むことをお勧めします。

[1] geektimes.ru/post/254932/

[2] www.synopsys.com

[3] www.springer.com/us/book/9780387938196