PCで最大100 MHzの周波数でのビデオ伝送

はじめに

私たちの部門はCCDマトリックスと定規を開発しています。 開発されたセンサーごとに、テストできるようにする光検出器デバイス(FPU)を作成し、デバイスのパラメーター(ダイナミックレンジ、出力信号の不均一性、生成-再結合暗電流のレベルなど)を計算する必要があります。

FPUは一種のビデオカメラですが、手に持って公園に行って何か(例えばリス)を撮影できるものではありません。

通常、光検出器は複数のボードで構成されます。 一方のボードには電源安定装置、フィルターがあり、もう一方のボード(または他のボード)には全体のマイクロ回路スタッフィングがあります。 メインボードの中央にはセンサー自体があり、その周囲にはCCD電極に制御電圧を供給するための強力なクイックキーがあります。 エミッタフォロワがデバイスの出力に接続され、ビデオプロセッサ(CCD用のスマートADC)があり、すべてのFPGAが完成します。 キーを介してCCDにクロックパルスを供給し、ビデオプロセッサにクロックを供給し、そこからデジタルコードを取得し、必要な処理後に出力コネクタに送信します。 1つのコードに加えて、PCLK(ピクセル同期)、HSYNC(水平同期信号)、VSYNC(フレーム同期)の同期パルスが出力されます。これらは、受信側での情報の通常の受信に必要です。

もちろん、FPUは、デバイスの良好な計算パラメーターを得るために、CCDからのアナログ信号への干渉をできる限り少なくする必要があります。 しかし、この記事はFPUやCCDについてではなく、高周波でデジタルコードをPCに送信する方法と方法について説明しています。

送信機チップの簡単な説明

数年前、1000x1000の要素を含むマトリックス(開発のマトリックス)からデジタルビデオストリームを送信する必要が生じました。 これに先立って、私たちはラインナップ(ここでもデザインの)のみで作業し、USB 2.0をデータ転送に高速モードで使用しました。 支配者にとっては、スピードは十分で、問題はありませんでした。 しかし、水平線上で12ビットを送信するタスクが明らかになりました。 40 MHzの周波数でストリーミングします。 簡単な計算では、40MHz * 12bit = 480MBit / sであることが示されています。 -これはUSB2.0 HI-SPEEDの制限であり、理論上の制限でもあります。 私たちは最小の抵抗の道を歩み、光ファイバー伝送システムを求めた次の部門で、私たちはそれを開始し、それが機能しました。 しかし、特に光ファイバトランスミッタはPCIバス用に設計されていたため、ほとんど忘れられていたため、多くのFPU-PCに汎用性が必要でした。

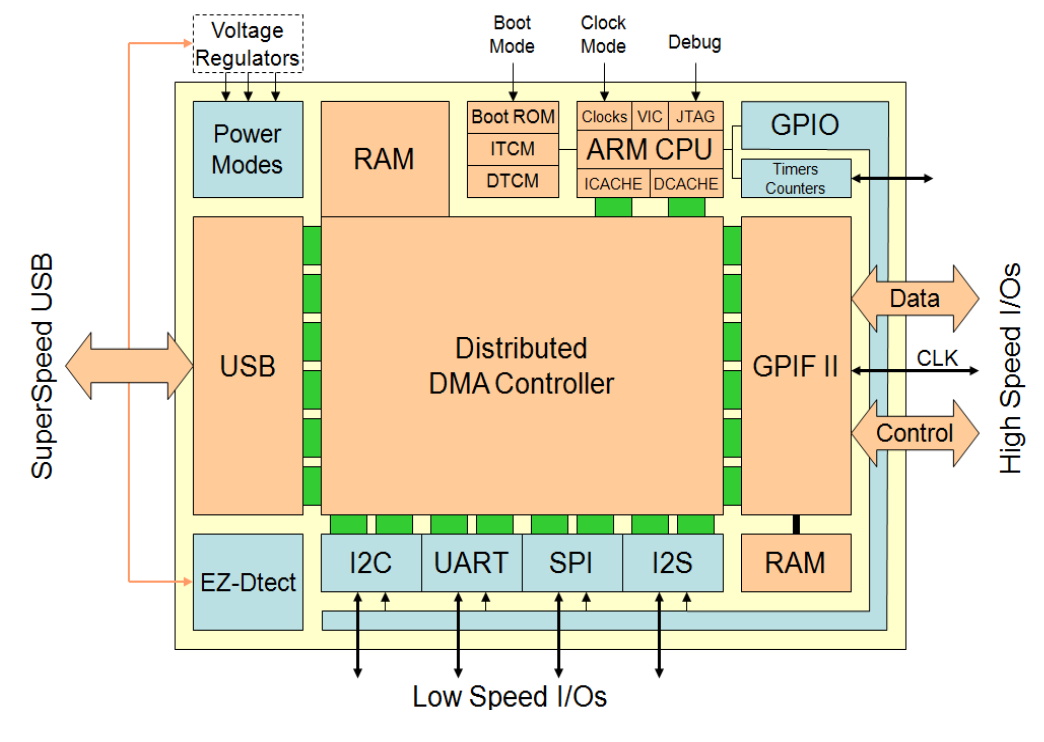

この伝送バンドルが機能している間、USB3.0バスに基づくソリューションを探していました。 検索は成功し、ソリューションはチップであることが判明しました-サイプレスのEZ-USB FX3 SuperSpeed USB 3.0周辺コントローラ。 コントローラーの機能図を図1に示します。

図1-コントローラーの機能図

このコントローラーには、構成可能なGPIF IIインターフェースがあります。 これを使用すると、FPGA、メモリ、必要なプロセッサなどをチップに接続できます...このインターフェイスのポイントは、好きなように設定できることです。 彼は自由に32ビットを使用できます。 データバス、8ビットアドレスバス、多数の同期ライン。 GPIF IIを最大限に使用する必要はありません。より小さなデータバスに制限し、アドレスバスを削除し、解放されたレッグを他の目的に使用できます。 インターフェイスの最大動作周波数は100 MHzです。 そのプログラミングは、GPIF II Designerという特別なソフトウェアで行われます。 メインファームウェアの作成は、Eclipseに基づいた「Cypress」の環境にあります。

コアは200 MHzのARM926EJです。 EZ-USB FX3にはフラッシュメモリがないため、プログラムは外部フラッシュ、EEPROMからSRAMにロードされるか、PCからUSB3.0を介してロードされます。 SRAMの容量とGPIF IIデータラインの数は、コントローラーのモデルによって異なります。 最大RAMサイズは512kB、最小は256kBです。 デバッグはJTAGを介して行われます。 コントローラには、GPIOに加えて、SPI、I2C、UART、I2Sの標準インターフェイスセットがあります。 チップにはDMAコントローラーもあります。 ケースは次のタイプで表されます-121レッグのBGAと131ピンのWLCSP。

EZ-USB FX3を使用したビデオ送信の原理

最初に、彼はFPUの束を例として引用することを計画していました-GPIF IIインターフェースおよびコントローラー自体のファームウェアを作成する分析を備えた1000x1000要素の国内マトリックス上のPCですが、これを行わなかったので、1つの記事で書きすぎる必要がありました。 さらに、サイプレスにはHDマトリックスの非常に良い例があり、ビデオデータを送信する際のm /回路の動作を理解できます。

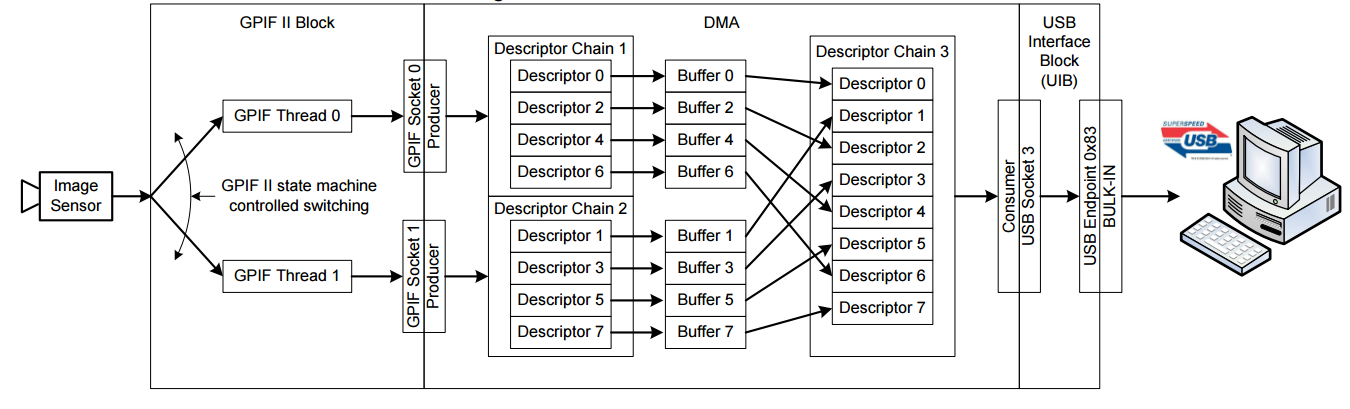

したがって、データ転送のカスケード全体:

図2-ビデオデータ送信のカスケード

1) GPIF IIインターフェース 。 デュアルスレッドモードで動作し、各ストリームはそのソケットに接続されます。 ソケットは、コントローラのさまざまな周辺機器、および周辺機器とプロセッサ間の接続ポイントです。 Producer Socket-データが書き込まれるソケット、Consumer Socket-データが読み取られるソケット。 デュアルストリームモード(ピンポン)を使用すると、バッファに遅延なくデータを書き込むことができます。 ゼロストリームの作業中にゼロバッファがいっぱいになると、自動的に別のストリームに切り替わり、記録は新しいバッファに移動し、古いバッファがPCに送信されます。 遅延がないため、少量のメモリに制限されたリアルタイムでビデオ信号を送信できます。

2) DMAブロック この例では、8つのバッファーを使用してデータを送受信します。 配列は、8、16、または32ビットです。 配列の深さは特定のタスクに依存します。 異なる数のバッファを使用できますが、主なことは、ビットサイズとボリュームが同じであり、その合計ボリュームが使用可能なメモリからクロールされないことです。 各バッファーの説明は、その記述子(記述子[7:0])に格納されます。 8つの記述子はすべて、2つのグループ(記述子チェーン1および2)に分割されます。 2つのグループはそれぞれ、記録ソケットに接続されています。

3記述子チェーンはUSBコントローラーを参照し、7-0バッファーからUSBソケット3を介してデータを正常に読み取るのに役立ちます。

お気づきかもしれませんが、図にはCPUブロックはありません。 その不在は偶然ではありません、なぜなら 送信されたデータを処理する必要がない場合、カーネルを省いて直接データを送信できます。

処理せずにデータを転送する場合、PCの形式の受信者は、識別マークのない情報付きのソーセージを受け取ります。 最初に受信した要素が同期開始点として取得され、この要素からのピクセル、ライン、フレームがカウントされます。 行のピクセル数とフレームの行数がわかっている場合、これを調整できます。 非同期同期が判明しましたが、これはあまり快適ではありません。 データには既に番号が付けられていることをお勧めします。

これがARM9カーネルの助けとなり、ソフトウェアの同期を実装できるようにします。 DMAアレイを初期化するとき、各バッファーの特別なヘッダー(16バイトなど)の下に場所を予約する必要があります。 これらの16バイトにビデオデータが書き込まれることはありません。 バッファーがいっぱいになると、DMAコントローラーはこれをプロセッサーに通知し、プロセッサーは(必要に応じて)必要なデータを取得してヘッダーに書き込みます。 ヘッダーに記入した後、プロセッサーはバッファーをPCに転送するコマンドを出します。

ビデオ送信時のコントローラーの原理の詳細については、このガイドを読むことをお勧めします-「Cypress」の「USBでEZ-USB FX3を使用してイメージセンサーインターフェイスを実装する方法」 GPIF IIのファームウェアを作成するプロセスを詳細に説明します。 マニュアルを分析した後、コントローラー自体のEclipseの付随プロジェクトをダウンロードして処理できます。

この記事は、実用的な観点から紹介的で有益ではないことが判明しました。 GPIF IIとMKのプログラミングプロセスを見て、コメントを書きたい場合は、すべてをペイントしようとします。 例として、12,000要素の国内線のファームウェアを分析します。