みなさんこんにちは!

アルテラSDK for OpenCLは、 OpenCLで記述されたコードをアルテラ FPGAファームウェアにコンパイルできるライブラリとアプリケーションのセットです。 これにより、プログラマーは、HDL言語の知識がなくてもFPGAを高性能コンピューティングのアクセラレーターとして使用し、GPUで使用するときに慣れていることを書くことができます。

簡単な例でこのツールを使用しましたが、それについてお話ししたいと思います。

計画:

猫へようこそ! 注意 、写真があります!

FPGA(FPGA)について一言

FPGA(Field-Programmable Gate Array)はユーザーがプログラム可能なゲートアレイで、 FPGAの一種です。

これらのチップは、論理要素の小さなブロックに基づいています。 このようなプリミティブでは、8ビットマイクロコントローラーからビットコインマイナーまで、あらゆるチップのロジックを構築できます。

FPGAの詳細を読む

FPGAの「クラシック」開発は次のようになります。

FPGAは、より高価な種類のマイクロコントローラーとして認識される場合があります。あちこちでLEDを点滅させ、UART、SPI、I2Cを整理できます。 以前は、FPGAが(リソースと周波数の点で)小さく、一部の深刻なデータ処理やプロセッサとの競合について話すことができなかったため、これは部分的に真実でした。 現在、FPGAチップはますます厚くなり、そのパフォーマンスはGPUと比較されています。

FPGAを使用すると、最低レベルで処理を制御できます。適切な場所に適切なサイズのキャッシュを作成し、パイプラインを整理し、明示的な同時実行性を記述します。 さまざまな周辺機器(ビデオカメラやイーサネットポートなど)を接続し、汎用プロセッサなしで計算を実行できます。

FPGAのすべての魅力は、低レベルの制御がある場合、この低レベルをプログラムする必要があるという事実によって相殺されます! 低レベルの抽象化は、常に開発とデバッグの複雑化、用語の増加につながります。

FPGA製造業者は、市場投入までの時間を短縮する必要性について非常に合理的に考えました。つまり、プログラマーがFPGAの下で非常に簡単かつ迅速に作成できるようにするためです。 並列計算用のプログラムを記述するための標準オプションの1つはOpenCLです。 アルテラはOpenCLのサポートを決定しました。 アルテラSDK for OpenCLが開発されました。

OpenCLの説明は意図的に省略しています。ロシア語のインターネットに関するこの主題に関する文献は多数あります。たとえば、 OpenCLの概要などです。

何を実行しますか?

FPGAを搭載したすべてのマザーボードが OpenCLを実行できるわけではありません。アルテラは特別なアフィリエイトプログラムを作成しました。開発者キットは上記のタグを取得します。

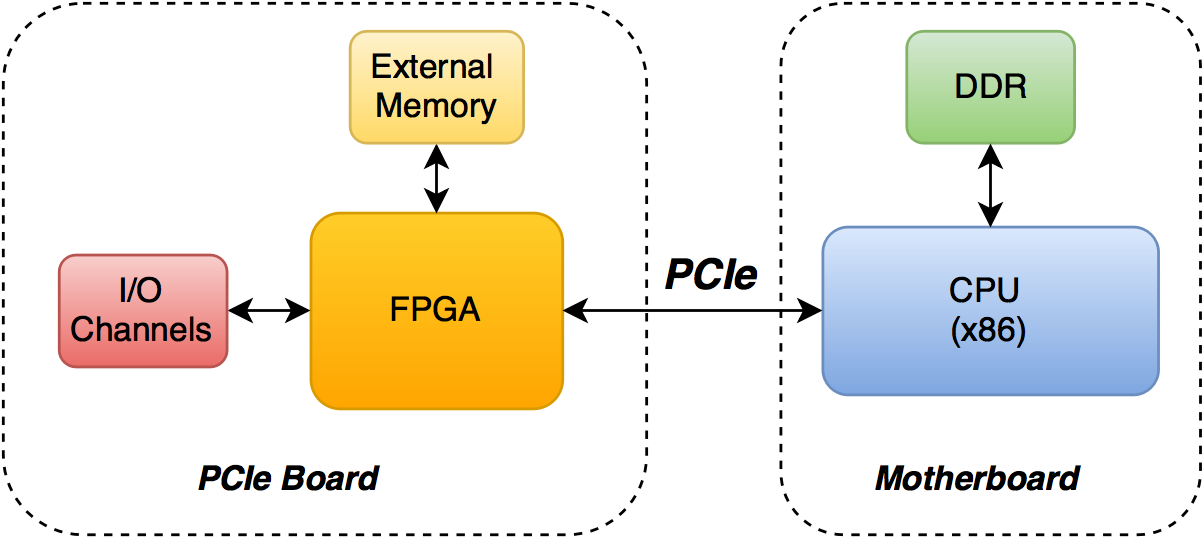

PCIe

FPGAチップは、対応するスロットのマザーボードに(少なくともGPUの代わりに)プラグインされるPCIeカードに配置できます。 DMAおよびPCIe FPGAを介して、プロセッサに接続されているDDRメモリと通信できます(計算のためにデータを取得します)。 ボードには、FPGAでのみ使用可能な外部メモリを配置することもできます(CPUのOSはこのメモリにアクセスできません)。

中間計算を保存するために外部メモリが必要になる場合があります。DMAへのアクセスはホストメモリへのアクセスよりも安価です。 DDRである必要はありません。一部の低遅延計算では、SRAMの方が適切に機能する場合があります。

処理用のデータは、グローバルメモリからだけでなく、たとえばイーサネットポートなどのI / Oチャネルからもカーネルに提供できます。 この場合、ホストはカーネルのみを構成し、データは最小限の遅延で処理されます。 (イーサネット、FPGA、低遅延という言葉が並んでいる場合、ほとんどの場合、高頻度取引が暗示されています)。

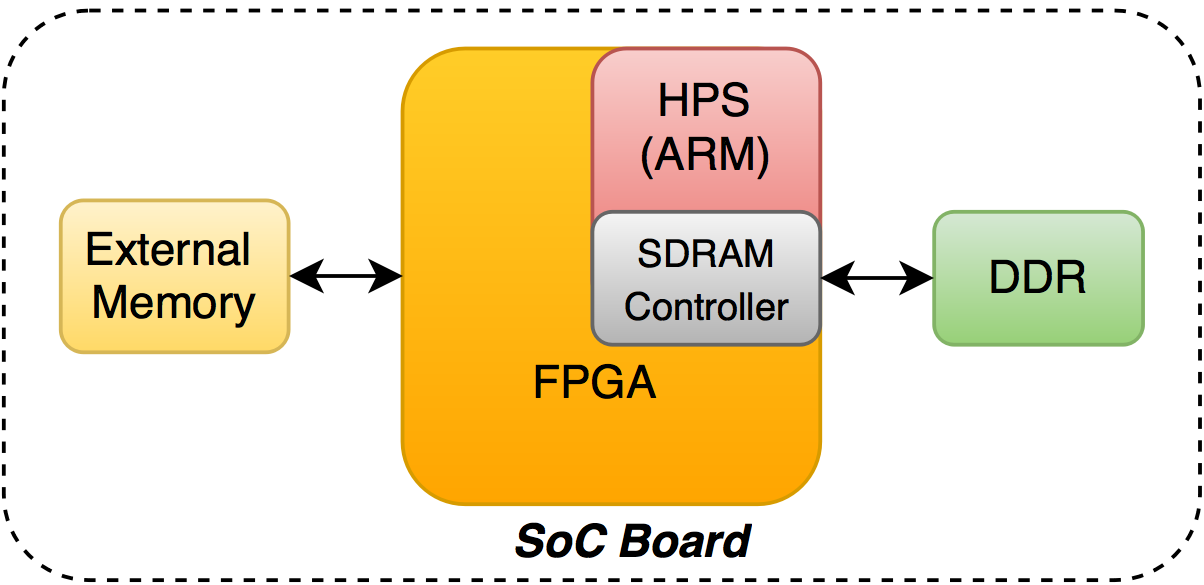

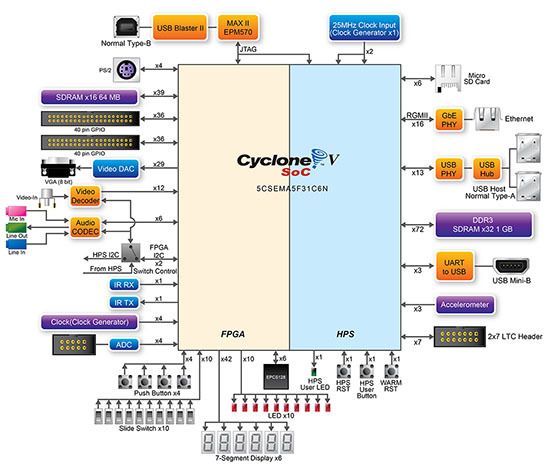

SoC

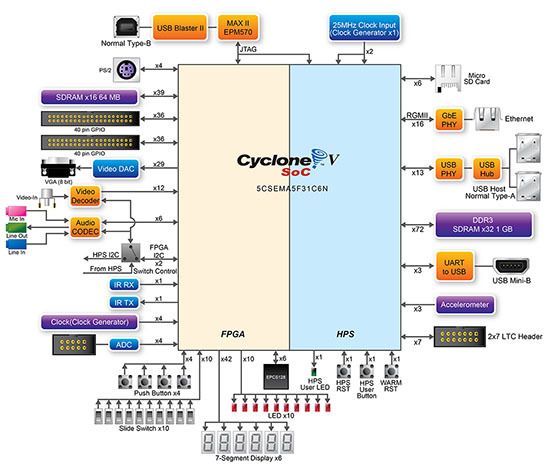

2番目のオプションは、 SoC 'axで可能です。プログラマブルロジックとARMプロセッサが1つのクリスタルに配置されています。

緑色のDDRメモリは共有リソースです。一方でCPUを使用し( そこでLinuxを実行できます )、もう一方でFPGAが最小限のオーバーヘッドでSDRAMコントローラを介してこのメモリに「直接」読み書きできます。 PCIeカードの場合と同様に、外部メモリをFPGAに接続できますが、その必要性は少なくなります。 常に手元のDDR。

プラットフォームの詳細については、 こちらをご覧ください 。

Altera Preferred Board for OpenCLマークのないボードでOpenCL を実行することは可能です。 これについては説明しませんが、出発点として、公式のアルテラSDK for OpenCL:カスタムプラットフォームツールキットユーザーガイドを参照することを提案します。

開発プロセス(ワークフロー)

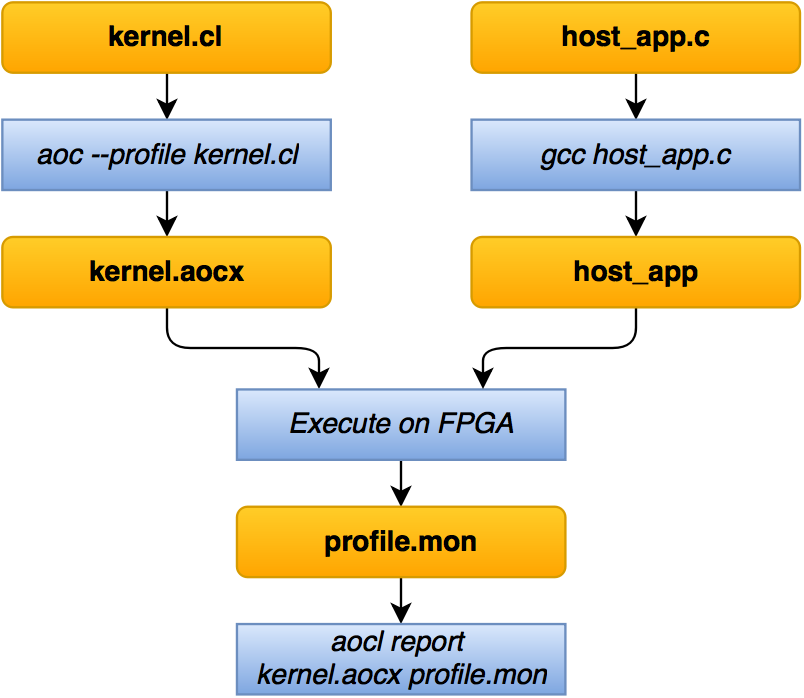

カーネルを起動するには、どのステップを実行する必要がありますか?

- カーネルコードは* .clファイルに記述されています。

- C / C ++のホストアプリケーションが準備されています。これにより、必要な量のメモリが割り当てられ、値がカーネルに「ロード」されます。

- アルテラOpenCL SDKに含まれているaocユーティリティを使用して、カーネルはaocxファイルに「コンパイル」されます。 gccを使用して、ホストアプリケーションが構築されます。

- host_appが起動すると、FPGA ファームウェアがロードされ、準備されたデータがカーネルにロードされ、処理が開始されます。

- プロファイリング用のカウンターは、 profile.monファイルに収まるデータを収集します。

- aoclユーティリティを使用すると、このレポートを見て、この実装がランタイム/パフォーマンスの点で満足できるかどうかを結論付けることができます。

- 満足したら、-- profileなしでカーネルを再コンパイルできます。 プロファイリングメーターは、FPGAのリソースを消費します。 一方、追加のコアを追加する予定がない場合は、再構築しないことが可能です。

- それが満たされない場合は、最適化する/ペンで書く/別のチップを取るか、それを我慢する必要があります。

aocxファイルへのコンパイルには数時間かかることがあります!

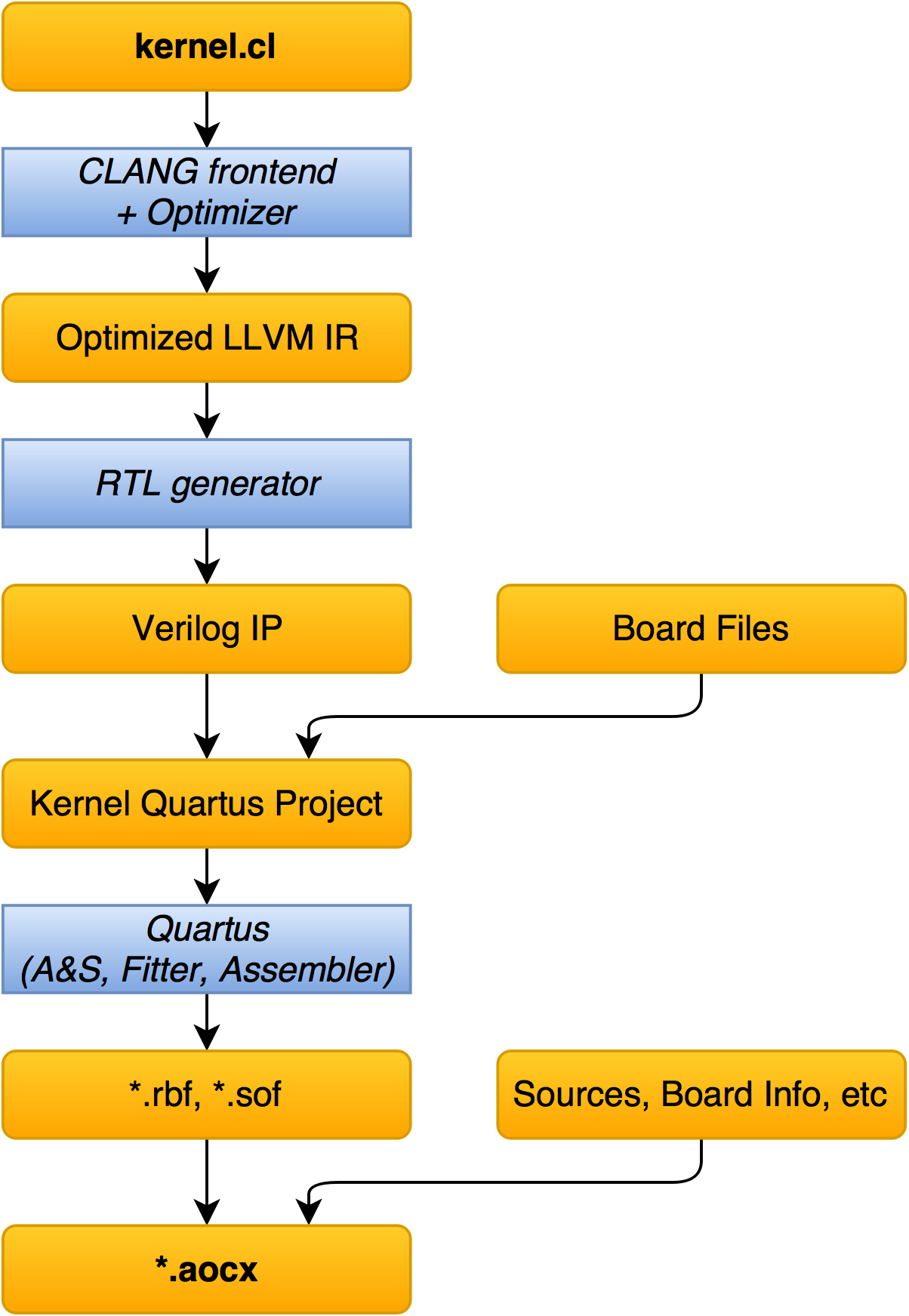

aoc kernel.clが呼び出されるとどうなりますか?

ビルドaocx

- kernel.clは 、記述をIRに変換し、さまざまな最適化も実行するclangによって提供されます。

- RTL Verilog IPコアが生成されます。 生成されたファイルは読み取り可能(暗号化されていない)であり、通常のシミュレーター(ModelSimなど)でシミュレートできます。 ただし、すべてのコードが自動生成されるわけではありません。人々が明確に書いたモジュールがあります。

- 受け取ったIPは、ボードのデフォルトプロジェクトに「参加」し、 Quartusの通常のプロジェクトが取得されます。

- プロジェクトは組み立てられています(Analysis&Synthesis、Fitter、Assembler)。 このアイテムの所要時間は最長(10分から数時間)です。プリミティブの最適な場所を検索するには、多くの計算が必要です。

- アセンブリの結果、ボードに関する情報などは、単なるELFファイルであるaocxに配置されます。

次に、このaocxファイルを使用してカーネルを「ロード」します。

DE1-SoC OpenCL BSP

言葉と写真では、すべてが非常に滑らかに見えます。Verilogの知識は必要ありません。

本当に何ですか?

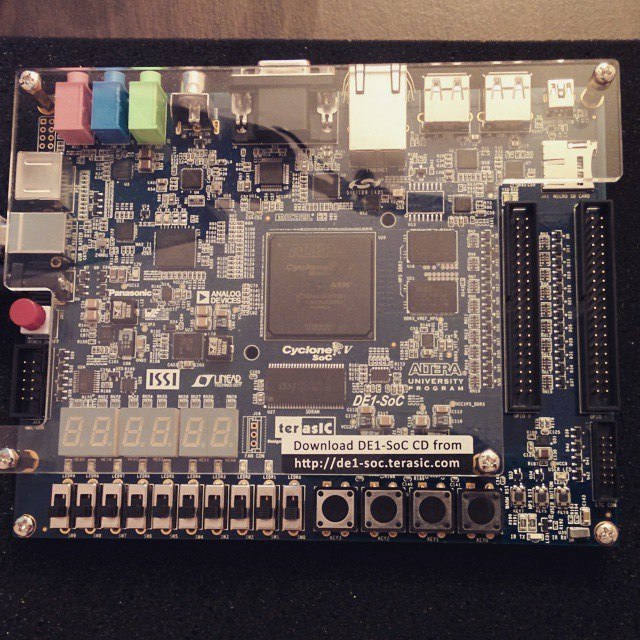

TerasicのDE1-SoCボードが私の手に再び現れました。 Cyclone V SoC ( 5CSEMA5F31C6 )の石に基づいています。

非表示のテキスト

このボードには、 OpenCLマーク用のAltera Preferred Boardがあります。そのため、OpenCLのローンチはすぐに使用できます。この特定のボードにはOpenCL BSPが必要です。 ここで取ることができます 。

OpenCL BSPのアーカイブには以下が含まれます。

- フラッシュドライブイメージ(Linuxが起動します)。

- インターフェイス(fpga2sdram、lwhps2fpgaなど)と同様に、すべてのピンが既に構成されているデフォルトのプロジェクト。

- 簡単な例。

イメージは、単にddを介してMicroSDに書き込まれます。

注 : クラス10フラッシュドライブを使用することをお勧めします 。

すでにLinuxがあります:

root@socfpga:~# uname -a Linux socfpga 3.13.0-00298-g3c7cbb9-dirty #3 SMP Fri Jul 4 15:42:32 CST 2014 armv7l GNU/Linux root@socfpga:~# cat /etc/issue Poky 8.0 (Yocto Project 1.3 Reference Distro) 1.3 \n \l root@socfpga:~# cat /proc/cpuinfo processor : 0 model name : ARMv7 Processor rev 0 (v7l) Features : swp half thumb fastmult vfp edsp thumbee neon vfpv3 tls vfpd32 CPU implementer : 0x41 CPU architecture: 7 CPU variant : 0x3 CPU part : 0xc09 CPU revision : 0 processor : 1 model name : ARMv7 Processor rev 0 (v7l) Features : swp half thumb fastmult vfp edsp thumbee neon vfpv3 tls vfpd32 CPU implementer : 0x41 CPU architecture: 7 CPU variant : 0x3 CPU part : 0xc09 CPU revision : 0 Hardware : Altera SOCFPGA Revision : 0000 Serial : 0000000000000000

また、コンパイルされたサンプルとOpenCLランタイム環境もあります。

思いやりのあるREADMEの提供:

Run "source ./init_opencl.sh" to setup OpenCL Run-Time Environment, including loading driver, on this board. Do it once right after booting the board. OpenCL Run-Time Environment is pre-installed in opencl_arm32_rte folder.

Init_opencl.sh自体は非常に簡単に見えます。

root@socfpga:~# cat init_opencl.sh export ALTERAOCLSDKROOT=/home/root/opencl_arm32_rte export AOCL_BOARD_PACKAGE_ROOT=$ALTERAOCLSDKROOT/board/c5soc export PATH=$ALTERAOCLSDKROOT/bin:$PATH export LD_LIBRARY_PATH=$ALTERAOCLSDKROOT/host/arm32/lib:$LD_LIBRARY_PATH insmod $AOCL_BOARD_PACKAGE_ROOT/driver/aclsoc_drv.ko

このスクリプトを実行し、 helloworldディレクトリに移動して、同じ名前のアプリケーションを実行します。

root@socfpga:~/helloworld# ./helloworld Querying platform for info: ========================== CL_PLATFORM_NAME = Altera SDK for OpenCL CL_PLATFORM_VENDOR = Altera Corporation CL_PLATFORM_VERSION = OpenCL 1.0 Altera SDK for OpenCL, Version 14.0 Querying device for info: ======================== CL_DEVICE_NAME = de1soc_sharedonly : Cyclone V SoC Development Kit CL_DEVICE_VENDOR = Altera Corporation CL_DEVICE_VENDOR_ID = 4466 CL_DEVICE_VERSION = OpenCL 1.0 Altera SDK for OpenCL, Version 14.0 CL_DRIVER_VERSION = 14.0 CL_DEVICE_ADDRESS_BITS = 64 CL_DEVICE_AVAILABLE = true CL_DEVICE_ENDIAN_LITTLE = true CL_DEVICE_GLOBAL_MEM_CACHE_SIZE = 32768 CL_DEVICE_GLOBAL_MEM_CACHELINE_SIZE = 0 CL_DEVICE_GLOBAL_MEM_SIZE = 536870912 CL_DEVICE_IMAGE_SUPPORT = false CL_DEVICE_LOCAL_MEM_SIZE = 16384 CL_DEVICE_MAX_CLOCK_FREQUENCY = 1000 CL_DEVICE_MAX_COMPUTE_UNITS = 1 CL_DEVICE_MAX_CONSTANT_ARGS = 8 CL_DEVICE_MAX_CONSTANT_BUFFER_SIZE = 134217728 CL_DEVICE_MAX_WORK_ITEM_DIMENSIONS = 3 CL_DEVICE_MAX_WORK_ITEM_DIMENSIONS = 8192 CL_DEVICE_MIN_DATA_TYPE_ALIGN_SIZE = 1024 CL_DEVICE_PREFERRED_VECTOR_WIDTH_CHAR = 4 CL_DEVICE_PREFERRED_VECTOR_WIDTH_SHORT = 2 CL_DEVICE_PREFERRED_VECTOR_WIDTH_INT = 1 CL_DEVICE_PREFERRED_VECTOR_WIDTH_LONG = 1 CL_DEVICE_PREFERRED_VECTOR_WIDTH_FLOAT = 1 CL_DEVICE_PREFERRED_VECTOR_WIDTH_DOUBLE = 0 Command queue out of order? = false Command queue profiling enabled? = true Using AOCX: hello_world.aocx Kernel initialization is complete. Launching the kernel... Thread #2: Hello from Altera's OpenCL Compiler! Kernel execution is complete.

さて、フラッシュドライブ上の特別に準備されたいくつかの例とファイルが機能し、何かを印刷します。

簡単な例をビルドして実行するには、何をする必要がありますか?

SDKのインストール

必要なもの:

- Quartus

- アルテラSDK for OpenCL

- SoC Embedded Design Suite :SoC'e上でアプリケーションを構築およびデバッグするためのツールセット。

これらのツールをすべてインストールするのは簡単なことですが、微妙な点があります。

- ルート権限が必要になる場合がありますが、インストールの最後でのみ通知されます。

- インストール後、PATH、ALTERAOCLSDKROOT、QUARTUS_ROOTDIRに何かを書き込む必要があります。 そこに登録するものは、関連するガイドから学ぶことができます。

何か間違ったことをしたかもしれませんが、最終的には環境変数を設定するためのスクリプトが次のようになり始めました。

export PATH=/home/ish/altera/14.1/quartus/bin:$PATH export PATH=/home/ish/altera/14.1/hld/bin:$PATH export PATH=/usr/local/DS-5/bin:$PATH export PATH=/usr/local/DS-5/sw/gcc/bin:$PATH export PATH=/home/ish/altera/14.1/hld/linux64/bin/:$PATH export ALTERAOCLSDKROOT=/home/ish/altera/14.1/hld/ export QUARTUS_ROOTDIR=/home/ish/altera/14.1/quartus/ export LD_LIBRARY_PATH=/home/ish/altera/14.1/hld/linux64/lib/:$LD_LIBRARY_PATH # , export AOCL_BOARD_PACKAGE_ROOT=/home/ish/altera/14.1/hld/board/de1soc

非表示のテキスト

はい、私は最新のQuartusを持っていないため、おそらく15番目のバージョンで少し低めに表示されるものが改善されました。

OpenCLの点で根本的に変更されたものがある場合、PMで私に当たっていただければ幸いです。

OpenCLの点で根本的に変更されたものがある場合、PMで私に当たっていただければ幸いです。

これをすべて設定し、ライセンスに専念したら、ボードをインストールする必要があります。

これを行う方法は、BSPのアーカイブにあるREADME.txtに指示します。

note:before the below operations,make sure you have install the opencl SDK 14.0 and SoCEDS 14.0. 1. directly unzip the de1soc_openCL_bsp.zip into %ALTERAOCLSDKROOT%/board directory. 2. set the "User variables" AOCL_BOARD_PACKAGE_ROOT to %ALTERAOCLSDKROOT%/board/de1soc 3. open the windows command window and type "aoc --list-boards", it should output "de1soc_sharedonly"

実行して確認します。

ish@xmr:~$ aoc --list-boards Board list: de1soc_sharedonly

ボードがリストに表示されました-それはすべてが正しく行われたことを意味します。

例を置く

まず、非常に単純な例を選択しました。

Z = X + Y 、

XとYは、 N個の uint(32ビット)数値の配列です。

カーネルvector_addは非常にシンプルに見えます:

// ACL kernel for adding two input vectors __kernel void vector_add( __global const uint *restrict x, __global const uint *restrict y, __global uint *restrict z ) { // get index of the work item int index = get_global_id(0); // add the vector elements z[index] = x[index] + y[index]; }

完全なホストコードは提供しません。 こちらをご覧ください 。

彼は何をしますか:

- OpenCLデバイスとは何かを認識しようとする

- aocxファイルを使用してFPGAを再プログラムする

- 配列X、Y、Zのバッファーを初期化します

- 配列XおよびYにデータを生成し、(プロセッサ上で)参照応答も計算します

- 配列へのポインタをカーネルに渡します

- 処理を開始します

- その完成を待っています

- 参照の回答をカーネルがカウントしたものと比較します

ビルドは簡単です。ARMクロスコンパイラを使用する非常にシンプルなMakefileを実行します。 (この場合のホストは、SoC'eにあるARMです)。

aocxを取得 :

ish@xmr:~/tmp/cl/vector_add$ aoc device/vector_add.cl -o bin/vector_add.aocx --board de1soc_sharedonly --profile -v aoc: Environment checks are completed successfully. You are now compiling the full flow!! aoc: Selected target board de1soc_sharedonly aoc: Running OpenCL parser.... aoc: OpenCL parser completed successfully. aoc: Compiling.... aoc: Linking with IP library ... aoc: First stage compilation completed successfully. aoc: Hardware generation completed successfully.

--profileフラグは、プロファイルを作成するためのカウンターをファームウェアに追加し、 -vは冗長なものであることを思い出させてください。

約10〜15分かかります。

binディレクトリにvector_add.aocxが表示され、 bin_vector_addに Quartusプロジェクトが表示されました。このプロジェクトはこの間ずっと組み立てられていました。

アセンブリレポート:

+-------------------------------------------------------------------------------+ ; Fitter Summary ; +---------------------------------+---------------------------------------------+ ; Fitter Status ; Successful - Sat Oct 17 21:36:01 2015 ; ; Quartus II 64-Bit Version ; 14.1.0 Build 186 12/03/2014 SJ Full Version ; ; Revision Name ; top ; ; Top-level Entity Name ; top ; ; Family ; Cyclone V ; ; Device ; 5CSEMA5F31C6 ; ; Timing Models ; Final ; ; Logic utilization (in ALMs) ; 5,570 / 32,070 ( 17 % ) ; ; Total registers ; 9685 ; ; Total pins ; 103 / 457 ( 23 % ) ; ; Total virtual pins ; 0 ; ; Total block memory bits ; 127,344 / 4,065,280 ( 3 % ) ; ; Total DSP Blocks ; 0 / 87 ( 0 % ) ; ; Total HSSI RX PCSs ; 0 ; ; Total HSSI PMA RX Deserializers ; 0 ; ; Total HSSI TX PCSs ; 0 ; ; Total HSSI PMA TX Serializers ; 0 ; ; Total PLLs ; 2 / 6 ( 33 % ) ; ; Total DLLs ; 1 / 4 ( 25 % ) ; +---------------------------------+---------------------------------------------+

私が最も興味を持っているのは、 ロジック使用率と合計ブロックメモリビットの 2行です。

この簡単な例では、5570 ALMを使用しました。 実際、加算操作にかかるのはこの数の1%未満です。残りは、「インフラストラクチャ」によって占められ、DDR(およびプロファイリングカウンタ)からデータを読み書きします。 Quartusのプロジェクトはデフォルト設定で行われていたことに注意することも重要です。デフォルト設定には、リソース/頻度の最適化は含まれていません。

また、合計容量が約128 Kビットのメモリが自動的に「どこか」に表示されたことも興味深いです。

ところで、 vector_add.aocxに表示されたセクションを見ることができます:

非表示のテキスト

ish@xmr:~/tmp/cl/vector_add$ readelf -a bin/vector_add.aocx ELF Header: Magic: 7f 45 4c 46 01 01 01 00 00 00 00 00 00 00 00 00 Class: ELF32 Data: 2's complement, little endian Version: 1 (current) OS/ABI: UNIX - System V ABI Version: 0 Type: NONE (None) Machine: Advanced Micro Devices X86-64 Version: 0x1 Entry point address: 0x0 Start of program headers: 0 (bytes into file) Start of section headers: 2370388 (bytes into file) Flags: 0x0 Size of this header: 52 (bytes) Size of program headers: 0 (bytes) Number of program headers: 0 Size of section headers: 40 (bytes) Number of section headers: 20 Section header string table index: 1 Section Headers: [Nr] Name Type Addr Off Size ES Flg Lk Inf Al [ 0] NULL 00000000 000000 000000 00 0 0 0 [ 1] .shstrtab STRTAB 00000000 000080 00011c 00 S 0 0 128 [ 2] PROGBITS 00000000 000200 001000 00 0 0 128 [ 3] .acl.board PROGBITS 00000000 001200 000011 00 0 0 128 [ 4] .acl.compileoptio PROGBITS 00000000 001280 000002 00 0 0 128 [ 5] .acl.version PROGBITS 00000000 001300 00000a 00 0 0 128 [ 6] .acl.file.0 PROGBITS 00000000 001380 000030 00 0 0 128 [ 7] .acl.source.0 PROGBITS 00000000 001400 0006c2 00 0 0 128 [ 8] .acl.nfiles PROGBITS 00000000 001b00 000001 00 0 0 128 [ 9] .acl.source PROGBITS 00000000 001b80 0006c2 00 0 0 128 [10] .acl.opt.rpt.xml PROGBITS 00000000 002280 000019 00 0 0 128 [11] .acl.mav.json PROGBITS 00000000 002300 00107f 00 0 0 128 [12] .acl.area.json PROGBITS 00000000 003380 0009da 00 0 0 128 [13] .acl.profiler.xml PROGBITS 00000000 003d80 002f08 00 0 0 128 [14] .acl.profile_base PROGBITS 00000000 006d00 0009c8 00 0 0 128 [15] .acl.autodiscover PROGBITS 00000000 007700 000071 00 0 0 128 [16] .acl.autodiscover PROGBITS 00000000 007780 00021e 00 0 0 128 [17] .acl.board_spec.x PROGBITS 00000000 007a00 0003eb 00 0 0 128 [18] .acl.fpga.bin PROGBITS 00000000 007e00 23ab98 00 0 0 128 [19] .acl.quartus_repo PROGBITS 00000000 242a00 000151 00 0 0 128 Key to Flags: W (write), A (alloc), X (execute), M (merge), S (strings), l (large) I (info), L (link order), G (group), T (TLS), E (exclude), x (unknown) O (extra OS processing required) o (OS specific), p (processor specific) There are no section groups in this file. There are no program headers in this file. There are no relocations in this file. There are no unwind sections in this file. No version information found in this file.

カーネルを起動します

scp vector_addおよびvector_add.aoxを介してボードにコピーし、実行します。

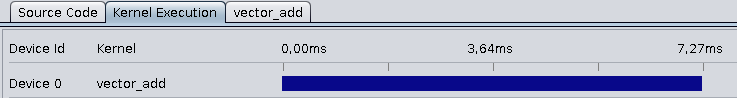

root@socfpga:~/myvectoradduint# ls -l -rwxr-xr-x 1 root root 42525 Apr 16 06:57 vector_add -rw-r--r-- 1 root root 2371188 Apr 16 06:58 vector_add.aocx root@socfpga:~/myvectoradduint# ./vector_add Initializing OpenCL Platform: Altera SDK for OpenCL Using 1 device(s) de1soc_sharedonly : Cyclone V SoC Development Kit Using AOCX: vector_add.aocx Launching for device 0 (1000000 elements) Time: 112.475 ms Kernel time (device 0): 7.270 ms Verification: PASS

7.270ミリ秒で100万ペアの32ビット数、または7.27 nsで1ペアを追加できました。 実際、このインジケーターは現時点ではそれほど興味深いものではありません。例はパフォーマンス用に最適化されていません。 (スポイラー:1つの加算器のみが使用されました:計算の並列化はありませんでした)。

実行後、 profile.monはディレクトリに表示されます。

root@socfpga:~/myvectoradduint# ls -l -rw-r--r-- 1 root root 170 Apr 16 06:58 profile.mon -rwxr-xr-x 1 root root 42525 Apr 16 06:57 vector_add -rw-r--r-- 1 root root 2371188 Apr 16 06:58 vector_add.aocx

それをコンピューターにコピーして、プロファイリング結果を確認します。

ish@xmr:~/tmp/cl/vector_add$ aocl report bin/vector_add.aocx profile.mon

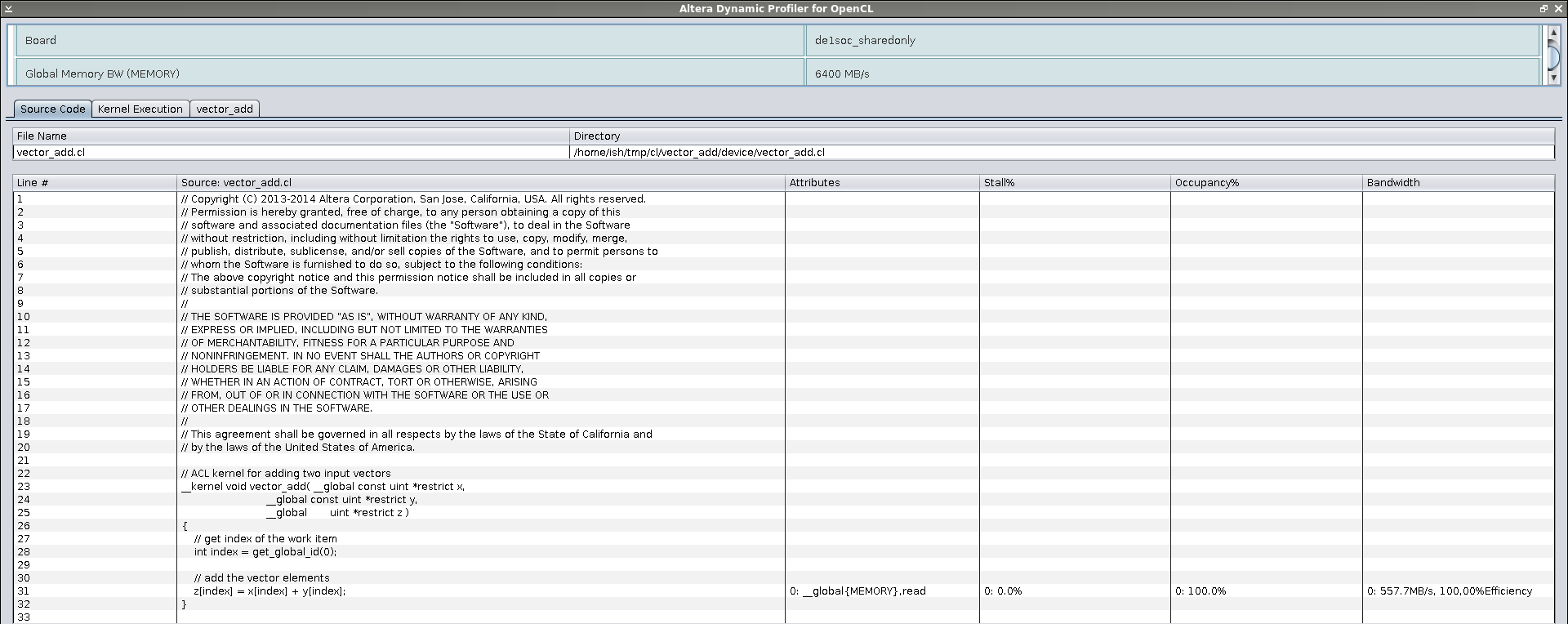

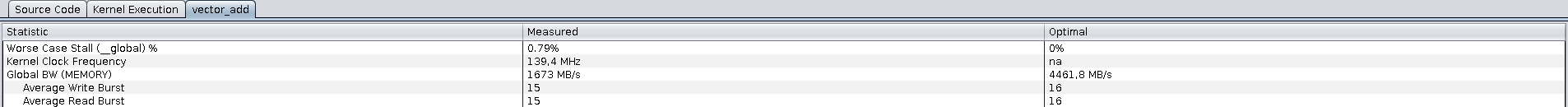

プロファイラーは、グローバルメモリに帯域幅の3分の1しか使用していないことを示しました。

ビジュアライザーを実行することが可能です:

ish@xmr:~/tmp/cl/vector_add$ aocl vis bin/vector_add.aocx

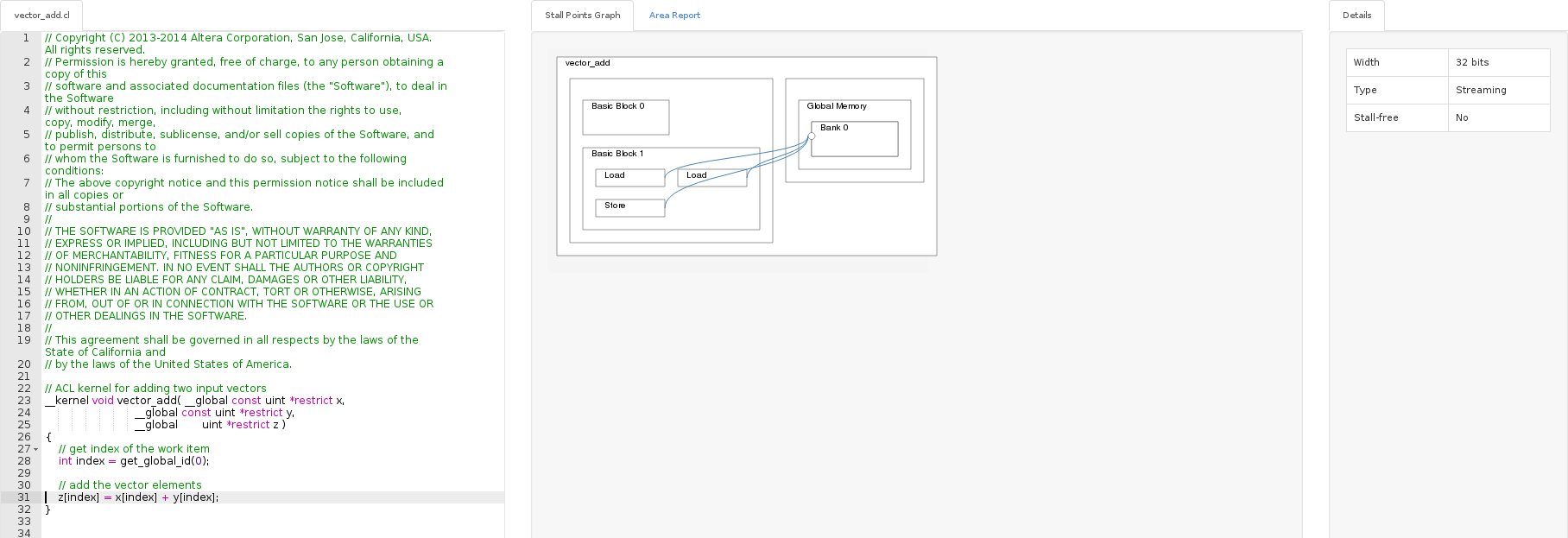

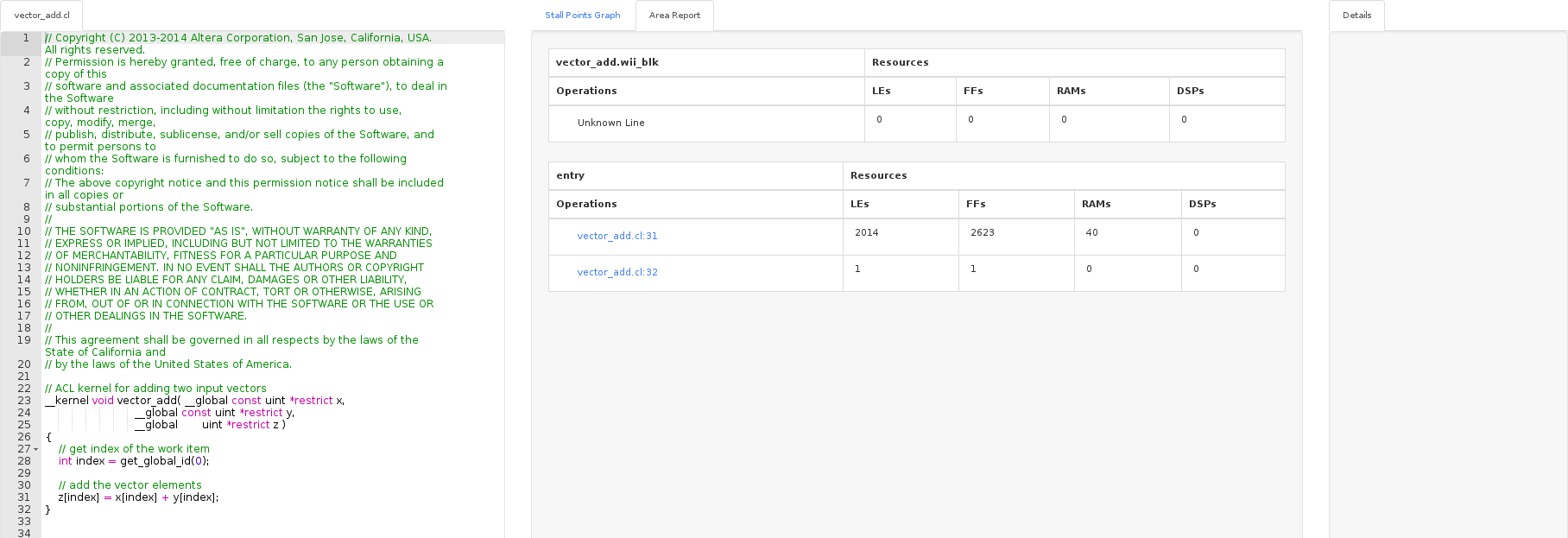

ビジュアライザーは、グローバルメモリと通信する3つのブロックがあることを示しました。2つは読み取り用、1つは書き込み用です。 この場合のグローバルメモリへのアクセスは、幅の狭いリンクになることがあります。 各行のエリアレポートでは、FPGAで実装に費やされたリソースの量を確認できます。 もちろん、1行の例は指標ではありません。

アルテラのyoutubeチャンネルには、上記のすべての手順を詳細に示すビデオがあります。

このサイクルの残りのビデオは、ネタバレの下にあります:

非表示のテキスト

おわりに

この記事では、HDL言語の知識がなくても、FPGAで高レベルで記述できるツールを試しました。 ご覧のとおり、(簡単な例を使用して)動作し、実際に余分なことをする必要はありませんでした。

FPGAでのOpenCLは金色のハンマーにはなりません。

- ビートに正確なプロセスを記述することはできません(しかし、これから逃げたいと思いました!)

- 小さなチップには適用できません。インフラストラクチャは膨大な量のリソースを消費します。

ただし、FPGAはそれを使用して、ビデオ処理(マシンビジョン)、暗号化、DSP、さまざまなプロセスのシミュレーション(シミュレーション)などの分野でGPUと競合できます。 私が作業している領域(生成、フィルタリング、イーサネットパケットのスイッチング)、最低レベルのコントロールのおかげで最大のパフォーマンスが絞り出される領域について話すと、OpenCLの使用方法がわかりません(同様の結果が得られます)。

最大のパフォーマンスが必要な場合は、この言語構成またはその言語構成が得られるものを非常によく理解する必要があります。 そのため、FPGAの下でOpenCLでそれほど深刻ではないものを作成したい人は、基本レベルでQuartus、Qsys、およびVerilog(読み取りレベルで)を勉強する必要があるように思えます。 おそらく、ビジュアライザーとプロファイラーで十分ですが、学生の偽物のように見える限り、新しいquartusリリースで修正されることを願っています。

リアルタイムのビデオ処理について話す場合は、このデモを見ることをお勧めします。

iABRAのメンバーは、最初にAMD GPUを使用したOpenCLでマシンビジョンを実行しましたが、その後アルテラに移行しました。 プログラマーは、OpenCLを使用すると「VHDLを理解できなくなるため、 彼らはこれに経験がなく、何ができるかを書いています。」

GPUとOpenCL FPGAでのアルゴリズム(暗号化、ビデオ処理)の実装を比較するレポートでは、1秒あたりに実行される操作の数はほぼ同じですが、FPGAは10分の1の電力しか消費しません。 私は自分で試したことがないので、そのようなベンチマークについては常に少し懐疑的です)

新しいArria 10ファミリとStratix 10ファミリのリリースにより、ますます多くの並列コンピューティングがFPGAに切り替わると考えています。これらのチップは、スーパーコンピューターとデータセンターで見られるでしょう。

また、アルテラSDK for OpenCLの実際の使用に関する別のビデオ:

ご清聴ありがとうございました! コメントまたはPMで質問やコメントを歓迎します)

便利なリンク :

- サンプルソースと自動生成されたVerilogコード

- アルテラSDK for OpenCL:概要

- アルテラSDK for OpenCL:入門ガイド

- アルテラのOpenCL Compilerを使用したFPGAのパワーの活用 :写真を見るのが好きな人のための非常に大きなプレゼンテーション(100枚以上のスライド):)

- アルテラSDK for OpenCL:プログラミングガイド

- アルテラSDK for OpenCL:最適化ガイド

- アルテラSDK for OpenCL:ベストプラクティスガイド

更新 :

記事の第2部がリリースされました: アルテラ+ OpenCL:カーネルを開きます 。