理論のビット

デジタルオートマトン(CA)は、いくつかのアルゴリズムに従って離散情報を受信、保存、および変換するデバイスであり、いくつかの安定状態のいずれかになります[7]。

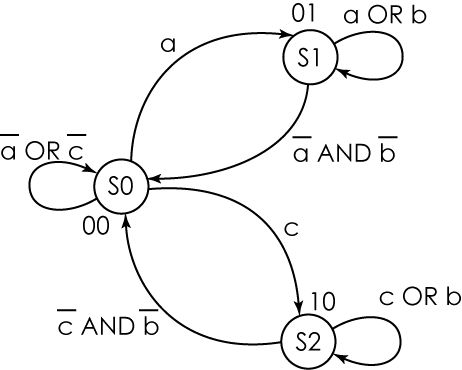

図1-デジタルマシンのグラフ

デジタルオートマトンの出力信号が現在の状態のみに依存する場合、そのようなオートマトンはムーアオートマトンと呼ばれますが、出力信号が現在の状態と入力信号に依存する場合、そのようなデジタルオートマトンはMilyオートマトンと呼ばれます。

デジタルマシンは、次の表現を使用して説明できます。

-有向グラフの形式で、

-遷移と出口を使用します。

有向グラフの形式でのデジタルオートマトンの表現を図に示します。 1.ここでは円—グラフの頂点—デジタルオートマトンの状態が示され、状態間の遷移は頂点間のアークで示され、同じ状態への遷移はループで示されます。

アークとループの近くに、この遷移が発生する入力信号の値が表示されます。 たとえば、(a OR b)は、 a = 1またはb = 1のときにこの遷移が発生することを意味します。

ムーアオートマトンの出力信号はグラフの頂点の近くに表示され、デジタルマイリーオートマトンの場合は、入力信号の近くの円弧に表示されます。 T.O. 図 図1は、デジタルムーア機を示しています。

テーブルを使用したデジタルオートマトンの表現は、遷移テーブルと終了テーブルの2つのテーブルが存在することを意味します。 遷移表は、デジタルマシンの現在の状態、入力信号、および将来の状態をリンクします。 図のグラフで記述されたCAの遷移表 1を表に示します。 1。

表1-デジタルマシンの遷移表

| 現在の状態 | 次の状態 | 遷移条件 |

| S0 | S0 | a = 0またはc = 0 |

| S0 | S1 | a = 1 |

| S1 | S1 | a = 1またはb = 1 |

| S1 | S0 | a = 0およびb = 0 |

| S0 | S2 | c = 1 |

| S2 | S2 | c = 1またはb = 1 |

| S2 | S0 | c = 0およびb = 0 |

出力テーブル -デジタルマシンの現在の状態とその出力信号の対応を示します(表2)。

表2-デジタルマシンの出力の表}

| 現在の状態 | 出口 |

| S0 | 00 |

| S1 | 01 |

| S2 | 10 |

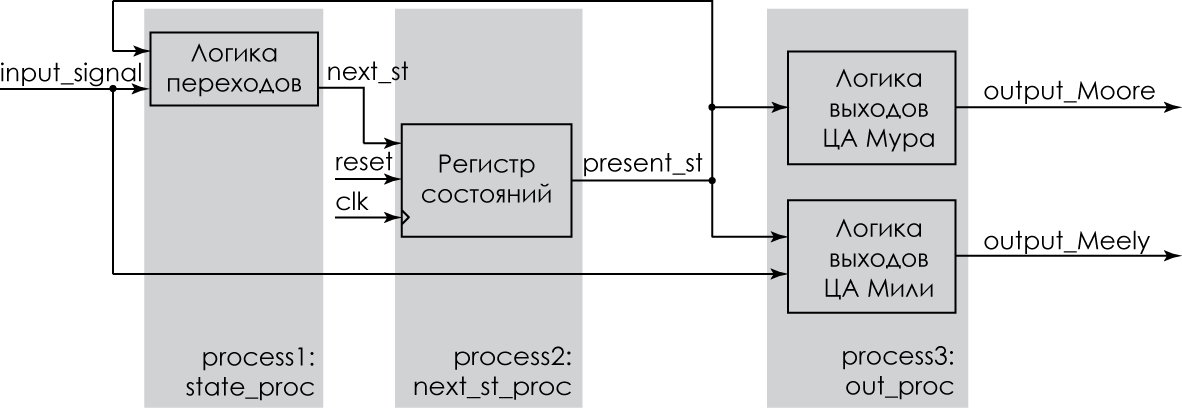

デジタルマシンを実装する場合、回路の組み合わせ部分と順次部分への分離の原則を順守します。 この解釈により、デジタルマシンは3つのブロックで表されます(図2)。

-組み合わせブロックの論理遷移。

-CAの状態を保存するためのレジスタ。

-出力信号を生成するための組み合わせブロック-TsAマイルとムーアでは異なります。

図2-非同期出力を備えたデジタルマシンの概略図

入力への遷移のロジックは 、デジタルマシンの現在の状態のコード( present_st )と外部信号( input_signal )を受け取ります。 このブロックの出力は、次の状態コード( next_st )です。

状態レジスタには、クロック( clk )、リセット( reset )、および次の状態コード( next_st )の3つの信号が含まれます。 クロック信号とリセット信号は、デジタルマシンの状態を保存するトリガーを制御するように設計されています。 クロック信号の立ち上がりエッジで、次の状態( next_st )がトリガーに記録されます。 トリガーへの書き込みの結果は、ステータスレジスタの出力にCAの現在の状態の信号( present_st )として表示されます。

CAの状態(およびMilesマシンの入力信号)に応じて、 出力信号を生成するブロックは、非同期出力信号を生成します。 同期出力信号を取得するために、このユニットにレジスタが追加で組み込まれています。

VHDLを使用してデジタルマシンを記述する

デジタルマシンの状態を記述するには、列挙型を使用する必要があります。 このために、タイプ( state_type )が記述され、その値はデジタルマシンの状態です。 次に、この列挙型の信号( 状態 )が記述され、オートマトンの現在の状態が格納されます。

TYPE state_type IS (init, state1, state2, ...); SIGNAL state: state_type;

実装時に、いくつかのトリガーのスキームが取得されます。 状態のエンコード方法に応じて、トリガーの数が異なり、回路の速度とサイズに影響します。 コーディング方法についてはもう少し後で説明します。

デジタルオートマトンの動作を説明し、遷移と出力のロジックの組み合わせ回路を作成するには、対応するテーブルを使用し、 case演算子を使用してpresent_st信号の値を分析する必要があります。

デジタルオートマトンの遷移ロジックを計算するための組み合わせ部分を説明するプロセスは、このテンプレートを使用して説明できます。

PROCESS (present_st, input_signal) BEGIN CASE present_st IS WHEN state1 => IF input_signal = '1' THEN next_st <= state1; ELSE next_st <= state2; END IF; WHEN state2 => IF input_signal = '1' THEN next_st <= state2; ELSE next_st <= state3; END IF; ... END CASE; END PROCESS;

出力信号のロジックを記述するために、プロセス演算子または並列条件付き代入演算子を使用することができます。

デジタルムーアオートマトンの出力を計算するための組み合わせ部分を説明するプロセスは、このテンプレートを使用して説明できます。

PROCESS (present_st) BEGIN CASE present_st IS WHEN state1 => output <= "000"; WHEN state2 => output <= "001"; ... END CASE; END PROCESS;

ここで、プロセス初期化リストでは、 present_stデジタルマシンの現在の状態のみが使用され 、その値はケース演算子を使用して分析されます。

Milesマシンの場合、同じプロセスは次のようになります。

PROCESS (present_st, input_signal) BEGIN CASE present_st IS WHEN state1 => IF input_signal = '1' THEN output <= "000"; ELSE output <= "001"; END IF; WHEN state2 => IF input_signal = '1' THEN output <= "011"; ELSE OUTPUT <= "010"; END IF; ... END CASE; END PROCESS;

このプロセスは、現在のCA状態( present_st )と入力信号( input_signal )を使用して初期化します。これらの信号のいずれかを変更するとプロセスがトリガーされるためです。

同期出力信号を取得するには、初期化リストにクロック信号clkのみを含むプロセスを使用する必要があります。 前のケースと同様に、現在の状態の分析は、 caseステートメントを使用して実行されます。

PROCESS (clk) BEGIN IF (rising_edge(clk)) THEN CASE present_st IS WHEN state1 => output <= "000"; WHEN state2 => output <= "001"; ... END CASE; END IF; END PROCESS;

並列条件付き割り当てを使用して出力信号を生成するには、プロセス演算子は必要ありません。 この場合、次の構成を使用できます。

output <= "000" WHEN present_st = state1 ELSE "001" WHEN present_st = state2 ELSE ... "100";

デジタルオートマトンのシリアル部分を記述する場合、 clkおよびリセット信号はプロセス初期化子のリストに含まれている必要があります。 リセット信号が到着すると、デジタルマシンは初期状態initになり 、そこからマシン全体が起動します。 clk信号のリーディングエッジがCAに書き込むと、新しい現在の状態がトリガーされます。 next_st信号はpresent_st信号に書き換えられます。

実際、シリアル部分はリセットレジスタです。

PROCESS (clk, reset) BEGIN IF reset = '1' THEN present_st <= Init; ELSIF (rising_edge(clk)) THEN present_st <= next_st; END IF; END PROCESS;

リセット信号は同期または非同期の場合があります。 上記のリストは、非同期リセットオプションについて説明しています。

非同期リセット信号を使用する場合、電源がオンになったときにデジタルマシンがどのような状態になるかが常にわかります。 クロック信号が到着し、システムが正常に機能する前に。 この場合、デジタルマシンの未使用の状態をデコードする必要がないため、遷移のロジックが削減されます。

同期リセット信号を使用すると、マシンの電源投入時の状態を判別できません。 彼は説明されていない状態のいずれかに「固執」する可能性があります。 T.O. デジタルオートマトンを記述する場合、デジタルオートマトンの動作状態であるかどうかに関係なく、トリガー状態の2 ^ nのすべての組み合わせを記述する必要があります。 ここで、nはデジタルマシンのエンコードに使用されるトリガーの数です。 これにより、移行ロジックスキームが増加します。

説明されていない状態でターゲットオーディエンスが「固着」するのを避けるために、 when ... other構造を使用して、そのような状況でアクションを明示的に登録する必要があります。 たとえば、このようなプロセスを使用して、同期リセットと未使用状態のアクションを記述することができます。

PROCESS (clk) BEGIN IF (rising_edge(clk)) THEN IF reset = '1' THEN state <= init; ELSE CASE state IS WHEN state1 => IF input_signal = '1' THEN state <= state1; ELSE state <= state2; END IF; WHEN state2 => IF input_signal = '1' THEN state <= state2; ELSE state <= state3; END IF; ... WHEN OTHERS => state <= init; END CASE; END IF; END IF; END PROCESS;

スリーツーツー

デジタルマシンは、1つ、2つ、または3つのプロセス演算子を使用して記述できます。 デジタル信号機の例を使用して、これらのオプションを検討します。

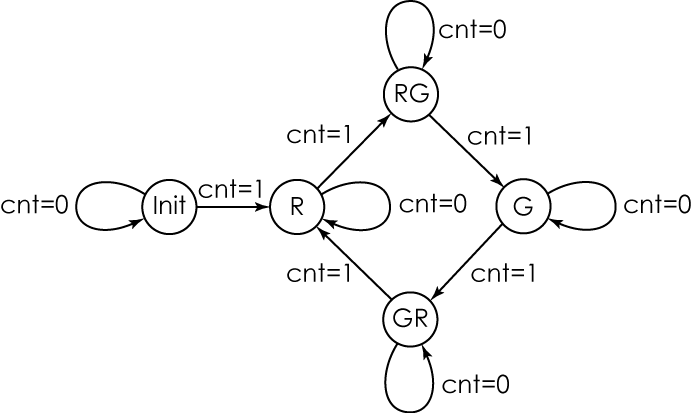

このデジタルマシンには5つの状態があります。初期(Init)、赤(R)、緑(G)、2つの黄色-1つは赤から緑(RG)に、もう1つは緑から赤(GR)に切り替えます。 入力cntがゼロに等しい場合、遷移は発生せず、入力cntが1に等しい場合、次の状態への遷移が発生します。 デジタルオートマトンのグラフを図に示します。 3。

図3-デジタル信号機のグラフ

移行テーブルと出力テーブルを使用して、同じマシンを表すことができます。 出力信号は、3ビットのベクトルで表されます。最上位ビットは赤、2番目は黄色、2番目は緑を表します。

表3-変換表

| present_ st | next_st | 遷移条件 |

| 初期化 | 初期化 | cnt = 0 |

| 初期化 | R | cnt = 1 |

| R | R | cnt = 0 |

| R | Rg | cnt = 1 |

| Rg | Rg | cnt = 0 |

| Rg | G | cnt = 1 |

| G | G | cnt = 0 |

| G | GR | cnt = 1 |

| GR | GR | cnt = 0 |

| GR | R | cnt = 1 |

表4-出力テーブル

| present_st | 出力 |

| 初期化 | 000 |

| R | 100 |

| Rg | 010 |

| G | 001 |

| GR | 010 |

CAの状態を記述するには、すべての状態がリストされる列挙型を記述する必要があります。 上記の例では、 state_typeタイプが導入されており、これには5つの値Init、R、RG、G、GRが含まれています。 デジタルマシンの特定のインスタンスを動作させるには、このタイプの信号を記述する必要があります。 例では、これらはそれぞれオートマトンの後続の状態と現在の状態を保存するための信号next_st、present_s tです。 プロセスを実行するとき、この信号はデジタルマシンの現在の状態の値を取ります。

次に、 3つのプロセス (図4)を使用してこのデジタルオートマトンの説明を検討します。各プロセスは、デジタルオートマトンの個別の部分を説明します。

-遷移ロジックの組み合わせ部分。

-出力信号の組み合わせ部分。

-シリアル部分は、デジタルオートマトンの状態を記録するためだけのものです。

図4-3つのプロセスを備えたデジタルマシン

デジタルオートマトンを記述するためのこのようなオプションにより、開発者は出力信号を生成するロジックから遷移ロジックを分離し、状態ストレージレジスタにオートマトンの状態を同期的に記録できます。 これにより、同期デジタルマシンの記述とデバッグが容易になります。

プログラム自体は、上記の3つのプロセスの組み合わせです。

3つのプロセスを使用したデジタルマシンの説明

LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY traffic IS PORT(clk : IN std_logic; cnt : IN std_logic; reset : IN std_logic; output : OUT std_logic_vector(2 downto 0) ); END ENTITY; ARCHITECTURE rtl OF traffic IS TYPE state_type IS (Init, R, RG, G, GR); SIGNAL next_st, present_st: state_type; BEGIN state_proc: PROCESS (present_st, cnt) BEGIN CASE present_st IS WHEN Init => IF cnt = '1' THEN next_st <= R; ELSE next_st <= Init; END IF; WHEN R => if cnt = '1' THEN next_st <= RG; ELSE next_st <= R; END IF; WHEN RG => IF cnt = '1' THEN next_st <= G; ELSE next_st <= RG; END IF; WHEN G => IF cnt = '1' THEN NEXT_st <= GR; ELSE next_st <= G; END IF; WHEN GR => IF CNT = '1' THEN next_st <= R; ELSE next_st <= GR; END IF; WHEN OTHERS => next_st <= Init; END CASE; END PROCESS; next_st_proc: PROCESS (clk, reset) BEGIN IF reset = '1' THEN present_st <= Init; ELSIF (rising_edge(clk)) THEN present_st <= next_st; END IF; END PROCESS; out_proc: PROCESS (present_st) BEGIN CASE present_st IS WHEN Init => output <= "000"; WHEN R => output <= "100"; WHEN RG => output <= "010"; WHEN G => output <= "001"; WHEN GR => output <= "010"; END CASE; END PROCESS; END rtl;

Quartus IIパッケージのコンパイル中に得られたCAグラフは、図5(ツール-ネットリストビューアー-ステートマシンビューアーメニュー)に表示されます。

図5-3つのプロセスを備えたデジタルマシン。 コンパイル結果

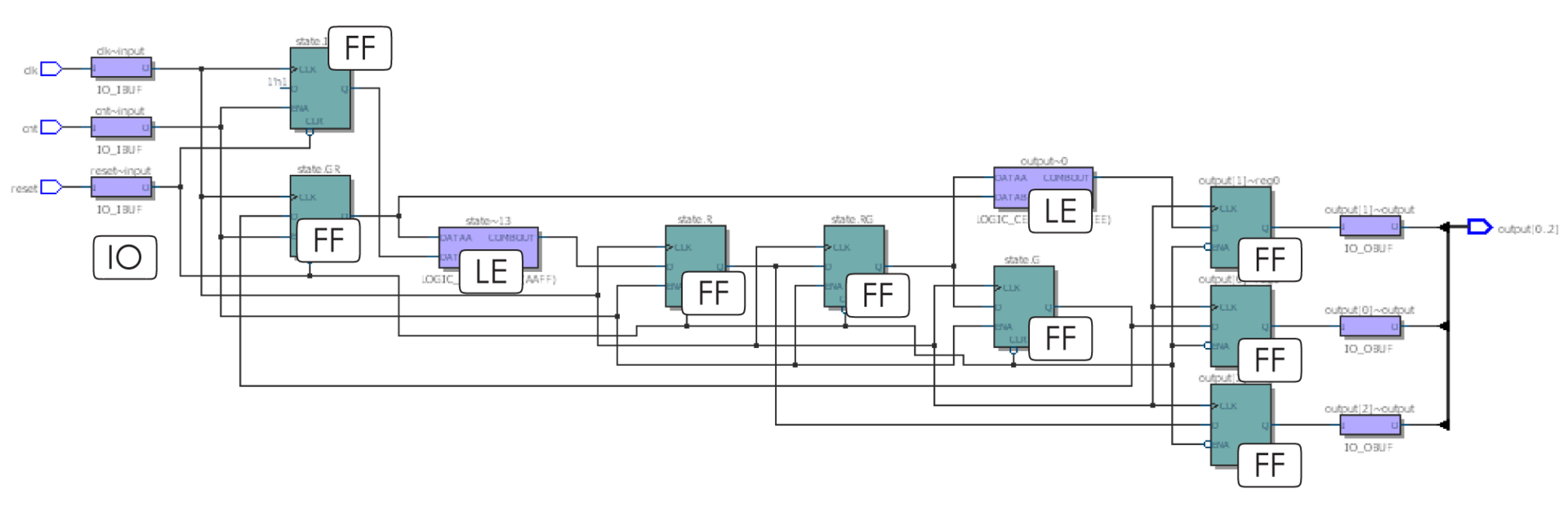

上記のリストに示されているプログラムの合成の結果を図3に示します。 6([ツール]メニュー-ネットリストビューアー-テクノロジーマップビューアー)。 図の理解を容易にするため、I / OエレメントはIO、トリガーはFF、ロジックエレメントはLEとして示されています。 合成の結果からわかるように、デジタルマシンの状態を保存するための5つのトリガーのスキーム(One Hotコーディング方式の場合)と、遷移スキームを実装し、出力信号を生成するための2つの論理要素を取得します。

図6-3つのプロセスを備えたデジタルマシン。 テクノロジーマップビューアー

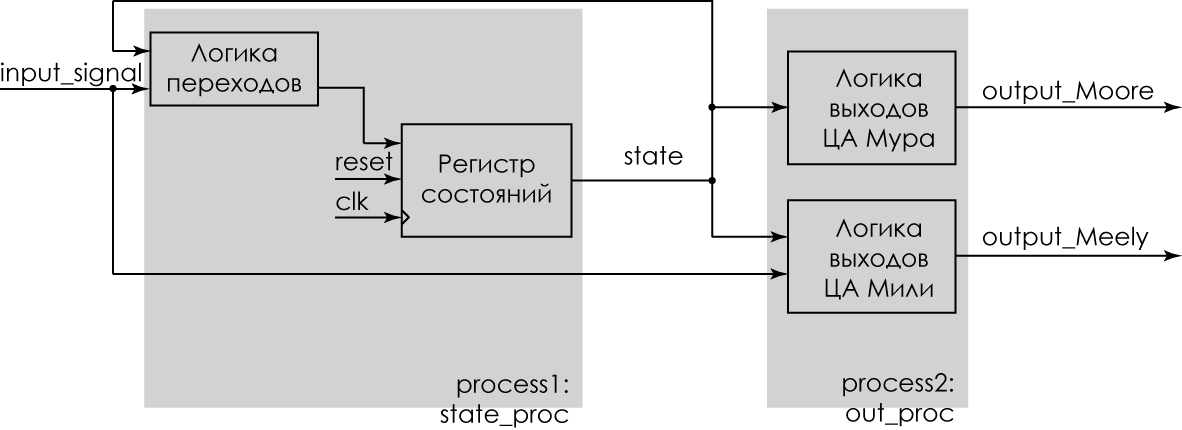

2つのプロセスの助けを借りた説明(図6)では、遷移ロジックのブロックと状態レジスターが1つのプロセスに結合され、 ケースオペレーターを使用して、デジタルオートマトンの将来の状態が選択されると仮定しています。 現在の状態と将来の状態の信号を分離する必要がないため、これらの2つの信号は、デジタルマシンの状態が格納されるstateに置き換えられます。

以下のリストは、非同期リセットを使用したCA記述の例を示しています。 コンパイルの結果として、前のケースと同じ結果が得られます-図7

図7-2つのプロセスを備えたデジタルマシン

2つのプロセスを使用するCAの説明。 非同期リセット

LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY traffic IS PORT(clk : IN std_logic; cnt : IN std_logic; reset : IN std_logic; output : OUT std_logic_vector(2 downto 0) ); END ENTITY; ARCHITECTURE rtl OF traffic IS TYPE state_type IS (Init, R, RG, G, GR); SIGNAL state: state_type; BEGIN state_proc: PROCESS (clk, reset) BEGIN IF reset = '1' THEN state <= Init; ELSIF (rising_edge(clk)) THEN CASE state IS WHEN Init => IF cnt = '1' THEN state <= R; ELSE state <= Init; END IF; WHEN R => IF cnt = '1' THEN state <= RG; ELSE state <= R; END IF; WHEN RG => IF cnt = '1' THEN state <= G; ELSE state <= RG; END IF; WHEN G => IF cnt = '1' THEN state <= GR; ELSE state <= G; END IF; WHEN GR => IF cnt = '1' THEN state <= R; ELSE state <= GR; END IF; END CASE; END IF; END PROCESS; out_proc: PROCESS (state) BEGIN CASE state IS WHEN Init => output <= "000"; WHEN R => output <= "100"; WHEN RG => output <= "010"; WHEN G => output <= "001"; WHEN GR => output <= "010"; END CASE; END PROCESS; END rtl;

2つのプロセスによって記述される同期リセットを備えたデジタルマシンを以下に示します。 Technology Map Viewerの合成結果を図に示します。 図8から、非同期リセットを備えたオートマトンと比較して、オートマトンの組み合わせ部分のサイズが大幅に増加していることがわかります。

2つのプロセスを使用するCAの説明。 同期リセット

LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY traffic IS PORT(clk : IN std_logic; cnt : IN std_logic; reset : IN std_logic; output : OUT std_logic_vector(2 downto 0) ); END ENTITY; ARCHITECTURE rtl OF traffic IS TYPE state_type IS (Init, R, RG, G, GR); SIGNAL state: state_type; BEGIN state_proc: PROCESS (clk) BEGIN IF (rising_edge(clk)) THEN IF reset = '1' THEN state <= Init; ELSE CASE state IS WHEN Init => IF cnt = '1' THEN state <= R; ELSE state <= Init; END IF; WHEN R => IF cnt = '1' THEN state <= RG; ELSE state <= R; END IF; WHEN RG => IF cnt = '1' THEN state <= G; ELSE state <= RG; END IF; WHEN G => IF cnt = '1' THEN state <= GR; ELSE state <= G; END IF; WHEN GR => IF CNT = '1' THEN state <= R; ELSE state <= GR; END IF; END CASE; END IF; END IF; END PROCESS; out_proc: PROCESS (state) BEGIN CASE state is WHEN Init => output <= "000"; WHEN R => output <= "100"; WHEN RG => output <= "010"; WHEN G => output <= "001"; WHEN GR => output <= "010"; END CASE; END PROCESS; END rtl;

図8-同期リセットを使用したデジタルマシンの合成結果

1つのプロセスを使用するデジタルオートマトンの説明では、すべてのロジックが1つのプロセスにあると想定しています。 一部の著者[5]は、1つのプロセスを使用してデジタルオートマトンを記述する方が簡単であり、デジタルオートマトンの記述とデバッグが容易になると考えています。 この声明は、小型のデジタル自動販売機に当てはまります。 状態の数が増え、1つのプロセスが使用されると、コードの可読性が低下します。 なぜなら、古代ローマ人でさえ、デジタルマシンを記述するときに「分割して征服する」というルールを使用していたからです。

デジタルオートマトンを記述するときに単一のプロセスを使用することを支持するもう1つの議論は、このオプションには同期出力信号の使用が含まれることです。 この条件は、すべてのCAに必須ではなく、簡単に達成できます。これは、出力信号の形成のロジックを説明するときに上記で示したものです。

それでも、イメージを完成させるために、単一プロセスを使用した非同期リセットを備えたデジタルマシンの説明の例を示します。

1つのプロセスでのCAの説明

LIBRARY IEEE; USE ieee.std_logic_1164.ALL; ENTITY traffic IS PORT(clk : IN std_logic; cnt : IN std_logic; reset : IN std_logic; output : OUT std_logic_vector(2 downto 0) ); END ENTITY; ARCHITECTURE rtl OF traffic IS TYPE state_type IS (Init, R, RG, G, GR); SIGNAL state: state_type; BEGIN PROCESS (clk, reset) BEGIN IF reset = '1' THEN state <= Init; ELSIF (rising_edge(clk)) THEN CASE state IS WHEN Init => IF cnt = '1' THEN state <= R; ELSE state <= Init; END IF; output <= "000"; WHEN R => IF cnt = '1' THEN state <= RG; ELSE state <= R; END IF; output <= "100"; WHEN RG => IF cnt = '1' THEN state <= G; ELSE state <= RG; END IF; output <= "010"; WHEN G => IF cnt = '1' THEN state <= GR; ELSE state <= G; END IF; output <= "001"; WHEN GR => IF cnt = '1' THEN state <= R; ELSE state <= GR; END IF; OUTPUT <= "010"; END CASE; END IF; END PROCESS; END rtl;

プログラムのコンパイル結果は、図\ ref {FSM_1process_TMView}に示されています。 明らかに、結果は2つのプロセスを使用した説明と同じであることが判明しましたが、唯一の違いがあります。出力レジスタのトリガーが追加されました。

図9-1つのプロセスを備えたデジタルマシン

私たちの研究の結果を要約する。

何よりもまず。 デジタルマシンが存在します! 写真5で彼を見ました。

二番目。 2つと3つのプロセスを使用した説明でも同じ結果が得られ、説明方法の選択は開発者の好みに依存します。

三番目。 マシンの初期リセットと未使用状態の説明には十分に注意する必要があります。

4番目。 1つのプロセスを使用した記述により、デジタルマシンの出力信号用のレジスタが表示されます。

参照資料

1.アルテラ。 Quartus IIハンドブックバージョン10.0 Volume 1:Design and Synthesis Vol。 1、2010-1820 p。

2. B.コーエン。 VHDLコーディングスタイルと方法論。 Kluwer Academic Publishers。2002-454 p。

3. DLペリー。 例によるVHDLプログラミング。 ニューヨーク:McGraw-Hill、2002.- 476 p。

4. DJスミス。 HDLチップ設計:VHDLまたはVerilogを使用してASICおよびFPGAを設計、合成、およびシミュレーションするための実用的なガイド。 マディソン、アラバマ州:Doone Publications、1996 .-- 448 p。

5. A.テイラー。 FPGAにステートマシンを実装する方法。 Xcell 81(4)、p。 52-57。

6.ザイリンクス。 VHDLリファレンスガイド。 XSTユーザーガイド。

7. K. G.サモファロフ。 デジタルオートマトンの応用理論。 M。:、1987.375秒

PS PDFバージョンはこちらです。