良い一日! 前の記事で、 Altreraの SoCをゼロから「上げる」方法について説明しました。

プロセッサによってコピーが実行されたときに、 CPUとFPGA間のスループットを測定することに決めました。

今回はもう少し進んで、プリミティブDMAをFPGAに実装します。

誰が気にします-猫へようこそ。

中古鉄

前回は、 EBVの SoCratesを使用しました 。

今回は、私たち自身の開発のボードを使用します-写真に示されているのはそれです。

主な違いは、ボードに2 ギガビットイーサネットインターフェイスがあり、CPUにではなく、FPGAに接続されていることです。

これにより、非常に柔軟なトラフィック処理が可能になります。 さらに、多数のピンがコネクタに出力されます。

しかし、これらの違いは、以下の記事でのみ重要になります。

1つは、FPGAにNICを実装することです。これには、もちろん、ギガビットインターフェイスを使用します。 別の方法では、再びILI9341ディスプレイのフレームバッファーサポートをFPGAで記述します。これには拡張カードが必要です。

また、以下で説明するアクションを実行するには、 SoC Cyclone Vを搭載したボードが適しています

ソースコード

記事の過程で、重要なコードのみを説明します。

すべてのソースコードはgithubで表示できます

詳細

前の記事で説明したカーネルの構築、ブートローダーの取得、その他のアクションの詳細については説明しません。

カーネルに関する注意-ここから最新のカーネルバージョン3.18を使用することをお勧めします。

git clone git://git.rocketboards.org/linux-socfpga.git git checkout remotes/origin/socfpga-3.18

実装について考える

DMAコントローラの選択

したがって、私たちの目標は、最大帯域幅と最小CPU負荷でFPGAからプロセッサにデータを転送することです。

プロセッサをコピーするオプションはすぐに消えます。DMAを使用する必要があります。 しかし、誰がDMAコントローラーの役割を果たすことができますか?

SoCには、FPSまたはHPSに組み込まれたDMA-330コントローラーの2つのオプションがあります。

ネットワークに関する議論から判断すると、DMA-330の生産性はそれほど高くなく、対応するドライバーも完全には動作しない可能性があります。

おそらくいつか、DMA-330を「復活」させようとしますが、今ではFPGAを選択します

インターフェースの選択

DMAコントローラの機能を実行するには、FPGAがウィザードでなければなりません。 これは、次の2つのインターフェースのいずれかで実装できます。

- FPGAからHPS( fpga2hps )

- FPGA-to-HPS SDRAM( fpga2sdram )

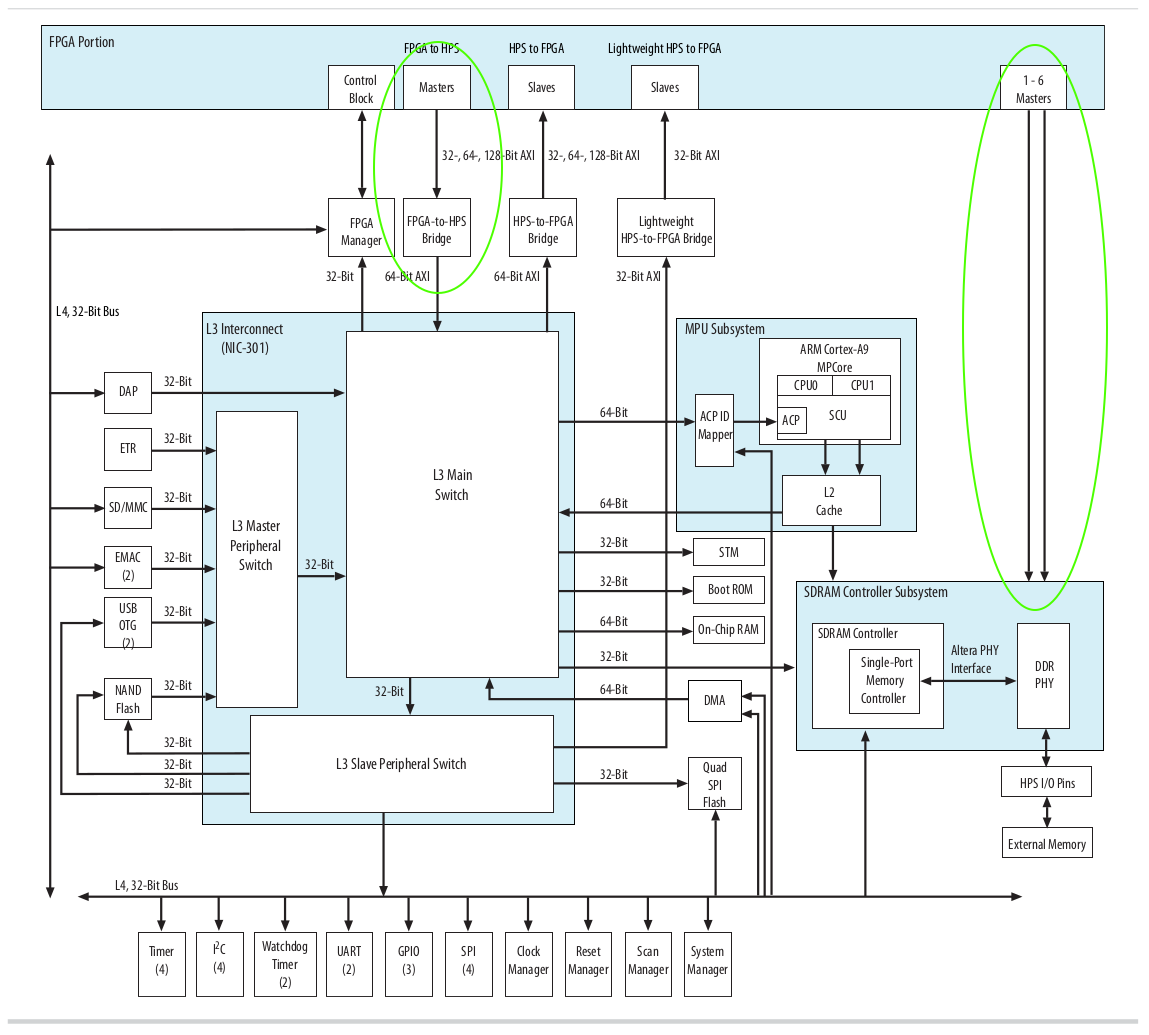

HPSコンポーネントとそれらの間のインターフェースのブロック図:

HPSアーキテクチャ

各オプションの長所と短所を見てみましょう。

fpga2hpsを使用すると、FPGAのマスターがシステム内のほぼすべてのスレーブにアクセスできます。 それは、記憶としてだけでなく、多様な周辺への、ということです。

fpga2sdramを使用すると、FPSがHPSが「所有」するDPSメモリと連携できます。 この場合、アクセスはRAMによってのみ制限されます。

fpga2sdramを使用すると、より多くの帯域幅を取得できます。

fpga2hpsを使用すると、1つのインターフェイスで交換が行われます。 FPGAに複数のマスターが必要な場合は、調停が必要です。 そのため、独自のモジュールを作成するか、Qsysを使用して生成されたモジュールを使用する必要がありますが、これらはかなりリソースを消費します。

一方、最大6つの独立したポートをfpga2sdramで作成でき、DDRコントローラーは調停のすべての問題を解決します。

注:番号6は完全に「正直」ではありません-6つのコマンドポート、4つの書き込みポート、4つの読み取りポートが使用可能です。

同時に、1つの128ビットインターフェイスでは、最初のコマンドポート、2つの書き込みポート、2つの読み取りポートを使用する必要があります。

fpga2hpsとfpga2sdramは、使用する前に適切なレジスタに書き込むことで初期化する必要があります。 残念ながら、 fpga2sdramの場合、これはFPGAファームウェアの後で行う必要がありますが、現時点ではインターフェイスでトランザクションが発生していません。 実際、 Linuxを使用する場合、これはUブートでFPGAをフラッシュする必要があることを意味します。 詳細はこちらをご覧ください 。

fpga2hpsを使用する場合、FPGA のマスターはfpga2sdramを使用する場合、ワードのアドレスであるバイトアドレスを使用する必要があります。

詳細については、 Cyclone V Device Handbook、Volume 3:Hard Processor System Technical Reference Manualを参照してください 。

HPS-FPGAブリッジの第8章および11 SDRAMコントローラーサブシステム 。

このタスクでは、何を使用するかという基本的な違いはありません。 より多くの帯域幅を取得することを期待して、 fpga2sdramを選択しましょう。

DMAコントローラの実装を選択する

DMAコントローラーをFPGAに実装し、どのインターフェイスを介して機能するかを決定しました。

しかし、コントローラー自体をどのように作成するのでしょうか? 開いている「ピール」の1つ 、たとえばこの1つを使用できます。これはQsysからも利用できます。

これは、多くの便利な機能を備えた優れたDMAコントローラーです。 NICを実装すると、それに戻ります。

しかし今、私たちの仕事にとって、そのようなコントローラーは不必要な機能と不必要な複雑さです。

学習タスクの場合、DMAコントローラーの本質が非常にシンプルであることを理解するために、FPGAでいくつかのカウンターをスケッチすることをお勧めします。

トップレベル

ソフトウェア側からも、すべてが非常に単純です。メモリを割り当て、このメモリのバスアドレスを取得し、FPGAでDMAコントローラを構成して起動し、トランザクションが完了してデータを受信するのを待つドライバが必要です。

そして、それを書きます。 しかし、ドライバーからではなく、同じ機能を実行するユーザースペースの少し奇妙なプログラムから始めます。

これにより、カーネルレベルで何かを記述することなく、FPGAでDMAコントローラーを操作できます。

「プロダクション」では、このようなソリューションは通常使用されませんが、デバッグに便利な場合があります。

FPGAのファームウェアを簡単にするために、FPGA-> CPUの方向にデータを転送します。

反対方向のデータ転送は、以下で説明する1つのニュアンスを除き、ほぼ完全に類似しています。

CPU-> FPGAの方向で、 LCDのフレームバッファの実装を処理します。

だから、計画:

- FPGAのファームウェア

- ユーザースペースのプログラム

- カーネルドライバー

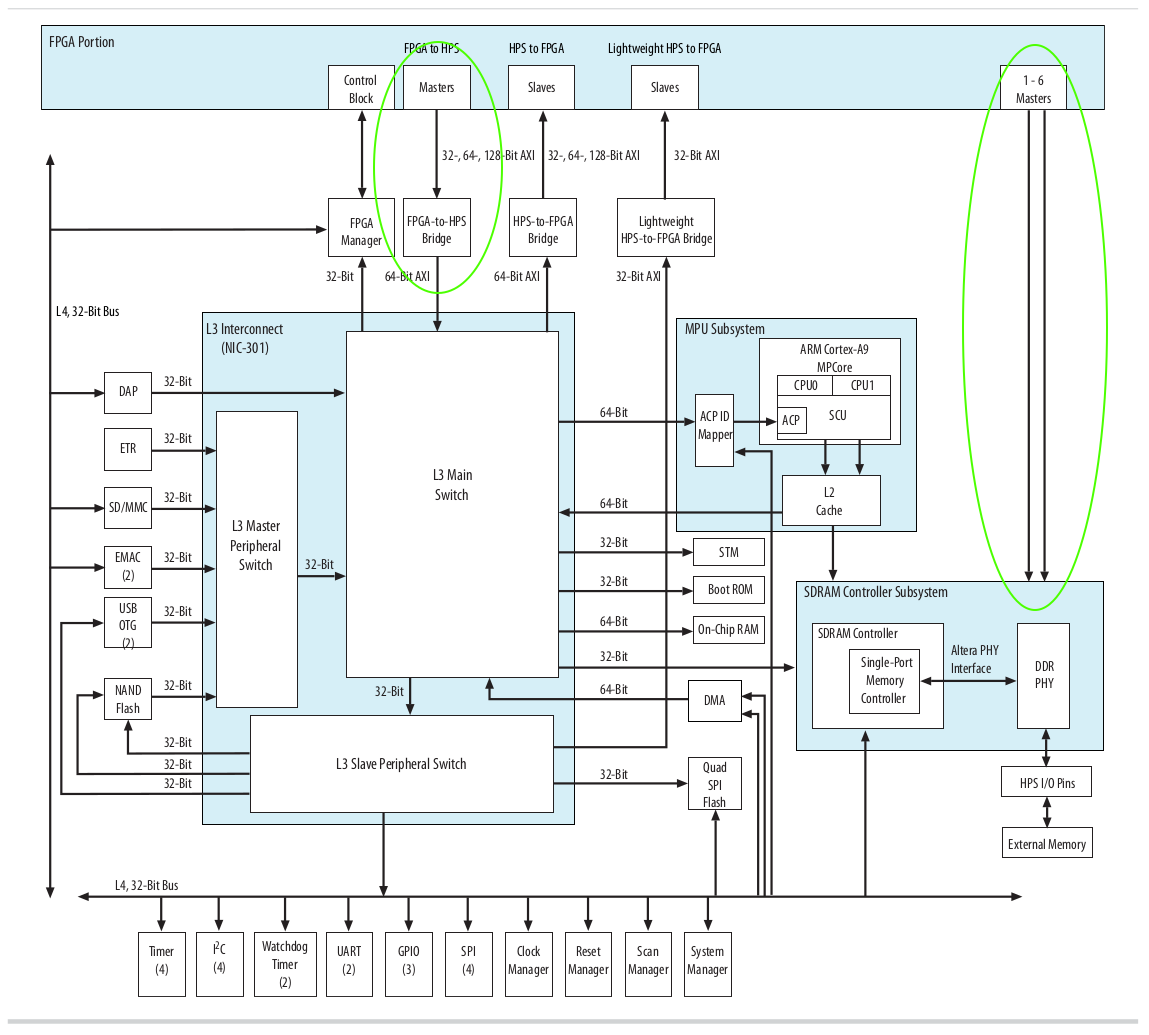

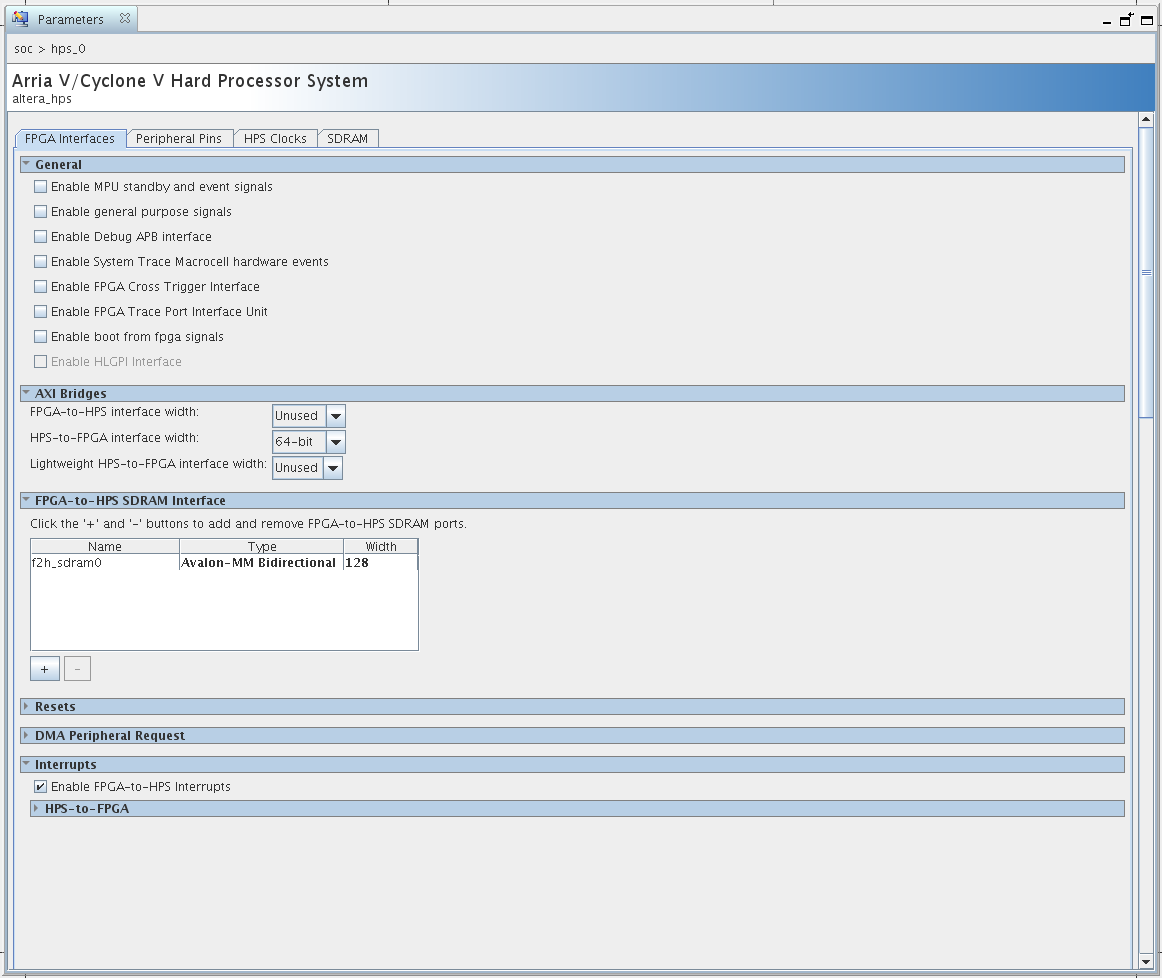

FPGAファームウェアの実装

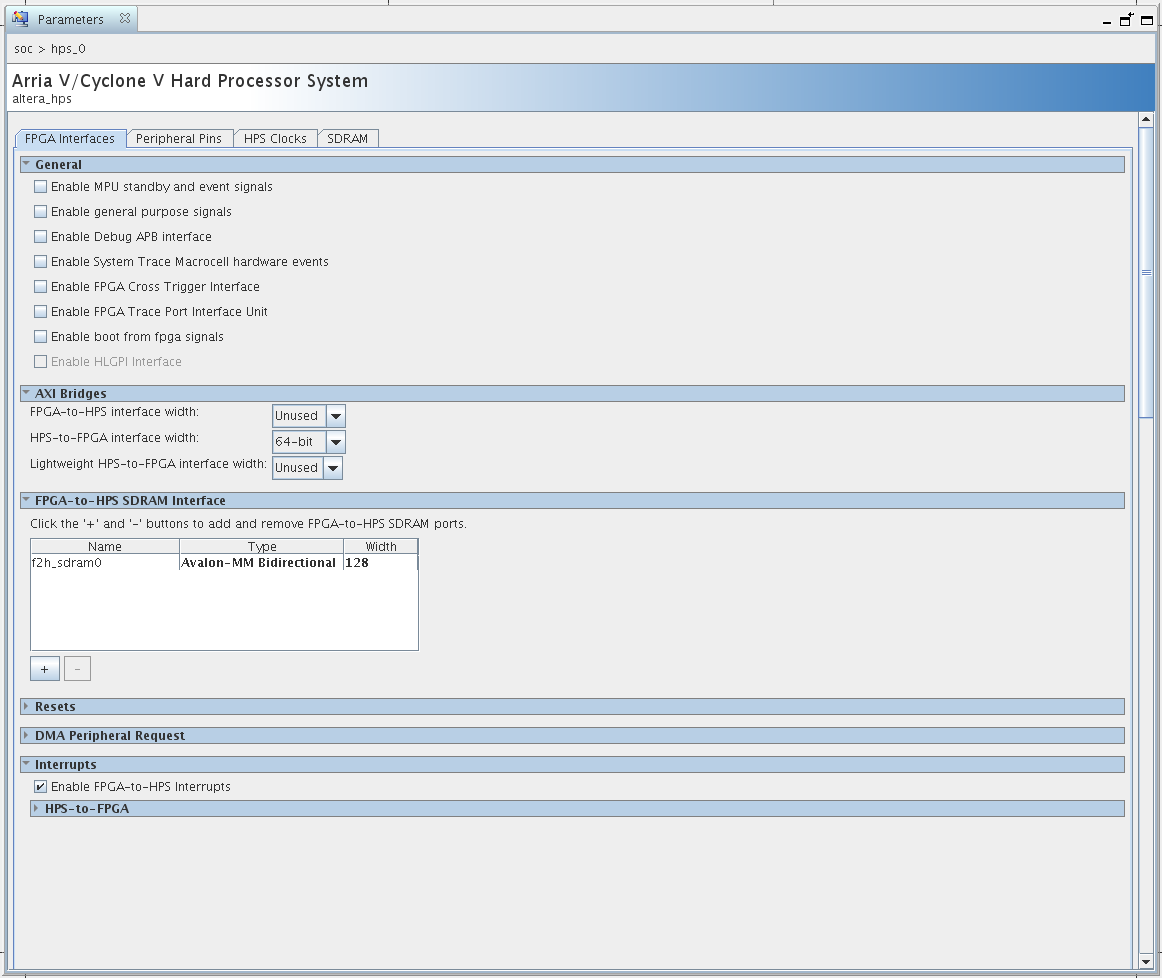

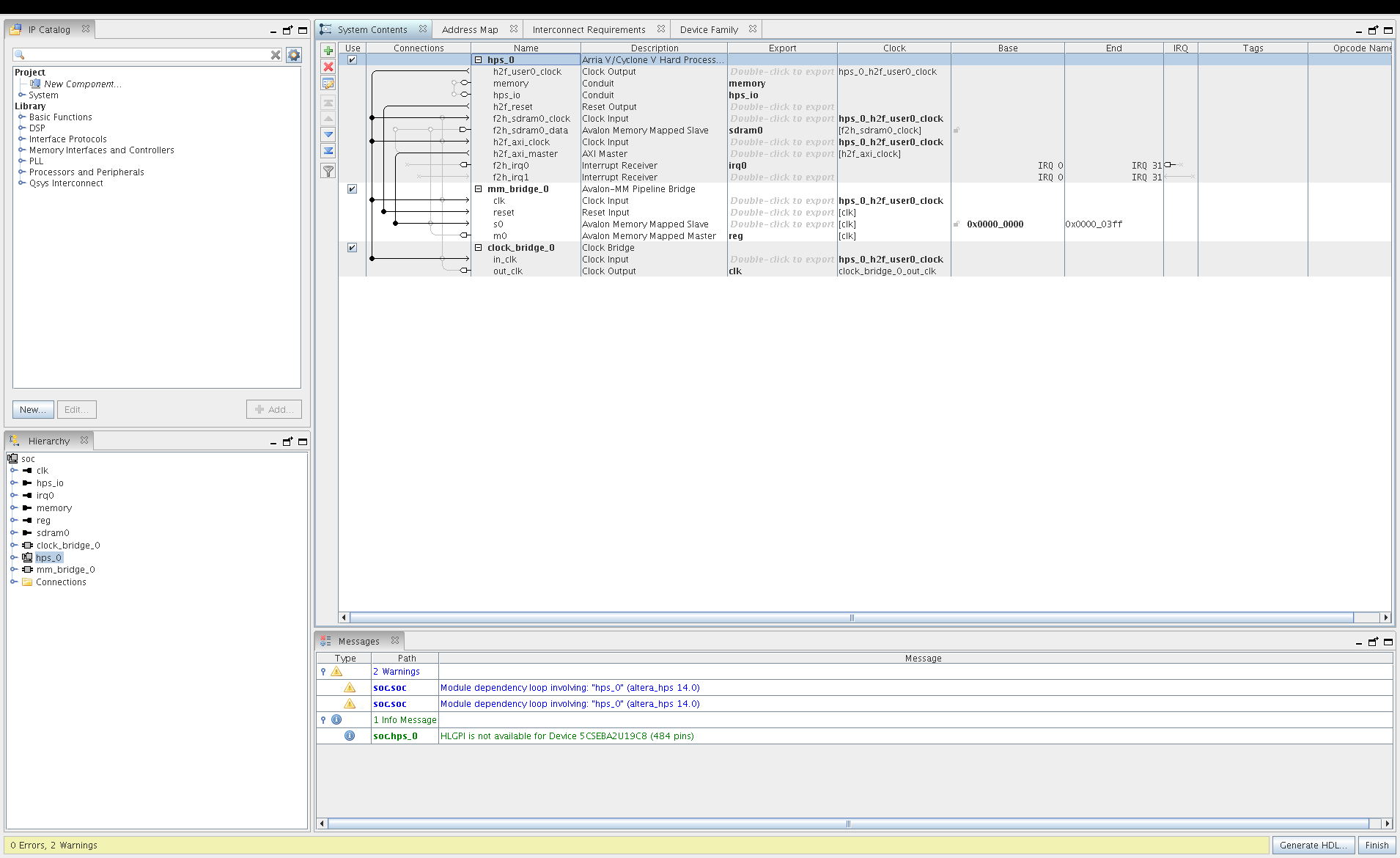

最愛のQsysから始めましょう。 次の3つのIPピールが必要です。

- プロセッサーと周辺機器->ハードプロセッサーシステム-> Arria V / Cyclone Vハードプロセッサーシステム

- 基本機能->ブリッジとアダプター->メモリマップ-> Avalon-MM Pipeline Bridge

- 基本機能->ブリッジとアダプター->クロック->クロックブリッジ

HPSについては、すべてを前の記事とほぼ同じにしておきます。

[ FPGA Interfaces ]タブで、 FPGA-to-HPS SDRAMインターフェイスを追加する必要があります。

タイプAvalon-MM Bidirectional 、width-128ビットを選択します。

[ FPGAからHPSへの割り込みを有効にする]の横にあるチェックボックスもオンにする必要があります。

これにより、DMAコントローラーは割り込みを介してトランザクションの完了をCPUに「通知」できます。

また、 HPS-FPGAインターフェイスの幅は64ビットに設定する必要があります。 これは、CPUがDMAコントローラーを構成するためのインターフェースです。

その幅は任意で、64ビットを設定したのは、このような幅を選択したためであり、この値に対して以下で説明するソースコードが構成されています。

取得する必要があるものは次のとおりです。

FPGAインターフェース

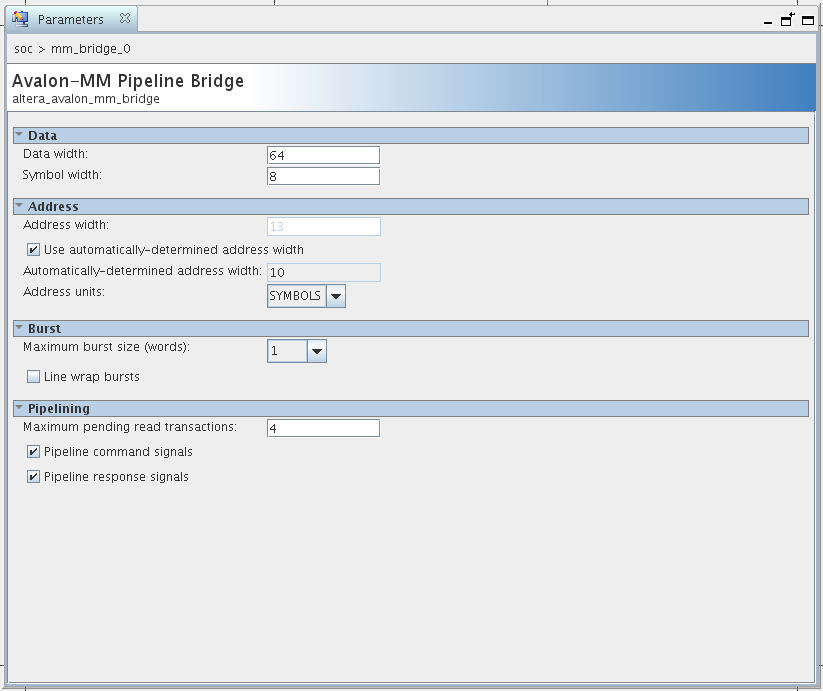

Avalon-MM Bridgeに移動します。

この皮はコンバーターとして機能します。 HPS-to-FPGAを自動生成されたQsysモジュールから外部にエクスポートする必要があります。

しかし、これを行うだけでAXIインターフェイスが得られますが、これはAvalon-MMよりもはるかに複雑です。 そして、誰とも一緒に働きたくありません。 このモジュールを追加すると、QsysはAXIをAvalonに自動的に変換します。 いくつかのリソースが必要になりますが、作業するのがはるかに便利です。

次のようにモジュールを構成する必要があります。

Avalon-mmブリッジ

最後のモジュールに進みます。 HPSから外部にロックをエクスポートして、このロックのDMAコントローラーを同期できるようにするために必要です。 その設定はプリミティブです-1に等しいシュレッドの数を指定するだけです。

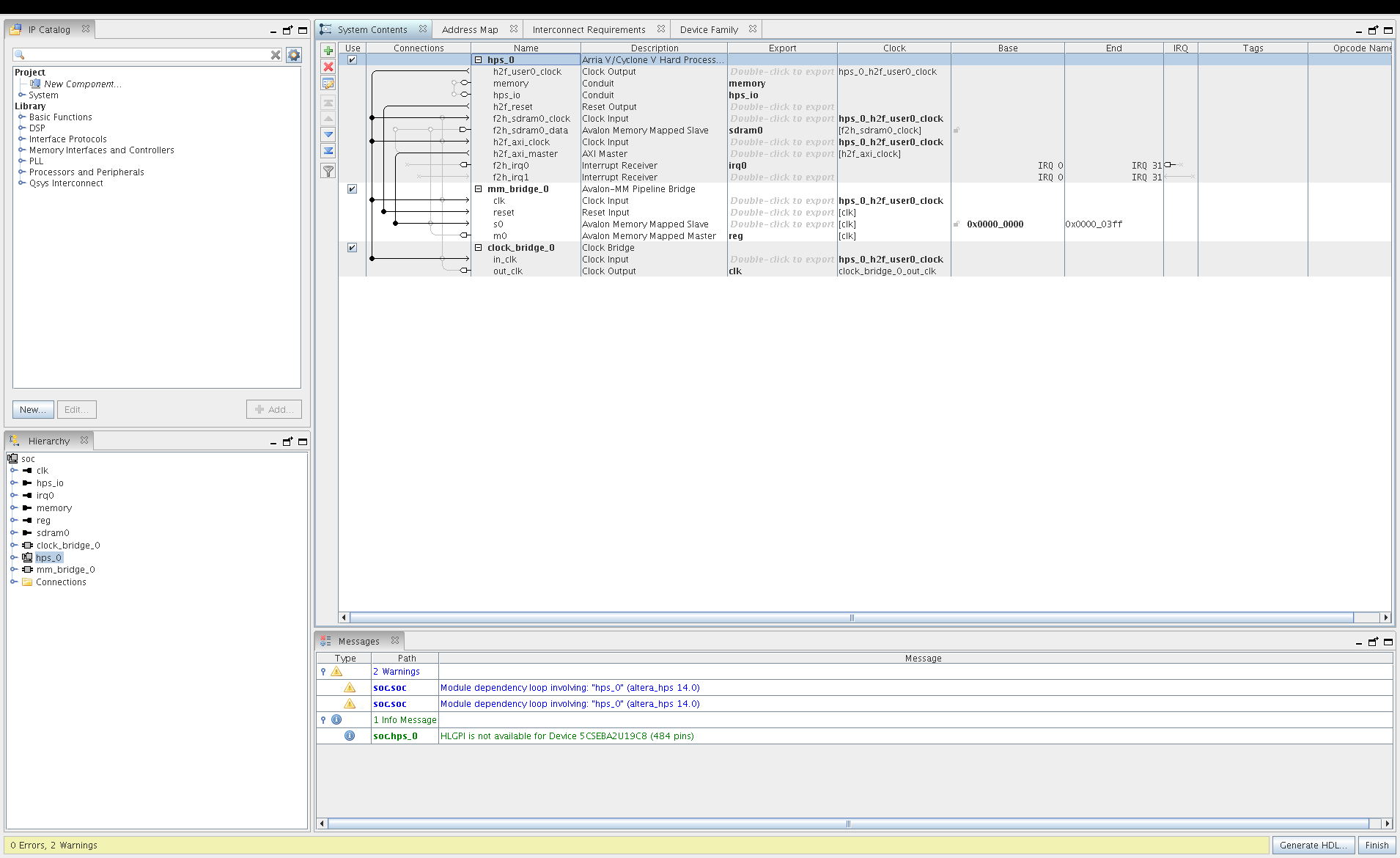

その後、すべてのモジュールを接続する必要があります([ エクスポート ]列の名前に注意してください)。

Qsys接続

ファイルを保存および生成するために残ります。

プリミティブDMAコントローラを実装するときが来ました。 どのように設定しますか?

カスタマイズには、いわゆる制御およびステータスレジスタ( CSR )を使用します

これらは、CPUが読み取り/書き込み(制御)または読み取り専用(ステータス)に使用できる固定サイズのブロックです。

これらのレジスタへのアクセスは、 HPS-to-FPGAを介して行われます。

インターフェイスの幅は64ビットなので、レジスタを同じ幅にするか、コンバータを追加できます。

レジスタを64ビットにすることは非常に高価です。 実際、非常に多くの場合、レジスタ全体では数ビットのみが使用されます。

レジスタを16ビットにすることをお勧めします。高ビットワードが必要になる場合は、2つまたは4つの隣接するレジスタを使用します。

理論的には、Qsysによって生成されたコンバーターを使用して、 Avalon-MM Bridge IPピールに16ビットの幅を指定することができましたが、実際にはこれを行うことができませんでした-Qsysは動作不能なモジュールを生成しました。 大丈夫、私たちはそれを使用します:)

avalon_width_adapter.svモジュールはコンバーターとして使用され、レジスタ自体はregfile_with_be.vモジュールで実装されます

レジスタモジュールのロジックは非常に単純です。アドレスに応じて、目的のレジスタの内容を読み取りバスに設定します。 書き込み信号も到着した場合、入力データをレジスタに保存します。 アドレスは、バイト番号ではなくレジスタ番号を指定します。 制御およびステータスレジスタへの分割方法は、アセンブリ中のパラメータ-アドレスの上位ビット(この場合、アドレス空間は制御およびステータスレジスタ間で均等に分割されます)、またはパラメータで示されるレジスタの数によって設定されます。

DMAコントローラーに直接渡します。 簡単にするため、 最上位モジュールにあります 。

DMAコントローラーで構成されるのは、3つのカウンターと1組の信号だけです。

コントローラーがAvalon-MMインターフェースにデータを発行することを思い出させてください。 詳細な説明はここにありますが、一般的にはかなりシンプルなインターフェースです。

データを記録するには、次の信号を設定する必要があります。

- sdram0_address-アドレス( fpga2sdramの場合は単語のアドレスである必要があることを思い出させてください )。

- sdram0_writedata-書き込み用のデータ。

- sdram0_byteenable-データのどのバイトを書き込むべきかを示す信号。 簡単にするために、 16'hFFFFに設定します 。

- sdram0_burstcount-バーストを制御するための信号。 繰り返しますが、簡単にするために、1に設定します。

- sdram0_write-書き込みトランザクションを完了するには、この信号を1に設定する必要があります

注意すべき唯一の注意点は、 sdram0_waitrequest信号の存在です。 1の場合、これはスレーブが現時点でトランザクションを処理できないことを意味し、マスターはすべての信号を変更しないでおく必要があります。 sdram0_waitrequest信号が1に設定され、最終的にDMAのスループットを決定する正確な頻度。

そのため、使用されるカウンタについて説明します。 最初はアドレスカウンターaddr_cntです。 DMAトランザクションが開始されると、CPUによって指定されたアドレスに設定されます。 各トランザクションが成功した後( sdram0_waitrequestが 1 でない場合)、このカウンターは1ずつ増加します。

2番目は、データをエミュレートするためのdata_cntカウンターです。 必要なデータをデータに書き込むことができます。 主な条件は、トランザクションの完了後、ソフトウェアがメモリから記録されたデータとまったく同じデータを読み取る必要があることです。 したがって、単純なカウンターを記述することはあまり正確ではありません。データには多くのゼロがあり、レコードの有効性を検証することは困難です。 擬似ランダムシーケンスを記述するのが理想的ですが、簡単にするために、カウンターとその反転値で十分です。

3番目のカウンタ- サイクルカウンタcycle_cntは、DMAトランザクションの開始時に0にリセットされ、各サイクルで1ずつ増加します。

DMAトランザクションにかかったクロック数を調べてスループットを計算できるようにするために必要です。

合計、カウンターについては次のコードを取得します。

カウンターの説明

// For emulate data logic [63:0] data_cnt; // Current address on SDRAM iface logic [31:0] addr_cnt; // Overall cycles count. logic [31:0] cycle_cnt; // Form pseudo-data always_ff @( posedge clk_w ) if( !test_is_running ) data_cnt <= '0; else if( !sdram0_waitrequest ) if( data_cnt != ( dma_data_size - 1 ) ) data_cnt <= data_cnt + 1; // Increase address if no waitrequest always_ff @( posedge clk_w ) if( run_test_stb ) addr_cnt <= dma_addr; else if( !sdram0_waitrequest ) addr_cnt <= addr_cnt + 1; always_ff @( posedge clk_w ) if( test_is_running_stb ) cycle_cnt <= '0; else if( test_is_running ) cycle_cnt <= cycle_cnt + 1;

信号に戻ります。 必要なものは次のとおりです。

- test_is_runningは、DMAトランザクションが現在進行中かどうかを示す信号です。

- run_test_stb-ストローブ信号、CPUがDMAコントローラーを起動した時点で1クロックの間アクティブ

- test_finished-必要な量のデータが書き込まれたことを示す信号。 また、割り込みを開始します。

これらの信号の形成は簡単です。

DMAコントローラーを構成するには何が必要ですか(これらは制御レジスターになります)。

- データをコピーするバッファアドレス

- レコードデータサイズ

- トランザクションを開始するシグナル。そこからフロントを選択します

ステータスレジスタは次のとおりです。

- DMAコントローラビジー信号

- カウンター値cycle_cnt

したがって、レジスタの宣言は次のようになります。

登録宣言

// Control registers `define DMA_CTRL_CR 0 `define DMA_CTRL_CR_RUN_STB 0 `define DMA_ADDR_CR0 1 `define DMA_ADDR_CR1 2 `define DMA_SIZE_CR0 3 `define DMA_SIZE_CR1 4 // Status registers `define DMA_STAT_SR 0 `define DMA_STAT_SR_BUSY 0 `define DMA_CYCLE_CNT_SR0 1 `define DMA_CYCLE_CNT_SR1 2

そして、レジスタの目的は次のとおりです。

レジスタ割り当て

// Control from CPU -- bit for start, DMA buffer address and transaction size. assign run_test = cregs_w[`DMA_CTRL_CR][`DMA_CTRL_CR_RUN_STB]; assign dma_addr = { cregs_w[`DMA_ADDR_CR1], cregs_w[`DMA_ADDR_CR0] }; assign dma_data_size = { cregs_w[`DMA_SIZE_CR1], cregs_w[`DMA_SIZE_CR0] }; // Status for CPU -- current state and overall cycles count. assign sregs_w[`DMA_STAT_SR][`DMA_STAT_SR_BUSY] = test_is_running; assign { sregs_w[`DMA_CYCLE_CNT_SR1], sregs_w[`DMA_CYCLE_CNT_SR0] } = cycle_cnt;

すべて、プロジェクトをコンパイルできます。 最初に、 Analysis&Synthesisを実行しましょう。

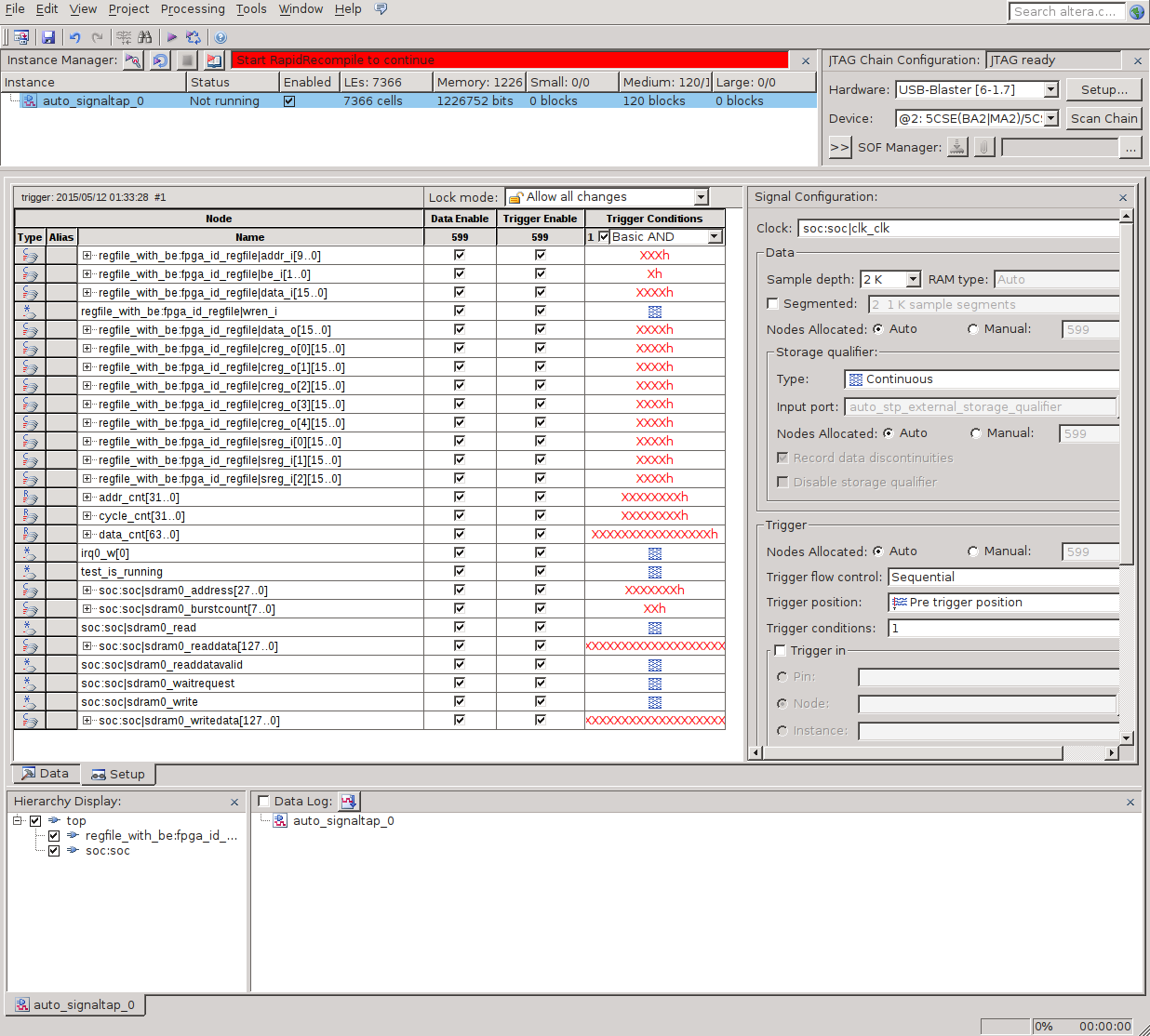

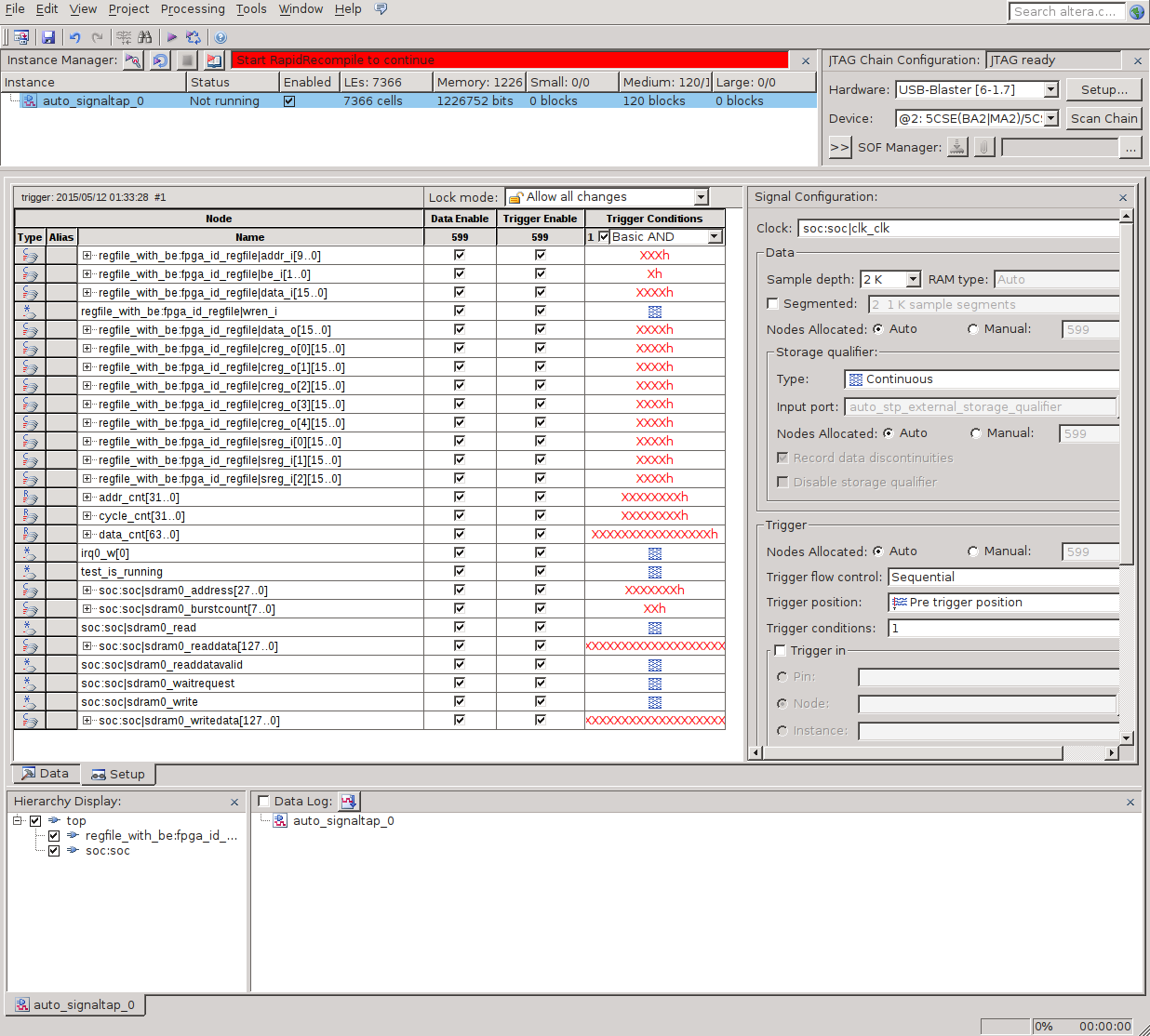

その後、 SignalTapファイルを作成します。これを使用して、 FPGA内の信号値を監視できます。

これを行うには、 [ファイル]-> [新規]-> [SignalTap II Logic Analyzer File ]に移動し、[OK]をクリックします。

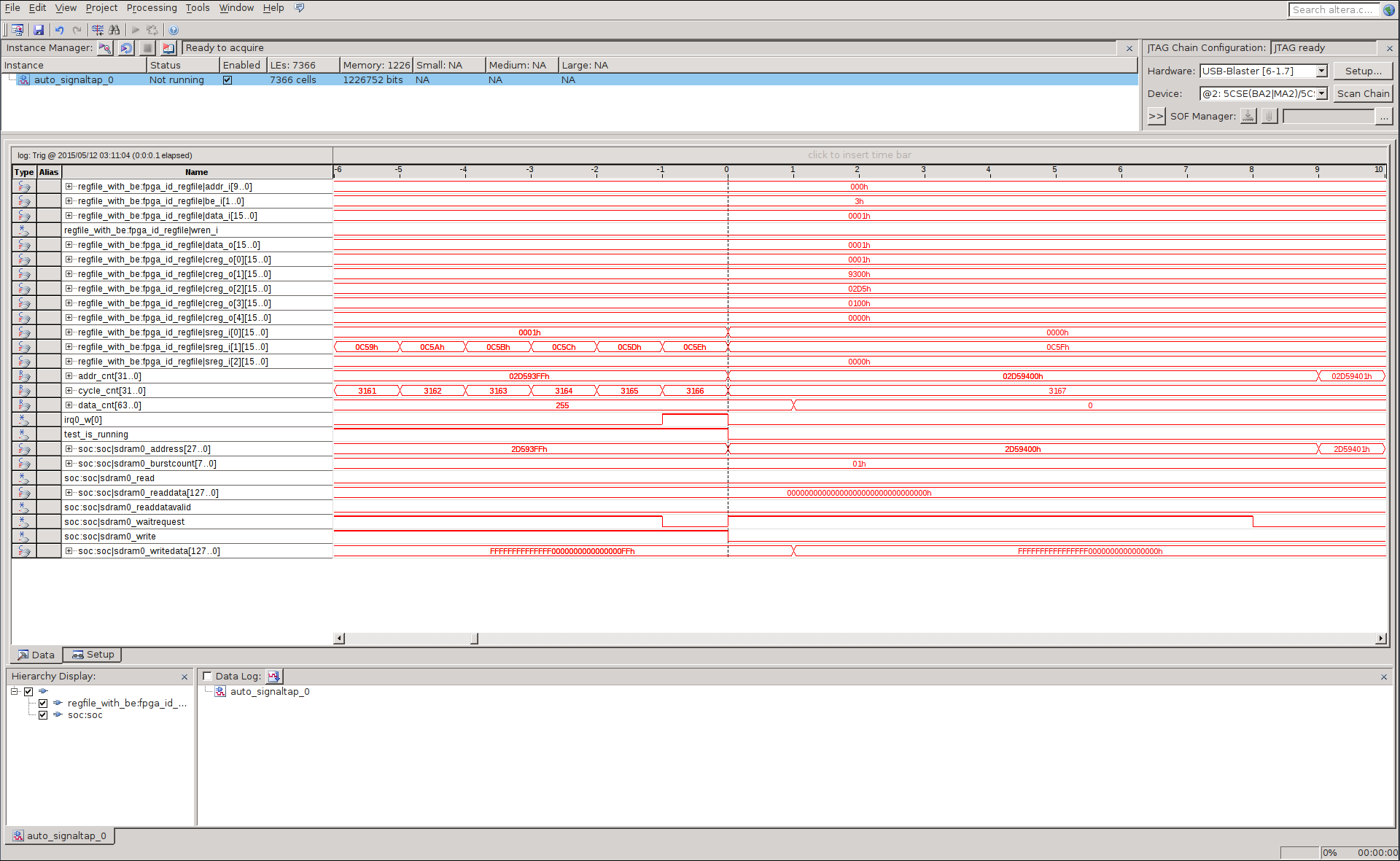

表示されるウィンドウで、必要な信号を追加します。 次のようなものが得られるはずです。

SignalTapファイル

ファイルを保存し、プロジェクトに追加して、アセンブリを完了します。

ビルドが完了したら、 .rbfファイルを取得する必要があります。

quartus_cpf -c etln.sof dma.rbf

すべて、ファームウェアの準備ができました。 ソフトウェア部分に渡します。

注意: Qsysの設定を変更した後(特にfpga2sdramを有効にした後)、 Preloaderを再生成および再構築する必要があることに注意してください。

FPGA githubでは、Verilogコードを含むファイルとQsys設定を含むファイルのみがアップロードされることに注意してください。

プロジェクトファイル(.qpf、.qsfなど)は、本当に有用な情報を運んでいないという事実のために欠落しています。

ユーザースペースプログラムの実装

ソフトウェア側からDMAコントローラーを操作するために必要なものは何ですか?

まず、DMAコントローラーを構成して実行できる必要があります。 このために、前の記事のmemプログラムを使用します。

次に、メモリ領域を取得する必要があり、そのアドレスをDMAコントローラーに渡すことができます。

ここで少し余談が必要です。 通常、ユーザー空間内のすべてのプロセス、およびカーネル内のほとんどのプロセスでさえ、いわゆる仮想アドレスで動作します。 しかし、DMAコントローラーは物理アドレスを転送する必要があります(より正確には、 バスアドレスですが、使用しているプラットフォームでは物理アドレスと同じです)。

このようなタスクを実行するカーネルには、仮想アドレスで物理アドレス(またはその逆)を取得したり、メモリ領域を割り当てたり、それを指す2つのアドレスを一度に取得したりできる特別な機能のセットがあります。

ユーザースペースで何をする? 素晴らしいプロセス/ proc / [PID] / pagemapには 、すべての仮想ページからあらゆるプロセスの物理ページへのマッピングに関する情報が含まれています。

このファイルの各ページの情報は8バイトです。 同時に、下位55ビットには、いわゆる物理ページ番号-ページフレーム番号( PFN )が含まれ、上位9ビットにはさまざまなフラグ(ページの存在、スワップなど)が含まれます。詳細な説明は、 ここまたはman procにあります。

したがって、仮想アドレスとページサイズがわかれば、仮想ページの数を簡単に計算できます。 その後、ファイル/ proc / [PID] /ページマップから、必要なオフセットで8バイトを読み取るだけで、下位55ビットに物理ページの番号があります。 そして、それを物理アドレスに変換することはすでに簡単であり、それをDMAコントローラーに書き込みます。

メモリ領域がページの境界から始まる場合、すべてが少し簡単になります。

したがって、 malloc()関数の代わりに、希望のオフセットを設定できるposix_memalign()関数を使用することをお勧めします。

また、RAMからスワップするデータのアンロードを防ぐために、mlock()関数を使用することをお勧めします。

上記のことはphys_addr.cプログラムによって実行されます

重要な注意 -仮想アドレス空間で連続するページは、必ずしもRAMで連続するわけではありません。

したがって、この方法では、DMAコントローラーによるページサイズより大きいデータを書き込むことはできません。

ドライバーを作成するときに、この制限を回避できます。

中間チェック

これで、ファームウェアとテストプログラムの準備ができました。少しテストしてみましょう。

バイナリをSDカードにコピーし、 USB-Blasterを接続してボードを実行します。

Linuxを起動する前にfpga2sdramインターフェイスを有効にする必要があることを上に書きました 。 これは事実ですが、常にそうとは限りません。

Linuxですでにインターフェイスを有効にして、FPGAからメモリ内のデータを読み取ろうとすると、システムは完全にフリーズします。

ただし、データの書き込みは成功します。 当然、このオプションは明らかに戦闘システムで使用する価値はありません。以下に、 fpga2sdramインターフェイスを適切に初期化する方法を説明します。 しかし、中間テストの場合、これは非常に適しています。

まず、FPGAをフラッシュします。

cat dma.rbf > /dev/fpga0

次に、 HPS-FPGAインターフェイスを有効にします。

echo 1 > /sys/class/fpga-bridge/hps2fpga/enable

SignalTapを実行すると、 sdram0_waitrequest信号が常に1でハングしていることがわかります。これは、 fpga2sdramインターフェイスがオフになっているためです。

オンにします:

./mem.o 0xFFC25080 0x3fff

レジスタビット0xFFC25080にユニットを書き込むと、 fpga2sdramインターフェイスの対応するポートが含まれます。 どのビットがどのポートに責任があるかに関する説明は上記のHandbookで与えられます。 簡単にするために、すべてのポートを有効にする必要があります(合計で、レジスタで14ビットが使用されます)。

SignalTapで、信号sdram0_waitrequestが 0に等しくなりました。

phys_addrユーティリティを実行します。

./phys_addr

バッファを割り当てて、その物理アドレスを表示します。 0x2d593000です。

fpga2sdramインターフェイスを使用するときは、言葉で対処する必要があることを覚えています。

128ビットのワードがあるため、ワードアドレスは次のように計算されます。

0x2d593000 / 16 = 0x2d59300

このアドレスをFPGAレジスタに書き込みます。

./mem.o 0xC0000002 0x2d59300

アドレスには、1および2の番号が付けられた制御レジスタを使用します。各アドレスは16ビットまたは2バイトです。 HPS-to-FPGAは0xC0000000から始まるため、最初の制御レジスタのバイトアドレスは0xC0000002になります

mem.cが正確にバイトアドレスを使用することを思い出させてください。

その後、DMAトランザクションの長さを制御レジスタ番号3に書き込みます。長さはページサイズを超えてはならず、私たちにとっては4096バイトです。 fpga2sdramインターフェイスの幅は128ビットであり、トランザクションサイズをワードで示すため、3番目のレジスタに256の数値を書き込む必要があります。

./mem.o 0xC0000006 256

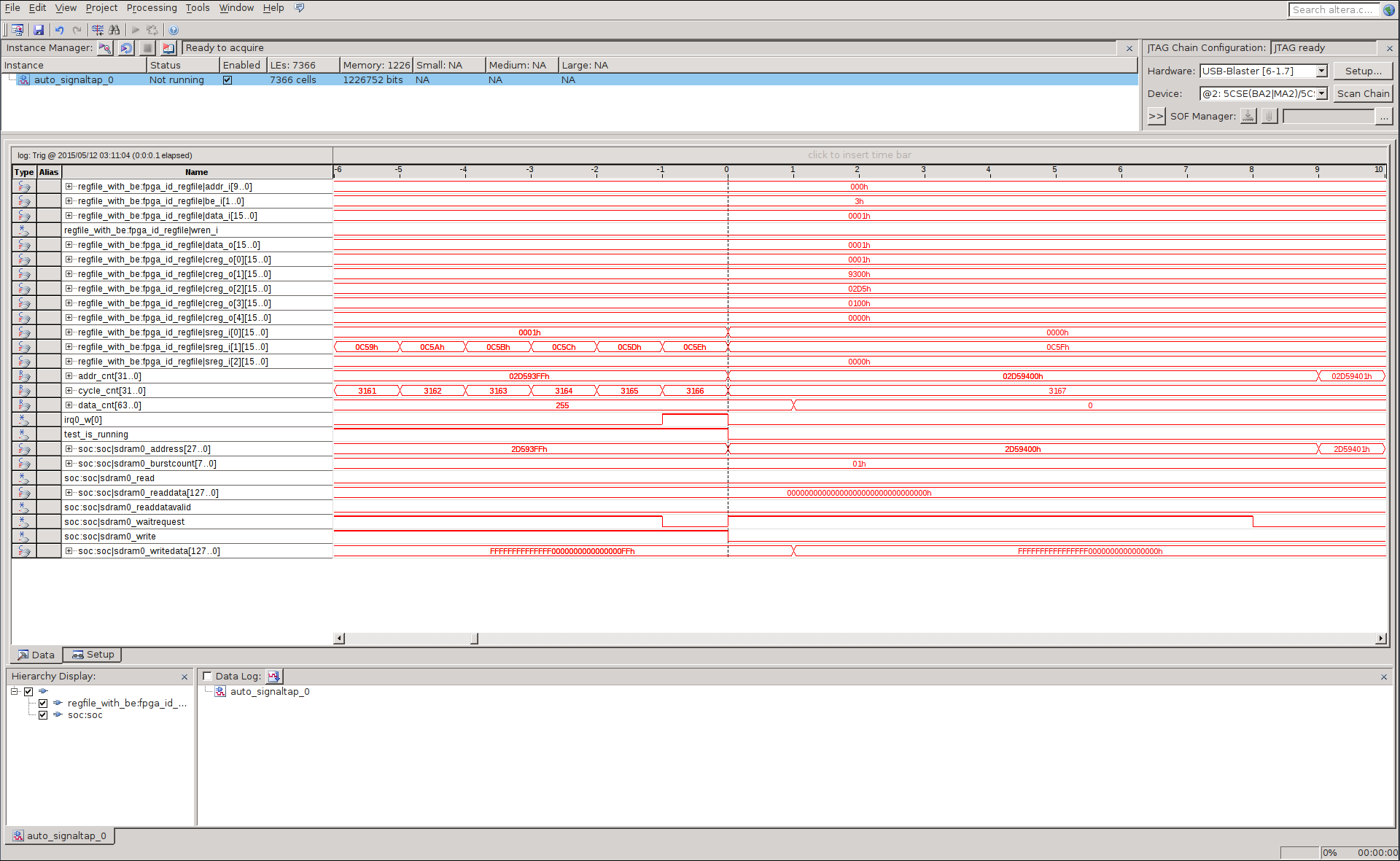

次に、 SignalTapを構成して、信号のネガティブエッジでtest_is_runningをキャプチャし、DMAコントローラーを実行します。

これを行うには、ゼロレジスタのゼロビットに書き込み、最初に0(存在しない場合)、次に1を書き込みます。同時に、 mem.oユーティリティはトランザクションを4バイト実行し、これらは2つのレジスタであることに注意してください。 したがって、注意しないと、隣接するレジスタのデータが上書きされます。

合計で、最初に0xC0000000のデータを読み取り、次にそれを書き留める必要がありますが、 ゼロビットが設定されています。

私たちは読みます:

./mem.o 0xC0000000

0x93000000を読み取りました

私たちは書きます:

./mem.o 0xC0000000 0x93000001

その後、 SignalTapで次のようなものを取得する必要があります。

SignalTapの結果

ご覧のとおり、トランザクションが終了した時点でのcycle_cntカウンターの値は3167です。

帯域幅を計算しましょう。 私のプロジェクトのクロック信号の周波数は150 MHzです(より広い範囲で周波数を変更できるようにするために、HPSシュレッドを使用せずにそこにインポートし、PLLから取得しました。これらの変更は簡単ですが、githubにはありません)。

幅-128ビット。 3167サイクル以上で256ワードが送信されました。 合計:

128 * 150 / (3167/256) = 1551 /c

更新:このような小さな帯域幅は、タイプミス、結論の詳細のために得られます。

データが正しく記録されたことを確認するために残っています。 Enterキーを押して、一時停止からphys_addrユーティリティを「削除」します。

次のテキストが表示されます。

Phys_addrの実行結果

0: 0x0 1: 0xffffffffffffffff 2: 0x1 3: 0xfffffffffffffffe ... 507: 0xffffffffffffff02 508: 0xfe 509: 0xffffffffffffff01 510: 0xff 511: 0xffffffffffffff00

あなたが見たなら、すべてがうまくいきました。

さまざまなパラメーターを試したところ、クロック周波数が帯域幅にほとんど影響を与えないことがわかりました。

25 MHzと150 MHzの両方でほぼ同じままです。

しかし、fpga2sdramインターフェイスの幅は、反対に、ほぼ線形の依存性を与えます-64ビットと128ビットでテストされました。256のためにチェックしませんでした。

当然、記録されたデータの量が少ない(4096バイトのみ)という事実により、測定誤差は非常に大きくなります。

独自のプリミティブドライバーを記述することで、DMAトランザクションのサイズを増やすことができます。

ドライバーのスペル

この記事は私が予想していたよりも少し多く出てきたので、このドライバーについて非常に簡単に話します。

さらに、次の記事で彼と協力する必要があります。

しかし、コードは興味のあるgithubにあります-詳細を見ることができます。

基本的な考え方は単純です-ドライバーを起動するときに、必要なトランザクションのサイズをパラメーターで設定します。

ドライバはメモリを割り当て、バスアドレスとトランザクションサイズをFPGAに書き込みます。

ドライバは、FPGAファームウェアで設定した割り込みハンドラも登録します。

その後、ドライバーは2つのcharデバイスを作成します。

- / dev / etn-ctrl -DMAトランザクションを開始します

- / dev / etn-data-データを取得します

ファイル/ dev / etn-ctrlから読み取ると、DMAトランザクションが開始されます。

その後、FPGAから割り込みが到着するまで呼び出しはブロックされます。

割り込みが到着すると、コールは終了します。これは、データが書き込まれ、ファイル/ dev / etn-dataから読み取ることができることを意味します。

ドライバーが.dtsファイルで機能するには、次の行を追加します。

.dtsの変更

fpga { compatible = "mtk,etn"; interrupts = <0x0 0x28 0x1>; };

最初の行は互換性のあるドライバーを指定し、2行目はFPGAからの割り込みの数とタイプを指定します。

4MBトランザクションを使用する場合、スループットは約

結論

FPGAでプリミティブDMAコントローラーを作成し、そのスループットを測定しました。

更新:

少量の帯域幅は、DDR3設定のタイプミスによるものです。

つまり、PLLシュレッドが実際の25 MHzではなく125 MHzに設定されたという事実です。

このため、PLLの乗数と除数の比率は正しく計算されませんでした。

その結果、DDR3は規定の333 MHzではなく66 MHzで動作しました。

正しい係数と256ビットのインターフェイス幅を使用すると、スループットは約16〜17 Gb / sになります。これは、幅が32ビットで周波数が333 MHzのDDR3インターフェイスの理論上のスループットに相当します。

次の記事で詳しく説明します。

もちろん、誰もが興味を持っている場合、記事の概要は次のとおりです。

- FPGA でのILI9341のフレームバッファ実装

- 作業SGDMAコントローラ

- SGDMAコントローラを使用したFPGAでのギガビット2ポートNICの実装

最後に達した人に感謝します! がんばって。