この投稿は、FPGAの設計者に、 Ahronix Speedster22iプラットフォームでPCIエクスプレスバスの使用を最小限の時間と労力で開始する方法を示すことを目的として書かれました。 この記事では、プロジェクトの組織について説明します。開発者の特定の要件への適応は、たった1時間でホストコンピューターのPCIeバスに接続できる、1つのモジュールのソーステキストの簡単な変更に限定されます。 他のプラットフォームの開発者もこの記事を興味深いものにすると思います。

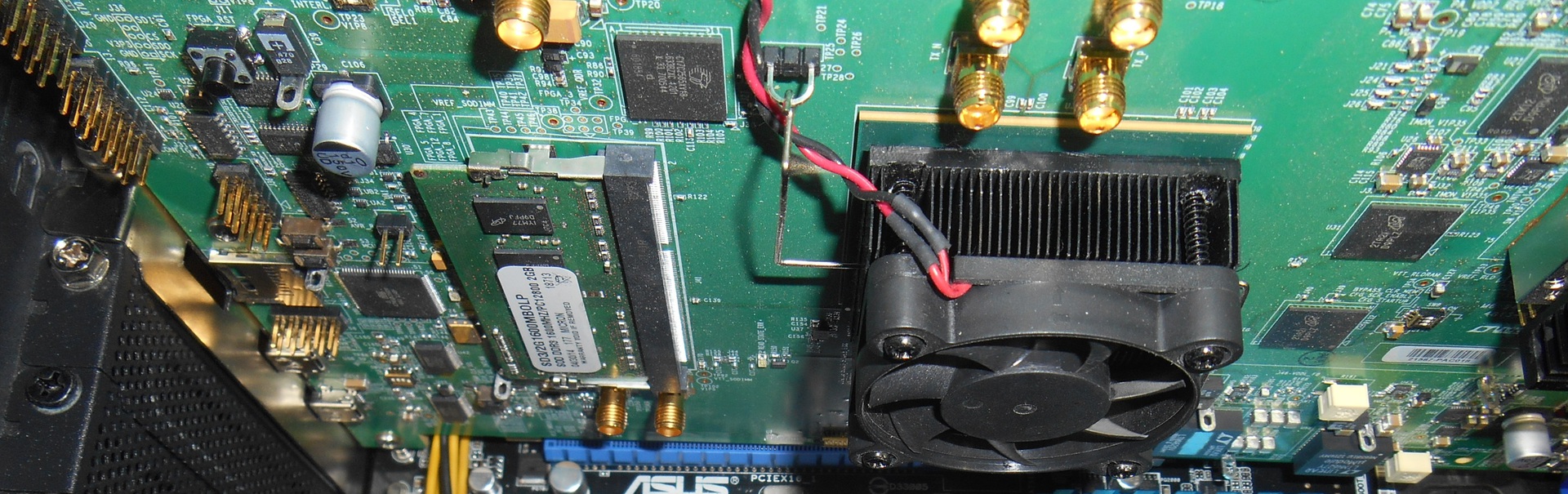

Speedster22i HD1000 FPGAには、 PCIe 3.0仕様用の2つのPCIe SIG認定PCIe SIGコアがあり、 Speedster22i HD1000開発キットデバッグカード(以前の記事で書いた)には、これらのコアの1つがPCIeスロットに接続されています 。 PCIeインターフェイスを介して、ホストコンピューターとデバッグボードと対話することは非常に便利です。 実際、これはこの目的のための唯一の高速ソリューションです。 PCIeを使用してデバッグボードをホストコンピューターに接続する代わりに、組み込みのcom-portがあります。これは数桁遅いです。 他のすべてのソリューションでは、多少のハードウェアの高度化が必要ですが、少なくとも信号レベルコンバーターの使用が必要になります。

Achronixには、 PCIeハードウェアコアのパフォーマンスを最大限に発揮するリファレンスデザインがあります。コアはターゲットモードで動作し、 CPUに直接アクセスし、 DMAメカニズムを介して読み取りおよび書き込みを行います。 すべて正常に動作することを確認しました。 しかし、この設計は、 Verilogコードの不十分なモジュール性と過度の複雑さのために、独自の目的のために修正するのが非常に難しいことが判明しました。 したがって、企業設計に基づいて、独自のバージョンを作成し、 DMAを介した交換に関連するすべてを削除し、変更されていないコードのモジュールおよびコードを適応させるために変更する必要のあるモジュールを明示的に選択するように構造化することが決定されました特定の開発者タスク。 その結果、シンプルで適切に構成されたプロジェクトが作成され、開発者の特定のタスクへの適応は、たった1つのモジュールのコードの単純な変更になります。

Achronix FPGAは 、 PCIe 、 DDR3、100 / 40 / 10Gイーサネット 、 Interlakenなどのインターフェイスのコントローラー用のハードウェアベースのIPコアを備えています。 これらのハードウェアコアは、これらのインターフェイスの機能に必要なすべてを提供します。開発者に必要なことは、これらのコントローラーで独自のインターフェイスモジュールを記述することだけです。 その結果、作業量が劇的に削減されます。 さらに、必要なタイミングの達成が大幅に簡素化されます。 PCIeデザインの場合、必要なインターフェイスモジュールはわずかで、そのほとんどは企業のリファレンスデザインから取得されました。

プロジェクトの簡単な説明

プロジェクトは、3つの128ビットレジスタへのアクセスを実装します。 PCIeコアは、BAR0-64KB、BAR1およびBAR2-8 KBの3つのBAR用に構成されています。 レジスタへのアクセスは、BAR1を介して行われます。 3つのBARが存在するのは、使用するドライバーとの互換性要件によるものです。 レジスタの説明を以下に示します。

| 名 | AP BAR1の変位 | タイプ | 説明 |

|---|---|---|---|

| R0 | 0 | RO | {4 {32'hDEADBEEF}} |

| R1 | 20時間 | Rw

Rw | ビット[7:0]-LEDラインへの出力

ビット[127:8]-使用されていません |

| R2 | 40時間 | RO

Rw | ビット[7:0]-スイッチの行の読み取り

ビット[127:8]-使用されていません |

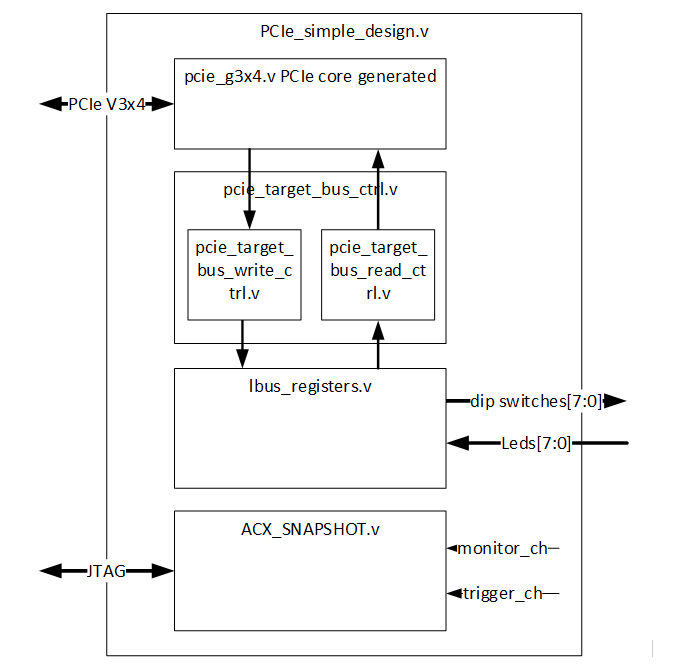

プロジェクトをアップグレードするとき、最初に行われたのは、 DMAを介したデータ交換に関連するコードを削除することでした。 その後、 target_readおよびtarget_write読み取りおよび書き込みチャネルを使用して、カーネルに接続しました。 次に、図に示すように、モジュール構造が定義されました。

合計で4つのモジュールが判明しました(サブモジュールを含むものもあります)

モジュールの構成:

- pcie_g3x4.v - PCIeハードウェアコアラッパー。 VendorID 、レーン数、ローカルバス幅などのパラメーターを決定します。このモジュールは、 ACE開発カーネルジェネレーターを使用して生成されます。

- pci_target_bus_ctrl.v-ハードウェアコアのターゲットチャネルと、 PCIバスを介してレジスタにアクセスできるローカルバスに一致するラッパーモジュール。 ターゲットチャネルは書き込みと読み取りの2つの独立したサブチャネルで構成されているため、このモジュールは2つのモジュールpci_target_bus_write_ctrl.vとpci_target_bus_read_ctrl.vを組み合わせており、それぞれ書き込み操作と読み取り操作を実装しています。

- lbus_registers.v-適切なユーザーレジスタを含むモジュール。 特定のプロジェクトのコード変更を必要とする唯一のモジュール。

- ACX_SNAPSHOT.v-インサーキットデバッグ用の補助モジュール。 デバッグの最後に、プロジェクトから除外できます。

このプロジェクトでは、開発者に必要な機能を実現するために、1つのモジュール( lbus_registers.v)のソースコードのみを変更する必要があります。 他のすべてのモジュールは、変更なしでそのまま使用されます。 同時に、 lbus_registers.vモジュールは、開発者に必要な機能が追加されるテンプレートとして使用できます。 したがって、 PCIeバス上の複数のレジスタを使用して動作するインターフェイスを取得するには、モジュールコードを追加するのに1時間もかかりません。

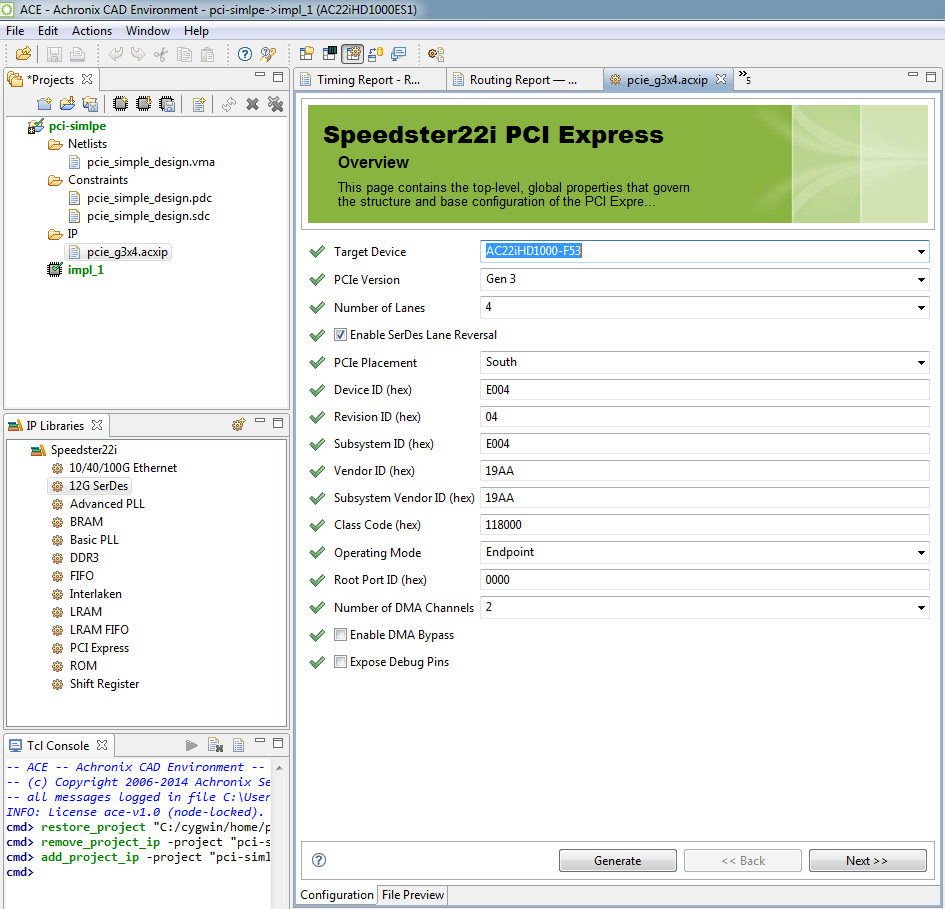

PCIeコア生成

カーネルを生成するには、ACEシェルコアジェネレーターを使用できます。 指定されたすべてのパラメーターは、拡張子が.axipのファイルに保存され、いつでも編集できます。 ジェネレーターの結果は、 VerilogおよびVHDL言語のテキストファイルです。 カーネル生成プロセスのスクリーンショットを図に示します:

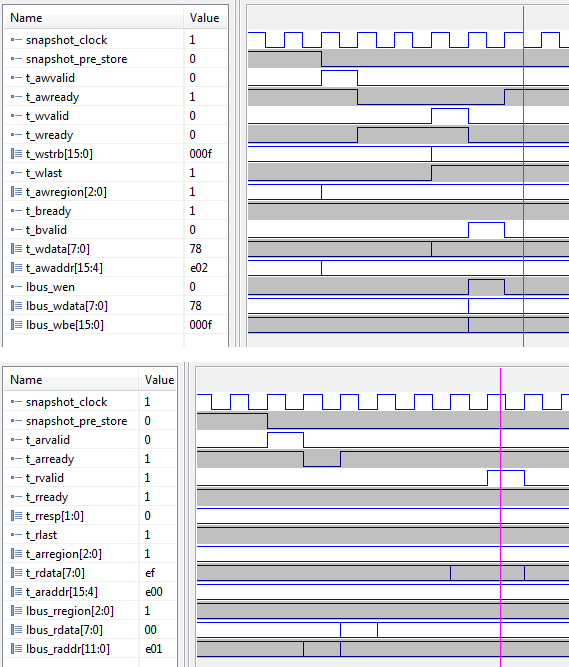

Pcieコアターゲットインターフェイス

PCIハードウェアコアにはいくつかのインターフェイスが含まれていますが、ターゲットインターフェイスに興味があります。 パッシブデバイスとして機能するレジスタはこのインターフェイスを介して接続され、プロセッサはアクティブデバイスとして機能します。 ターゲットインターフェイスは、書き込みアドレスの設定、データの書き込み、読み取りアドレスの設定、およびデータの読み取りの4つのチャネルで構成されます。 書き込みチャネルと読み取りチャネルは互いに独立して機能します。 以下は、書き込みおよび読み取りトランザクションのタイミング図です。 同じ図はローカルバス信号を示しています。

ローカルバス

ローカルバスの構造は非常にシンプルです。 書き込みと読み取りの2つの独立したチャネルで構成され、異なるワード幅に設定できます。 このプロジェクトでは、128ビット幅の単語を使用します。

lbus_registers.vモジュールに実装されたローカルバスインターフェイスは、遅延なしでレジスタに書き込み、1クロックサイクルの遅延で読み取りを提供します。 ただし、実際の遅延は次のようにわずかに大きくなります。 pci_target_bus_ctrl.vモジュールに含まれるサブモジュールは、書き込みおよび読み取りトランザクションのレイテンシに寄与します。

実装

プロジェクトの実装は、合成段階とトレース段階の2つの段階で構成されています。

ディレクトリ構造

次のディレクトリ組織が実装のために選択されました。

pci_simple

| --- src

| --- syn

| --- tr

| ---ツール

srcディレクトリには、 Verilogソースファイルが含まれています。 synディレクトリにはsynplifyプログラムを使用した合成に必要なファイルが含まれ、 trディレクトリにはトレースフェーズに必要なファイルが含まれています。 また、このディレクトリには、デフォルトで、生成されたカーネルがあります。 toolsディレクトリーには、ドライバーとPciExpressプログラムが含まれています。これらを使用して、 PCIeバスに接続されたレジスターに対してデータを読み書きできます。

合成

synディレクトリにはpcie_simple_design.prjプロジェクトファイルが含まれています 。 このファイルは、 Synopsysが開発したsynplify-pro合成プログラムで指定する必要があります。 このプログラムの結果は、 syn / rev_1サブディレクトリにあるpcie_simple_design.vmaファイルです。 このファイルは、次のステップ-トレースの入力です。 合成手順のスクリーンショットを以下に示します。

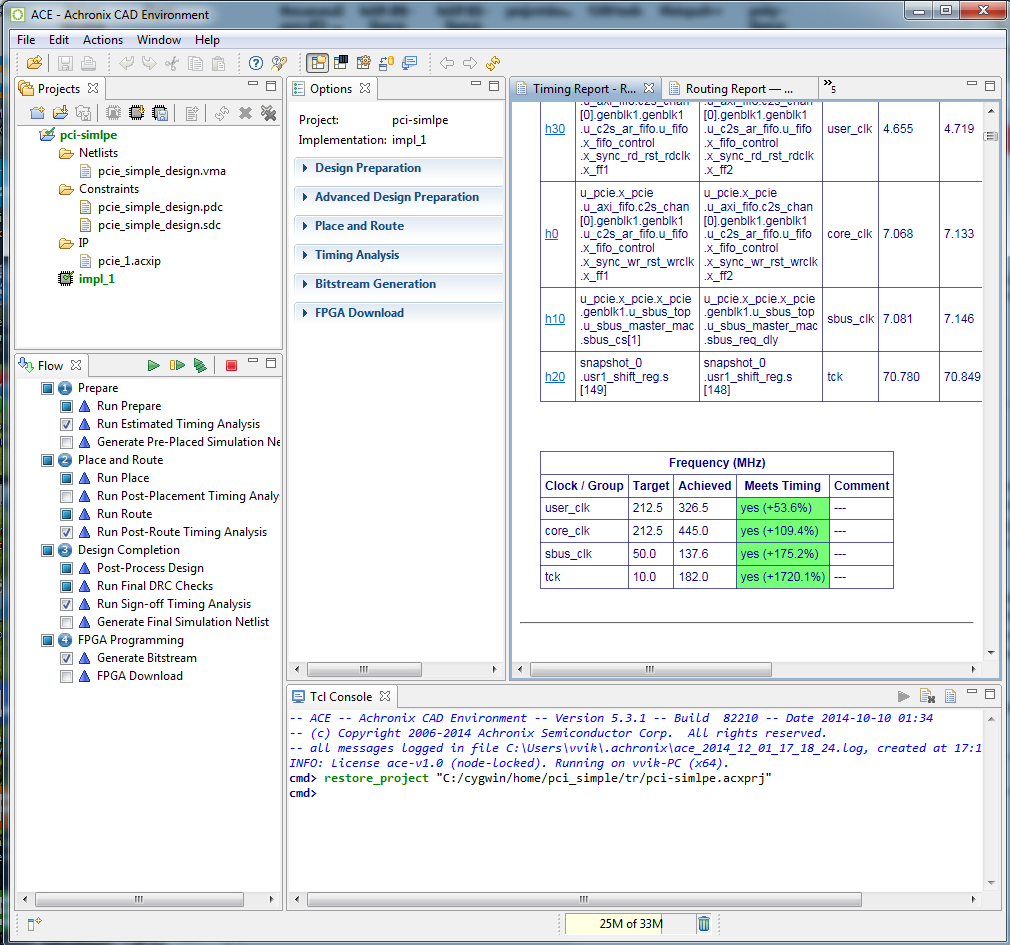

トレース

トレースフェーズは、 Achronix独自のACEプログラムによって実行されます。 trディレクトリにはpci-simple.prjプロジェクトファイルが含まれており、 ACEで指定する必要があります。 トレース手順の最後に、 pci-simple-design.jamファームウェアファイルがtr / impl_1 / output サブディレクトリに表示され、FPGAに直接ダウンロードされます。 トレースフェーズのスクリーンショット:

制約

constファイルは2つだけです。1つはクロック回路を記述し、もう1つは使用されるI / Oピンを定義します。 ファイルはtrディレクトリにあり、それぞれpcie_simple_design.sdcおよびpcie_simple_design.pdcという名前です。 それらは既にプロジェクトファイルを介して合成およびトレースプログラムに接続されています。

結果

タイミング

| トレース結果 | |||

|---|---|---|---|

| 周波数(MHz) | |||

| 時計/グループ | 対象 | 達成した | タイミングを満たします |

| user_clk | 212.5 | 308.5 | はい(+ 45.2%) |

| core_clk | 212.5 | 433.5 | はい(+ 104.0%) |

| sbus_clk | 50.0 | 138.7 | はい(+ 177.5%) |

| Tck | 10.0 | 175.4 | はい(+ 1653.6%) |

ユーザーレジスタが接続されているuser_clkクロックグループに興味があります。 ご覧のとおり、特定の周波数212.5 MHzで、結果は308.5 MHzでした。 必要以上に45%高い。

廃棄

| 資源 | 忙しい |

|---|---|

| RLB | 0.520% |

| LUT4サイト | 0.410% |

| DFFサイト | 0.520% |

| MUX2サイト | 0.010% |

| Aluサイト | 0.170% |

| LRAMサイト | 1.280% |

| BRAMサイト | 0.190% |

| BMULTサイト | 0.000% |

| I / Oパッドサイト | 1.980% |

| データパッド | 1.740% |

| クロックパッド | 12.50% |

| リセットパッド | 0.000% |

ホスト接続

ホストコンピューターに接続するには、ドライバーが必要です。 特定の条件下では、会社のリファレンスデザインのドライバーを使用できます。 PciExpress.exeアプリケーションはこのドライバーで動作し、 PCIeバスに接続されたレジスターにアクセスできます。 これらのツールを使用できるようにするには、元のデザインBARの構造を保持し、 VendorIDおよびDeviceIDパラメーターの値を保存する必要があります。

Windowsオペレーティングシステムを搭載したホストコンピューターでの作業を開始するには、次の手順を実行する必要があります。

- PCIeバスを介してデバッグボードをコンピューターに接続します。 PCIe x8以上のスロットが必要です。 帯電防止保護手段を遵守して、スイッチを切ったデバイスに接続する必要があります。 外部電源からデバッグボードに電力を供給します。

- コンピューターとボードの電源を入れます。 電源投入手順は重要ではありません。

- ファームウェアをFPGAにダウンロードします。

- デバイスマネージャーを使用して、 PCIバス上の新しいデバイスを見つけ、そのドライバーをインストールします。

- 再起動

- 再起動後、 PciExpressプログラムはレジスタの書き込み/読み取りができます。

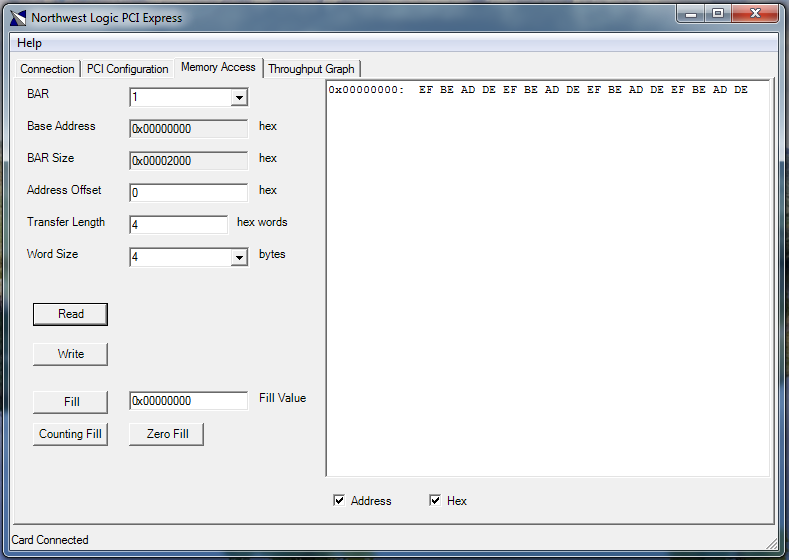

次の図は、アドレス空間BAR1のオフセット0でレジスタを読み取った結果を示しています。

lbus_registers.vモジュールのカスタマイズ

ソースコードを独自のプロジェクトで使用するには、開発者が必要なレジスタをデザインに入力する必要があります。 すべてのユーザーレジスタはlbus_registers.vモジュールにあり、それをカスタマイズする場合、次の簡単な手順が必要です。

- ユーザー登録ごとにコードを書く

- パラメータリストで各レジスタのアドレスを設定する

- 各レジスターのアドレスデコーダーコードを記述する

- 各レジスタを書き込みおよび読み取りバスに接続します

これらのアクションを実行する方法を示します。

•レジスタの名前とその長さを定義します。

reg [AXI_DATA_WIDTH-1:0] my_register;

•このレジスタの書き込みおよび読み取りストローブを定義します。

wire selw_my_register; wire selr_my_register;

•このレジスタに常時ブロックを書き込みます。 これは、 生成ステートメントを使用して簡単に実行できます。

最も単純な場合、コードは次のようになります。

genvar i; generate for (i = 0; i < AXI_BE_WIDTH; i = i + 1) begin: leds_lanes always @( posedge clk or negedge rst_n ) if (!rst_n) my_register [7+ 8*i: 8*i] <= 8'h0; else if (selw_my_register && lbus_wr_be[i] ) my_register[7+ 8*i: 8*i] <= lbus_wr_data[7+ 8*i: 8*i]; else my_register [7+ 8*i: 8*i] <= my_register [7+ 8*i: 8*i]; end endgenerate

個々のビットのより複雑な処理が必要な場合、always-blockは当然より複雑になり、生成演算子を使用せずに明示的にコードを記述しやすくなります。

•パラメーターのリストに行を追加します。

parameter ADDR_MY_REGISTER = 32'h1234_5678

、

ここで-32'h1234_5678の代わりに、必要なアドレス空間のバイト単位の実際のオフセットを示します

•レジスタ選択信号の式を作成します。

selw_my_register = reg_wr_hit & (lbus_wr_addr[REG_ADDR_WIDTH-1:0] == ADDR_MY_REGISTER [REG_ADDR_WIDTH+AXI_REMAIN_WIDTH-1:AXI_REMAIN_WIDTH]); selr_my_register = reg_rd_hit & (lbus_rd_addr[REG_ADDR_WIDTH-1:0] == ADDR_MY_REGISTER [REG_ADDR_WIDTH+AXI_REMAIN_WIDTH-1:AXI_REMAIN_WIDTH]);

•always_combブロック内

always_comb begin case (1'b1) … endcase end

caseステートメント内に新しいブランチを追加します。

selr_my_register: c_reg_rd_data = my_register;

ユーザー登録ごとに上記の手順を繰り返します。

モジュールインターフェース

モジュールインターフェイスは次のように定義されます。

module lbus_registers #( parameter BAR_NMB = 3'd0 parameter AXI_DATA_WIDTH = 128, parameter AXI_BE_WIDTH = AXI_DATA_WIDTH/8, // AXI Len Width parameter LBUS_ADDR_WIDTH = 12, // 64 KB expected for NWL Reference Design parameter REG_ADDR_WIDTH = LBUS_ADDR_WIDTH, // 64 KB expected for NWL Reference Design parameter ADDR_R0 = 32'h000_0000, parameter ADDR_R1 = 32'h000_0020, parameter ADDR_R2 = 32'h000_0040 ) ( input wire rst_n, input wire clk, // input wire [7:0] switches, output wire [AXI_DATA_WIDTH-1: 0] rg1_out, output wire [AXI_DATA_WIDTH-1: 0] rg2_out, output wire [71: 0] debug_bus, // Local Bus channel input wire [LBUS_ADDR_WIDTH-1:0] lbus_wr_addr, input wire [2:0] lbus_wr_region, input wire lbus_wr_en, input wire [AXI_BE_WIDTH-1:0] lbus_wr_be, input wire [AXI_DATA_WIDTH-1:0] lbus_wr_data, // input wire [LBUS_ADDR_WIDTH-1:0] lbus_rd_addr, input wire [2:0] lbus_rd_region, output wire [AXI_DATA_WIDTH-1:0] lbus_rd_data );

パラメータ設定

lbus_registers.vモジュールの設定は、表にリストされています。

| パラメータ名 | デフォルト値 | 値の範囲 | 説明 |

|---|---|---|---|

| BAR_NMB | 3'd0 | 3'd0-3'd7 | アドレスセレクターが構成されているBAR番号 |

| AXI_DATA_WIDTH | 128 | 128、256 | データバスサイズ |

| AXI_BE_WIDTH | AXI_DATA_WIDTH / 8 | - | 手動で変更しないでください |

| LBUS_ADDR_WIDTH | 12 | 8-15 | ローカルアドレスバスのビット数を設定します。 通常、最大のBARのAPのサイズに対応します |

| REG_ADDR_WIDTH | LBUS_ADDR_WIDTH | <= LBUS_ADDR_WIDTH | 選択したBARに対応するローカルアドレスバスAPのビット深度を設定します |

| ADDR_R0

ADDR_R1 ADDR_R2 | 32'h000_0000 | バーのサイズに依存 | レジスタアドレスR0(R1、R2)。 レジスタのアドレスは常にバイトで示され、BARのアドレス空間でのオフセットに対応します |

デバッグ

デバッグは内部シグナルアナライザーを使用して実行され、 ACX_SNAPSHOT.vモジュールがプロジェクトで使用されます。 このモジュールは、 「define USE_SNAPSHOT」条件付きコンパイルディレクティブによって接続されます 。 インサーキットデバッグを整理するためのドキュメントは、 Achronix WebサイトのSnapshot User Guide.pdfファイルにあります。

結論と結論

PCIエクスプレスバスへの接続などの困難なタスクでさえ、 Achronix Speedster22iプラットフォームで簡単に、そして最も重要なこととして、迅速に解決されます。 PCIeハードウェアコアに基づいた作業プロジェクトの作成は簡単ではありませんでしたが、非常に簡単です。

Achronix Speedster22i FPGAの他のハードウェアコアに関するストーリーは、マスターされ次第計画されています。 以降の投稿では、 DDR-3および100G Ehernetコアについて説明します。

参照資料

1. Achronixは、Speedster22i FPGAのPCI ExpressハードウェアコアがPCI-SIG仕様に準拠していることを発表しますwww.achronix.com/wp-content/uploads/pr/2014_May_PCI-SIG.pdf

2.デバッグボードHD1000開発キットの図(英語)22iHD1000_Development_Board_Schematic.pdf

3. Speedster22iでPCIeコントローラーを使用するためのガイド(英語) www.achronix.com/wp-content/uploads/docs/Speedster22i_PCIe_User_Guide_UG030.pdf

4.スナップショットユーザーガイド(英語) www.achronix.com/wp-content/uploads/docs/Speedster22i_Snapshot_User_Guide_UG016.pdf

5.オリジナルのリファレンスデザイン:Speedster22i_PCIe_Demo_Design.zip

6.記載されているプロジェクトのソースファイル: drive.google.com/file/d/0B9Gt8fTYH6s-VGhfbk5RQWM4bk0