あるタスクまたは別のタスクでFPGAを使用するかどうかは、誰もが自分で(または同僚と)決めます。

今日、FPGAでプリント回路基板を作成する機能に関する記事に注目したいと思います。 メンター・グラフィックスのIO Designerツールを基盤として使用します。

ある人はその資料を有用だと思うかもしれませんし、ある人は単におもしろいかもしれませんし、ある人は私に反対するかもしれません。

Altium Designerなどの一部のCADシステムでは、新しいチップをベースにしたアップデートが定期的にリリースされます。 (更新の購読者である場合)。 CadenceとOrCADの場合、コンポーネントメーカーは、多くの場合、回路シンボルと回路基板セルのライブラリシンボルをレイアウトします。 Mentor Graphics ExpeditionPCBにとって、この贅沢はルールというよりも例外です。 PADS(メンター・グラフィックスのプリント回路基板のエンドツーエンド設計用の別の製品)については、私はそれを扱う必要がなかったとは言いません。 設計システム自体では、非常に便利なライブラリコンポーネントマネージャー。 IPC-7351規格の要件に従ってプリント回路基板のコンポーネントフットプリントを構築するために、非常に成功したLP Wizzardプログラムがあります。 (ランドパターンウィザード)。 単純なコンポーネントではなく単純なコンポーネントのグラフィックダイアグラムシンボルを作成するには、ファイルからインポートする可能性があります。 また、FPGAには、プロジェクトのシンボル、回路、有料(プリント回路基板から)、およびVerilog(VHDL)部分を組み合わせた「IO Designer」があります。

IO Designerには、Xilinx、Altera、Lattice、AcctelなどのFPGAメーカーのほとんどのFPGAおよびCPLDに関するナレッジベースが含まれています。 FPGAメーカーからの新しいファミリのリリースに加えて、MGはFPGAデータベースのアップデートをリリースしています。 しかし、チップファミリに関する新しいドキュメントはまだ検討する必要があります。

FPGAを選択し、その機能を研究(知り合い)し、作成する準備ができたとします。

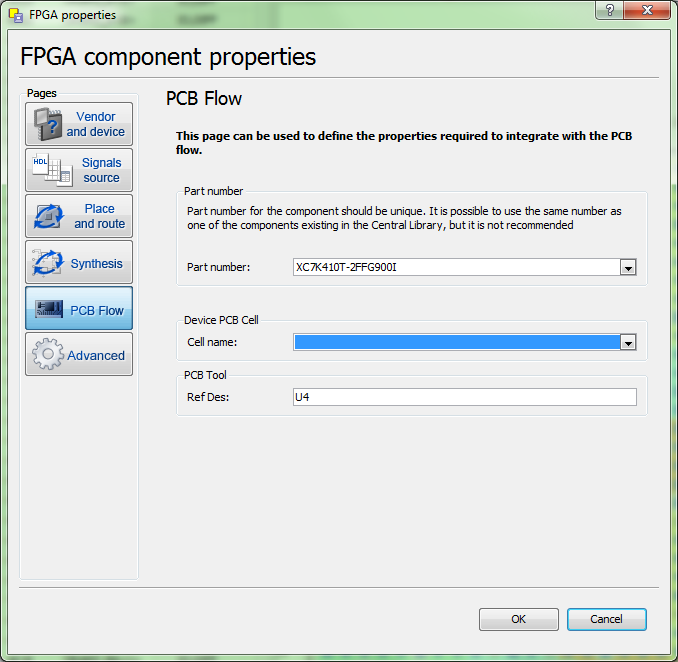

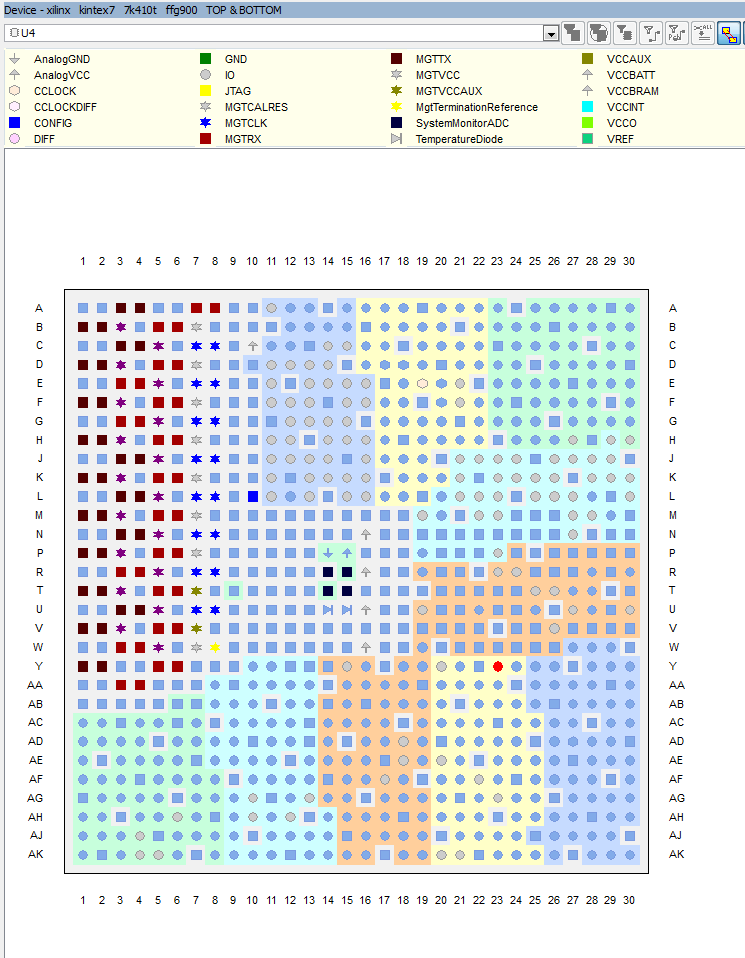

プロジェクトを作成するとき、FPGAのメーカー、FPGAファミリ、ケースのタイプ、および要素の数を選択できます。 また、コンポーネントの速度も示します(正確な部品番号を設定するため)。

FPGAの場合、ほとんどの接点は出力と入力の両方に構成できます。 一目で接続-私はしたくない。 ここでは、コントローラーSDカード、ここではイーサネットPHY用のRGMIIなどを用意しています。 連絡先をこのように大胆にバイパスすることで、多くの落とし穴を見つけることができます。 ドキュメントを読むことでそれらのほとんどを回避できますが、これから連絡先を割り当てるのは簡単ではありません。 そして、ボード設計は混乱に変わる可能性があります。

このイメージのすべてがそれほど悪くないのは、よく開発されたプロジェクトに基づいて「人工的に」作成されたためです。 通常、初めてのことはそれほどスムーズではありません。 また、FPGAを追加する段階では、まだすべての要素がボードに配置されているわけではありません。 ただし、左下のコネクタからの信号はFPGAの最下部に到達しないことに特に注意してください。 その結果、他の信号と交差し、トレース中に追加のビアとボードの追加レイヤーの両方が必要になる場合があります。 最終的には生産コストが増加します。

連絡先を設定するためのオプションも非常に限られています。 ボードが特定の製品用に作成されていると便利です。 隣接する要素には結論があり、FPGAでそれらの応答バス/信号を作成します。 FPGA向けCADのトライアルプロジェクトを開始しました。 すべてが成功したら、トレースに渡すことができます。

デロゲーションとして:Xilinx Spartan-6のEMNIPにはDDRメモリ用のピンが特別に割り当てられていたため、マイクロ回路がボードに正しく配置されたときに便利にトレースされました。 そして、場所を変えるためにそれらを移動する必要はありませんでした。

多くの場合、技術的な要件に従って、ある種の普遍性をもたらす必要があり、当社のボードは将来いくつかのプロジェクトに使用されます。 これが、他の多くのデバイスと連携するプロセッサを備えた中央ボード、FPGAを備えた一種のデバッグボード、「独自の」プロセッサおよびOSを設計する方法です。 同期のため、またはPLLから信号を出力するためにコネクタに1つの接点が必要な場合は、そのままにしておきます。 バス上の信号の方向(入力、出力、または双方向)を決定します。 中央ボードが常にマスターである場合、アドレスバスまたは制御へのそのような信号は出力に対してのみ行うことができます。

WAITやBUSYなどのスレーブボードからバスに応答がある場合、マスターボードではそれらを入力にしかできないピンに割り当てることができます。 また、取締役会の存在を決定する結論を出すこともできます。

そのような目的は、一見したところ、その後の信号の追跡およびシャッフルの可能性を制限します。 しかし、実践が示すように、事前にそのような制限を知っておいたほうがよいでしょう。 また、すべての信号に「Inout」を割り当てるだけではありません。

信号のリストを取得する場所からファイルを選択できます。 これは、テストプロジェクト、VerilogまたはVHDLのファイルにすることができます。

テストプロジェクトがまだ行われていない場合、そのようなファイルを指定しない場合があります。 そして、プログラムウィンドウで信号を作成します。 デフォルトの信号のタイプ。 単一信号用および差動用。

次に、連絡先の場所を含むファイルをアップロードする場所を指定できます。

次に、回路をどのように使用するか、本格的なシンボルが必要か、回路設計で回路を作成するかを決定する必要があります。すべての接点の説明は、CAD FPGAとの交換ファイルの形式でのみ送信されます。

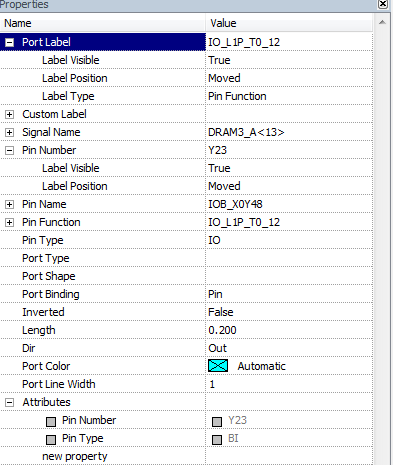

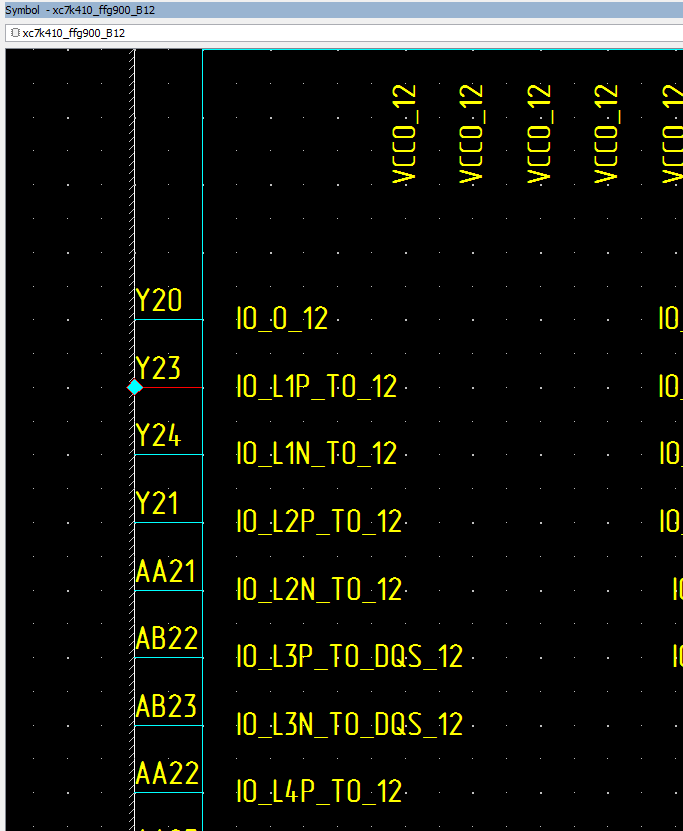

回路要素を作成する必要がなく、すべての交換が内部の未知のパスを経由する場合、私は常にこのオプションが好きでした。 しかし、チームで働くには、ゲームのより一般的なルールを受け入れる必要があります。 したがって、回路を設計するための企業標準に従って、シンボルをバンクに分割し、構成回路、土地、電源などを個別に取り出す必要がありました。 この部門には長所がありますが、欠点もあります。 回路図記号を作成する必要がありました。 484接点のFPGAの場合、誰かに思われるかもしれませんが、回路シンボルを正しく作成することはそれほど難しくありません。 しかし、1172接点を持つチップの場合、この職業は非常に疲れる。 ほとんどの連絡先の名前は長くて類似した名前を持ち、簡単に混同されます。 すべての文字を自動的に生成できます。 しかし、それらは「企業」の好みと一致しません。 IODでは、連絡先リストウィンドウからシンボルウィンドウにドラッグするだけで、要素のデータベースからシンボルを簡単に作成できます。 Farm Frenzyをプレイするのと同じくらい簡単だとは言えませんが、この時点で、マウスでチップの接触に信号を割り当てることができます。 この場合、名前、機能、連絡先番号、または独自の方法で指定する方法を指定できます。 私は通常、機能的な目的のためにディスプレイを選択します。 私の意見では、そのような名前はより有益であり、ダイアグラムはここで得られる信号の種類を示しています。

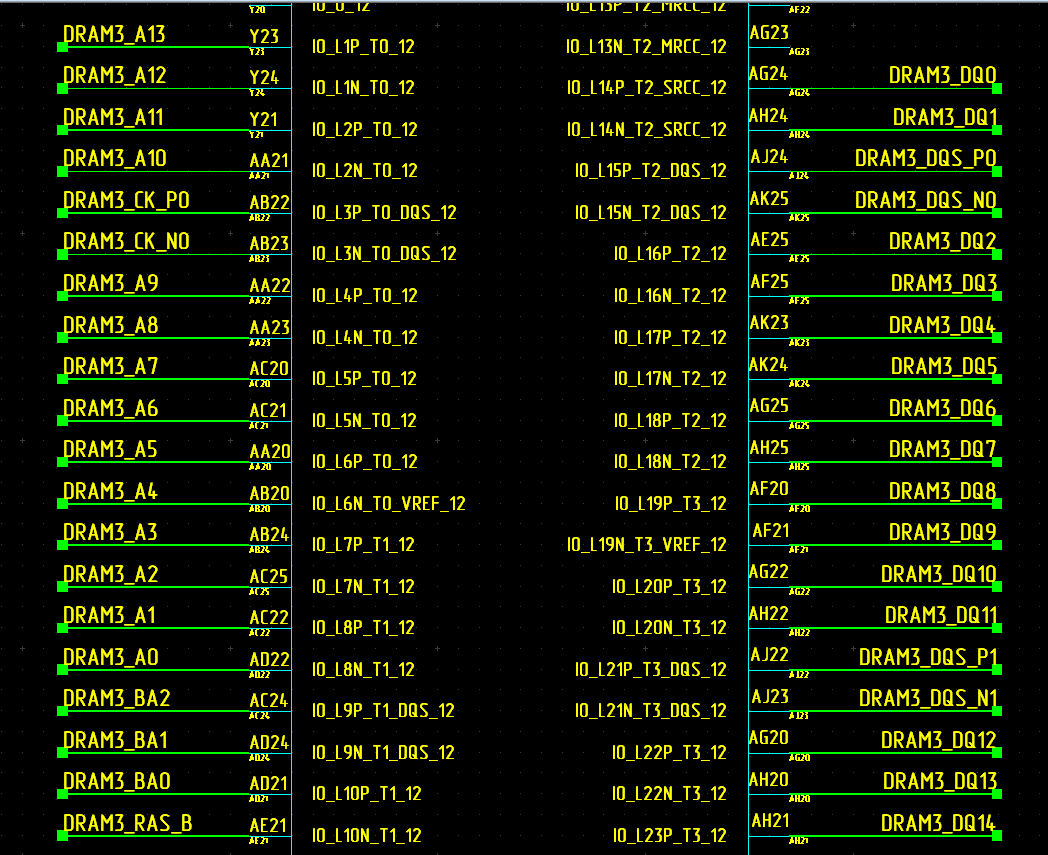

観察から、ザイリンクスの姓(第6および第7シリーズのファミリ)はかなり穏やかで有益であることがわかります。

IO_L6N_T0_VREF_13

IO-入出力接点

L6N-差動ペアの指定

T0-内部でメモリのデータ信号を交換できるバイトの指定(この点を明確にする必要があります!)

VREF-バンク用に選択した信号の規格で必要とされ、FPGA内に接続する方法がない場合、ここで外部基準電圧を適用できます。

13-銀行番号。

また、アルテラは通常の機能指定に出くわすこともありますが、多くの場合(私の主観的な意見)連絡先の名前を再現することは難しく、回路のシートに収まりません。 おそらく、大量のメモリ、乗算器、またはある種のコライダーを使用して回路を作成する場合、そのような名前は私にとって有用でしょう。

IO_DIFFIO_T18p__DATA15_DQ3T0_X9__DQ3T9_X18_DQ5T27_X36

この場合、連絡先名にカスタムラベルを指定すると役立ちます。 必要な名前を手で入力します。 私は通常、機能をコピーし、それを短くします

IO_T18p_DATA15_DQ

この場合

IO-入力/出力信号に使用できます

T18pは上部セグメントの差動ペアの数です

DATA15-この連絡先は、並列構成の読み込みに使用できます

DQ-これは連絡先の機能的な目的からの削減であることを教えてくれます(まだDMとDQSがある可能性があります)

これは、その機能に基づいて連絡先を呼び出す方法の1つの例であり、特定のプロジェクトでは、他の機能が最初に表示されます。

したがって、たとえば、アルテラでは、LVDS信号を使用する場合、外部負荷を使用する必要があります。 一部のバンクでは、これは受信側のみの負荷抵抗であり、他のバンクでは出力でも必要です。 これは、カスタムラベルプロパティのチャートシンボルで確認できます。 PCIタイプの信号についても同じことが言えます。 すべてのバンクに3.3V-PCIバス標準を割り当てることができるわけではありません。 また、これはシンボルにも記載されています。 デスクトップシステムのPCIe規格で混雑しつつありますが、工業デザインでは依然として人気があります。 また、このバージョンのデバイスを探しているお客様もいます。

すべての連絡先のシンボルに碑文を一度に追加できます。 これにより、キャラクター内のテキストの量が減ります。 追加情報があるとシンボルと回路が過負荷になるため、妥協が必要です。 ザイリンクスのマイクロサーキットでこれを行いました。これは、同じケース内の異なる数のロジックエレメントを持つコンタクトと互換性のあるマイクロサーキットを備えていますが、一部のコンタクトは「小さな」マイクロサーキットに関与しません。 その後、回路の一部はプロジェクトではんだ付けされず、より「軽い」マイクロ回路を設置することができました。 連絡先を配布するときにこれを考えると、不足しているコンポーネントとFPGAの価格を節約できます。

便宜上、缶詰のシンボルを作成します。 構成連絡先については、例外を作成できます。 プロジェクトに複雑な同期構造がある場合、CLK入力を別のシンボル(ローカル、グローバル、その他)に収集できます。 VCCOバンクの電源コンタクトは、メイン開発者の要求に応じて、シンボルと共にバンクと一緒に配置されるか、別のバンクに配置されます。

コア、VCCAUX、アースなどの電源接点は、ほとんどの場合、別々のキャラクターの上に立ちます。

伝えられるところでは、今では、すべての電源接点に回路のみを作成し、多数の同様の接点で回路を乱雑にしないことが可能です。 私たちがこれを行うのは慣習ではないので、私はそのようなオプションに精通していません。 これは、リファレンスドキュメント、またはメンターグラフィックスとその代表者のサイトのネットワーク上のウェビナーとトレーニング資料から入手できます。

作成したシンボルを直接回路設計に転送し、エンクロージャーのタイプを示し、回路に注釈を付けて、マイクロ回路を回路、回路、およびIODesignerに接続します。

信号の作成と割り当て

上記のように、信号をファイルからエクスポートしたり、自分で作成したりできます。

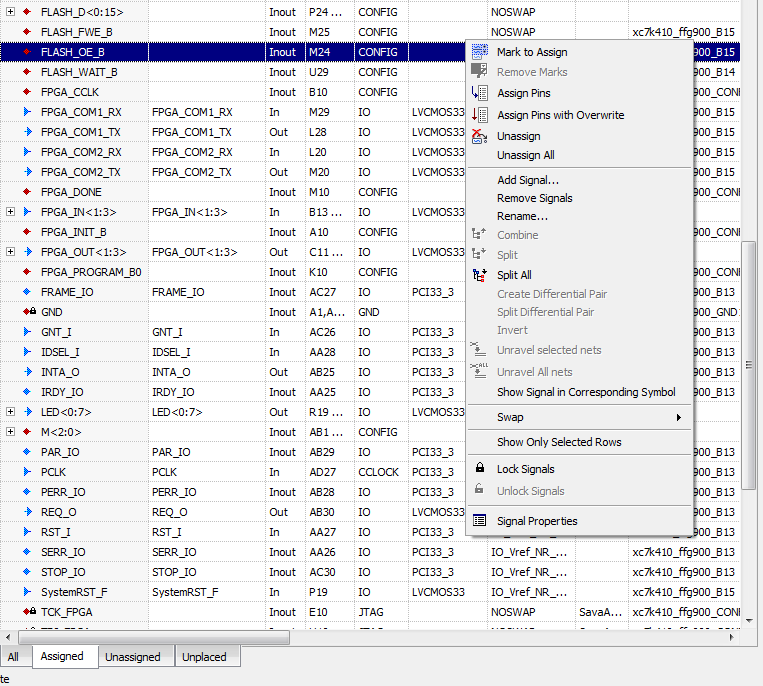

マウスとインポート/エクスポートの両方で信号を割り当てることができます。 SHIFT、CTRL、またはALTキーを押すと、既に割り当てられている連絡先に信号を再割り当てできます。 または、選択したすべての信号を1つのバンクに割り当てます。 視覚的に、銀行は異なる色で表示されます。 さまざまな種類の連絡先がさまざまなアイコンで表示されます。 差動ペアの表示を有効にできます。 時間が経つにつれて、ビジー信号はシェーディングされます。

回路を更新し、回路上の信号ですでにシンボルを確認します。

ボード上での接続方法を確認します。 通常、これはすでに上に示したおridgeです。

信号の簡単なリストをすぐに作成して、システムで自動的に作成されることがあります。その後、回路エディターの他の要素にドラッグします。

回路から信号のリストをインポートするオプションがあります。

回路、ボード、およびIO Designerの設計を同期することにより、IO Designerウィンドウで信号の表示を呼び出すことができます。 FPGAからそれに接続されたコンポーネントまでの回路を使用します。

これで信号をとかすことができます。 さらに、これらはすべて、当社が導入した規則に従って自動的に行われます。 設定信号はどこにも行きません。 信号を事前にロックして、位置の変更を防ぐこともできます。

信号DRAM3_RESET_Bは、入力/出力標準LVCMOS_1.35Vに割り当てる必要があり、標準のSSTL信号と同じバンクに配置できないため、バンク17に割り当てられ、他のすべてのDRAM3 *信号はバンク12に割り当てられます。 LVCMOS_1.35Vの4つの信号のみが標準LVCMOS1.8Vに割り当てられ、レベルコンバーターがインストールされています。

信号は明らかに複雑ですが、割り当てられたルールに従ってまっすぐになります。 Quartusのプロジェクトで作業しやすいように。

この画像は、分離されたコンポーネントと、FPGAからコンポーネントに向かって伸びる線を示しています。 場合によっては、すべてのコンポーネントが配置されていない場合、トラブルのないトレースの最初の試行ですべての連絡先を分解できないことがあります。 すべてはタスクに依存しますが。

このようなコンタクトの配布後、回路をすでに最終トレースに渡すか、自分でトレースすることができます。

Verilog / VHDLファイルにエクスポートすることもできます。 * .ucf、* .pinまたは別のファイルにエクスポートできます。 パイロットプロジェクトのFPGA設計者に渡してください。突然、何も考慮されませんでした。 しかし、小さなチームでは、他のプロジェクトの負荷が大きいため、これをすぐに実行できるとは限りません。 (古い改良、顧客の新しい願い、または並行プロジェクト)。

制限事項

この方法には制限があり、それを回避する方法が必ずしもわからない。 しかし、基本的には、汎用性と予備力のために多くのことを行う必要性と関係しています。 松葉杖などを発明しなければなりません。 そのため、デフォルトでは、アルテラは差動信号の隣に差動信号を配置できません。 コンパイラーは警告を出します。 Pin Planner QuartusでパラメーターSLEW_RATE = 0 MHzを設定することで回避できます。 その後、コンパイルは正常に完了します。 実際には、信号は20 MHzの周波数でハングします。 IODesignerにはそのようなパラメーターはありません。 その結果、回路では、これらの接点が最後に使用されるか、信号タイプを設定して、たとえばPCB信号や構成信号などの競合が発生しないようにします。

通常バイパスされる他の制限があります。 しかし、一般に、完成したボードが届くよりもはるかに早くマイクロチップのドキュメントをもう一度見直すので、私は彼らに対して前向きな姿勢を持っています。

他の設計システムで働いている人にとって、いくつかのことは明らかではないようで、必要ではないかもしれません。 したがって、私が知る限り(聞いた)、Altiumでは、プロジェクトをFPGA向けにコンパイルし、プロジェクトを回路とボードで直接構成できます。 すべての機能を認識しているわけではありません。 また、設計者にとっては、QuartusやISEにインポートする必要はありません。 しかし、1人の人が回路基板プロジェクトを行い、他の人がFPGAプロジェクトを行っています。 トレース用の回路を提供するとき、PCB設計者に接点を変更するためのアクションの自由を与えながら、信号を可能な限り正確に記述しようとします。 蓄積する警告はすべて同意します。

最後に、「IO Designer」は万能薬ではないと言いたいです。 回路、ボード、FPGAプロジェクトの設計をインタラクティブなゲームに変えたり、超小型回路のドキュメントを勉強することを免除しません。 しかし、このようなツールを使用する方がはるかに優れています。 この記事では、その利点のすべてを説明しているわけではありません。 また、一部のアルテラおよびザイリンクスファミリと連携するだけで済むため、すべてのマイクロ回路のライブラリの完全性を判断することはできません。 Cラティス、なんとかしてデバッグキットで少し作業できましたが、回路には届かず、ボードにも届きませんでした。 アクテルとはまったく仕事をしませんでした。 ザイリンクスに関するコメントから、私のバージョンでは、Vivadoとの間で制限ファイルを直接転送することはできません。 たぶんそれはアップデートで出てくるでしょう。 しかし、私はザイリンクスFPGAプロジェクトを実施していないため、問題が何であるかを正確に理解していませんでした。 * .csvファイルでエクスポートすることができました。

この出版物はIODesignerの教科書のタイトルであるとは主張していません。このためにMentor Graphicsから多くの教訓があります。 Megratek社がロシア語でトレーニングを行っていることを知っています。 www.megratec.ru 。

また、私が知る限り、メンター・グラフィックスは新しいバージョンの設計システムであるxPeditionの立ち上げを準備しています。 IODesignerによって具体的に何が追加されますか?時間はわかります。 私が見たプレゼンテーションのうち、ボードの3Dディスプレイを更新し、1つのプロジェクトで複数のボードを使用してデバイスを設計したことに感銘を受けました。

また、私が呼んだCADシステムに加えて、プリント回路基板用の他のものがあります。 それぞれに利点のリストと「XのようにYに欠けているもの」のリストがあります。 そして、IODを介して作業するオプションと比較して、それらの利点に名前を付けなかった場合、気を悪くしないでください。 これについてはコメントに書くことができます。 または、CADでFPGAを設計する方法に関する記事。