石から蒸気を作る方法、私たちの医者ガスパーは知っています

MKを選択する場合、特定のタスク用の特定の周辺デバイスのセットの構成に存在することに注意を払うことが非常に頻繁に必要です。 一方、すでに使用されているMKで使用可能な他のインターフェイスに基づいて、多くの標準バスを実装できます。 この投稿では、1986VIE1T MKには存在しない既存のSSPインターフェイスに基づいたハードウェア1-Wireインターフェイスの使用方法を示します。この経験は、同じアーキテクチャの他のメーカーの他のMKに転送できます。

まず、使用するマイクロコントローラーの簡単な説明。 Milander製のMK 1986BE1Tは非常に優れたデバイスであり、その利点は国産品であるという事実に限定されません(ただし、このパラメーターは著者にとって決定的でした)。 実際、最大140 MHzのクロック周波数を備えたCortex-M1コアを備えたMCはまれな市場参加者であり、多数のさまざまなインターフェイスの存在、拡張された温度範囲、およびVPを備えたバージョンの可用性を考えると、このMKはほぼユニークなオファーになります。 同時に、このMKの広範な使用に対する魅力を低下させるいくつかの特性に注意する必要があります。つまり、主に金属セラミックケースによって決定される高価格(開発者はプラスチックケースで比較的安価なバージョンを発表しましたが)、セラミック金属ケースは使用するのが非常に不便です(ただし、このタイプの住宅は、「正直な」軍事温度範囲を可能にし、(著者の意見では)不十分なレベルの文書作成(すべての国内問題の問題)を可能にします それにもかかわらず、正当化しないOtok、)。

このMKの主な特徴を説明します。

CORTEX-M1コア(わずかな制限付き);

クロック周波数-最大144 MHz(25 MHzを超える周波数の場合、プログラムメモリの読み取り時に遅延が発生し、実際の速度が100 MHzと同等に低下します)。

プログラムメモリ-128 Kb、データメモリ-48 Kb;

両方のタイプのメモリは、外部システムバスの組み込み32ビットコントローラーを介して簡単に拡張可能です(かなりの数の外部ピンが必要です)。

2つの内部発振器(あまり正確ではない)、外部水晶振動子と内蔵PLLを接続する機能を備えたクロックシステムを開発しました。

不揮発性メモリ(12 * 4バイト)およびリアルタイムクロック(外部バッテリー電源付き);

8 * 12ビットADC、2 * 12ビットDAC、PWMモードの8つのタイマー。

32xチャネルRAP;

適切な周辺機器の豊富なセット-2 * CAN、GOST 18977、2 * GOST R-52070、Ethernet 10/100(ビルトインPHY!)、USBホスト/デバイス、2 * UART(ビルトインIRDA)、3 * SSP。

最大96のユーザー設定可能なレッグ。

一般的なプログラミング環境(作成者はIARを好む)からSWDおよびJTAGを介してプログラミングおよびデバッグする機能。

一般に、水晶はかなりまともです。詳細については、製造元のWebサイトを参照してください。 機器の欠点の中で、著者は外部イベント用の未開発の割り込み装置に注意します(外部割り込みは事前定義された少数の結論にしか到達できません)。これは開発者の能力を制限します。

この記事のもう1つの「ヒーロー」は、1-Wireインターフェースです。 インターフェイスは標準化されておらず、ダラスセミコンダクターの所有物であり、広く知られています。低速デバイスとのやり取りに使用されます.i-Button識別キーとさまざまな温度センサーは特に知られており、バストポロジは個別のアドレス指定を備えたスターであり、交換レートは最大15 Kbpsです。ワイヤの数-2、より詳細な仕様は会社のウェブサイトで入手できます。 多くのマイクロコントローラにはこのインターフェイスのハードウェア実装がありますが、問題のMKはそれらに適用されません。 したがって、標準の周辺機器MK 986BEを使用してインターフェイスを実装する可能性を検討します。

まず、OSIモデルのレイヤー1(物理インターフェース)の実装が必要です。 この観点から、インターフェースは完全に単純です-アース線と1本の線が必要です。これにより、デバイスの双方向の相互作用が実行され、オプションで端末装置に電力が転送されます。 データワイヤを実装するには、オープンコレクタを備えたMK出力と、公称値5コムのプルアップ抵抗が必要です。 使用されるMKのすべての出力は構成可能であり、ビルトインプルアップおよびダウン抵抗を装備できます(詳細については、MKの説明を参照してください)。 内蔵抵抗器の値は必要なものとは異なります(噂によれば、それらは約10コムです-文書によると文書化されていないので、噂によると)、しかし、情報源が1つの場合、内蔵抵抗器を使用し、必要に応じて、外部抵抗器を追加することができます適切な栄養。 MK端子の許容可能な構成には、インターフェイス要件を満たすオープンドレイン出力モードもあります。 したがって、インターフェイスの物理的な実装の根本的な不可能性は見つかりませんでした。

マスターとスレーブの相互作用では、アクティブなゼロレベルが使用され、さまざまな持続時間のパルスの形で供給されます。 3つの主要なパルス幅が使用されます。

少なくとも480マイクロ秒の持続時間を持つリセットパルス、1から15マイクロ秒の持続時間の単位の送信パルス(読み取りを同期するために同じパルスが使用される)、15から60マイクロ秒の持続時間のゼロ送信パルス。 パルス間の保護間隔は少なくとも1μsである必要があり、保護間隔のあるパルス持続時間は60〜120μsである必要があります。 ここで、干渉を無視するという観点から最小期間の要件が明確な場合、上からのビット間隔の制限はそれほど明白ではなく、デバイスのロジックによって決定されないことに注意してください。 それにもかかわらず、制限は明確に述べられており、それに応じて尊重されなければなりません。 スレーブがマスターと対話するとき、2種類のパルスが使用されます。つまり、15から60μsの期間と60から240μsの期間の後者の終了に関連する遅延を伴うリセットパルスに応答するゼロの形の存在パルス、および応答で発行されるゼロ送信パルス最後の開始から1マイクロ秒以下の遅延で、15から60マイクロ秒の期間の読み取りパルス(インターフェイスのドキュメントでは、正確に15マイクロ秒の要件が確立され、その後に0から45マイクロ秒のパルスを削除するための遅延があります-奇妙な ATO 1回)を書きました。 上記からの一般的な結論は、1-Wireインターフェースの実装のために、上下からの制限で約10μsの精度で時間間隔を維持する必要があるということです。

このプロトコルの明白な実装は、出力ポートの直接制御に基づいており、オープンソースモードで構成され、プルアップ抵抗によって接続されています。 たとえば、プレゼンスパルスの存在を伴うリセットパルスの実装は、次の擬似コードで表すことができます。

( 0), 500 , ( 1), 15 : 0 – - (), 45 : 0 – :: - ( ), :: 60 : 1- - ( ), 180 : 1- :: - ( ), :: - .

実際、この手順でさえ、インパルスノイズの影響を排除するのはより難しいはずですが、この記事の目的のために、いくつかの単純化が許容されます。

残りのパルスについても同様の手順を実行できます。 次に、このオプションの短所を検討します。

遅延のソフトウェア実装の欠点は、取得された時間間隔がMKクロック周波数と個々のコマンドの実行時間に依存することであり、プログラムメモリの読み取りに遅延が導入されると、後者はほとんど無期限になります)

そして、微調整で最初の欠点を克服したとしても、RTOSのフレームワーク内で他のモジュールと一緒に機能する条件下で、または中断が存在する場合(そして、ほとんど常にそうであるように、真空で球形プログラムを書いていない)、得られる時間間隔ははるかに長くなる可能性があります(しかし予想以上に短くなりません。

インターフェースは非常に時間依存であり、必要な精度は重要です-高速MKでも10マイクロ秒はそれほど多くないため、1-Wireバス上のデバイスと通信しようとすると混chaとした障害を受け取る可能性が高くなります。 高レベルのプロトコルはコーディングの冗長性によるこのような障害を検出できますが、同様の実装方法を推奨することはできません。 このようなエラーに対処するには、クリティカルセクション(および上記のアルゴリズムではすべての操作)内で、割り込みを禁止し、タスクを十分に長い時間切り替えられる機能をブロックする必要があります。これは良いプログラミングスタイルではありません。

この実装のバリエーションは、汎用タイマーの1つまたはシステムタイマーを使用して必要な時間間隔を形成することです。 オーバーヘッドコストの遅延を考慮すると、タイミングチャートを非常に正確に維持し、上記の実装の最初の欠点を取り除くことができます。 それにもかかわらず、すべてのRTOS(または中断の存在下)で、指定された時間までに順序付けられたイベントが発生しないことのみを保証することはできますが、上記の制限は不可能であるため、2番目の欠点は、決定の枠組み内で根本的に取り返しのつかないものです。

したがって、1-Wireインタフェースの実装には、上下から厳密に制限された時間間隔を発行する機能と、正確に指定された時間間隔でMK端末の状態を監視する機能が必要です。 MKには、開発されたタイマー(ハードウェアステートマシンを含む)でそのような機会がありますが、検討中のMKはそれらの1つではありません。 また、ハードウェアで実装されたシリアルインターフェイスを使用することもできます。 MKには多数のシリアルインターフェイスが実装されていますが、すべてのシリアルインターフェイスを目的に使用できるわけではありません。 たとえば、USBインターフェースは固定周波数で動作し、そのハードウェアはプロトコルに厳密に接続されているため、CANおよびGOSTにも適用される目的のために実質的に変更することはほとんど不可能です。 UARTを使用すると、状況は非常に良くなり、その速度は広い範囲内で変更できます。また、パルスはアクティブレベルから開始されるため、開始ビットの存在は障害になりません。 唯一の重要な制限はアクティブレベルの不一致です。これは、一致する要素を導入することで解消できます。 しかし、2つのUARTがすべて他のタスクに使用されていたため、このようなソリューションは解決されませんでした。

その結果、同期シリアル通信SSPの3つのユニバーサルモジュールの1つに基づいて1-Wireインタフェースを実装することが決定されました。 これらのモジュールの機能の詳細な説明は、メーカーMKのドキュメントに記載されています。 つまり、これらのモジュールを使用すると、MK内で生成されたモジュールのクロック周波数と同期し、シリアルコードで出力ポートに情報を発行し、同時に上記の周波数を参照してMKの入力ポートで情報を受信できます。 同時に、双方向の交換を整理するために、一緒に接続されたモジュールデータの出力と入力を使用しますが、クロックラインと同期ライン上の信号は使用せず、汎用ラインとして使用できます。これは、柔軟なMKピンコンフィギュレーションシステムで許可されます。 送信されたバイトを使用して、1ビットの送信/受信に関連する時間間隔をエンコードすることが想定されていますが、バイトビットの値は、アクティブレベル(ビット0)とその不在(ビット1)の期間を決定します。 SSP設定を決定するとき、最小送信間隔は1〜15μsであり、最大カウント間隔は情報ビットで60〜120μs、リセット信号で少なくとも480であることを考慮する必要があります。 最小間隔として10マイクロ秒を選択すると、最初の条件が満たされ、ビット間隔の期間は6〜12の最小間隔になり、図8はこの範囲にうまく適合します。 リセット信号の持続時間は少なくとも48サイクルになり、バイトのビット数を超えます。 最後の問題を解決するには、最小間隔の期間を変更するか、1バイト以上の情報を使用してパルスを送信する必要があります。 後者の方法は、個々の送信バイトの送信間隔の不確実性に関する問題を引き起こす可能性があり、したがって、結果として生じるパルスの持続時間が予測できないほど長くなる可能性があります。 幸いなことに、SSPモジュールには8個の16ビットFIFOバッファーが装備されているため、16 * 8 = 128ビットの最終バッファー長は、480 + 60 + 240 = 780/10 = 78ビットの可能な最小シーケンス長と重複します。

したがって、SSPを使用するための次のアルゴリズムが構築されます:必要なモードと必要な送信周波数を構成し、トランスミッターの動作を禁止し、必要な時間間隔を提供するためにトランスミッターバッファーを情報で満たし、トランスミッターを有効にします。 モジュールは、出力データラインに沿ってシリアルコードで情報の送信を開始し、送信の最後にレディフラグが立てられます。これは、データの次のバッチを形成できるMK信号として機能します。 この場合、送信された信号のタイムダイアグラムは、モジュールクロック周波数に厳密に結び付けられます。これは、MKクロック周波数のみに依存し、その時点でどのプログラムが実行されようとも、決して変更できません。 さらに、シーケンスの個々のバイトの送信の間に、機器によって決定される間隔のみがあり、シーケンスを形成するときに考慮することができます(研究は、そのような間隔を排除できることを示しています)。 SSPモジュールを構成するプロセスを検討してください。

SSPモジュールは3つのモードで動作できます-

モトローラSPI

Texas Instruments SSI

National Semiconductor Microwireインターフェース。

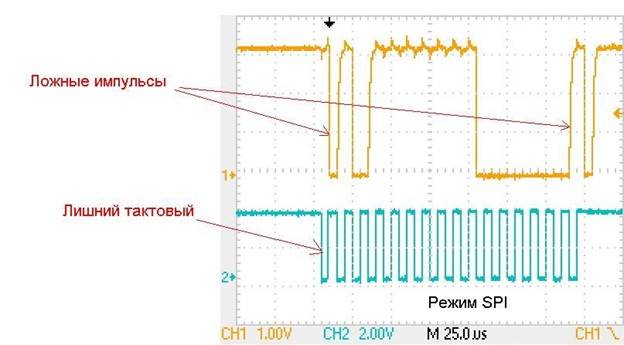

これらの3つのモードのうち、後者は適切ではありません。オシロスコープで検査を開始する前に、最初の2つのモードは信号フォーマットに追加の要件を課すからです。 ここで、SPIモードの特徴は、隣接ワードの送信間の1ビットの遅延であり、これは使用しない同期信号を送信するのに役立ちます。 これらの瞬間に0がデータラインに現れなかった場合、ビット間の間隔がわずかに増加するため、これはそれほど重要ではありません。これは1-Wireの要件に従って完全に受け入れられません。

図1. SPIモードでの偽パルス

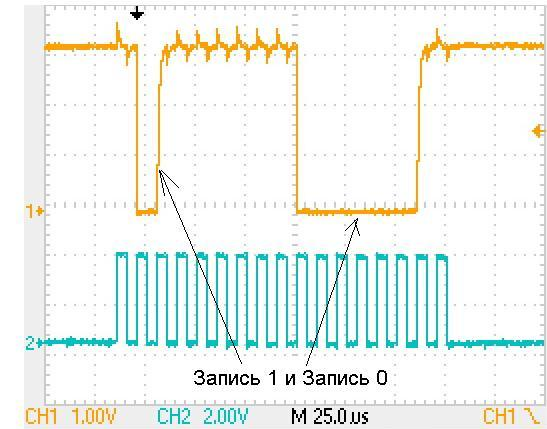

SSIモードにこのような欠点がないことは非常に幸運であり、そうでなければプログラムを大幅に複雑にする必要があります。 研究では、SSIモードでは、ワード間隔が単に存在せず(最後のビットで同期パルスが送信される)、したがって、伝送ラインに「ギャップ」がないことが示されています。 伝送線と同期線の構成時に、信号レベルに文書化されていない変更がありますが、SSPモジュールをセットアップした後のデバイスの操作は、これらの放射の結果を抑制するリセットパルスで開始されるため、この実装には影響しません。

図2. SSIイネーブル時の偽パルス

問題は簡単な方法で解決されたため、実際のSSIモードを使用するアプリケーションの場合は理解する必要がありますが、エミッションの原因を探すことはありませんでした。 上記の波形では、0xBF81パターンに対応する次の基準信号が適用されました。

図3.偽パルスのない信号。

すべての図で、図1および3の上の信号(黄色)はデータライン、下の信号(青)はクロック周波数ライン、図2では同期ラインです。 インターフェースの実装の下位の信号は使用されず、時間間隔を決定するために参照順序で与えられます。

したがって、リセットパルスの送信とプレゼンスパルスの存在は、次の擬似コードで表すことができます。

; 0F800 00000 00000 001FF 0xFFFF 0xFFFF // (50 , 500 , 410 ); ; " "; ; 6 – – SSP; 0xF800 0x0000 0x0000 0b000X1XXXXX0XXXXX 0xXXXX 0xFFFF – – - .

いくつかのポイントを説明します-SSPへの送信は受信と同時に行われ、入力データのゲーティングの瞬間は半クロックサイクル(5マイクロ秒のクロック周波数で)シフトします。したがって、読み取り時には、送信されるワードとまったく同じ数のワードを取得する必要があります。最後の1つを除いて、ゼロが受け入れられます(1でなければなりませんが、特定の値は、ラインキャパシタンスとプルアップ抵抗の抵抗に依存します)。 次の機能-「バッファが空」フラグは、情報の最後のワードがシフトレジスタに転送された直後に設定されますが、ビットが転送される前に、「デバイスがフリー」フラグを使用する必要があります(技術資料を参照)、そうでない場合、最後のワードが表示されません さらに、さまざまなパターンを使用してデバイスの誤動作に関するより詳細な情報を取得できますが、これは技術的な実装の微妙な点です。

ゼロと1つのパルスを送信するための同様の手順が簡単に作成され、1つの16ビットSSPワードで2ビットの1-Wireを連続して送信することは論理的です。 4 SSPワードで1-Wireバイトをすぐに転送する手順をお勧めします。 送信の最後に、受信バッファを読み取って送信データのコピーをそこから削除することを忘れないでください。 読み取りの場合、レコード1に対応するシーケンスを形成し、受信情報を分析して受信ビットの値を抽出する必要があります(パターン0b01111111を送信し、ケース1では0b01111111を、ケース0では0b00XXXX11を受け入れます)。 長いメッセージの送信については、開発されたダイレクトメモリアクセスデバイスを使用してソフトウェアを整理するオプションを検討することができます(これも十分に文書化されていません)。そのチャネルの1つがSSPモジュールとの対話を担当します。

インターフェースの提案された構成には欠点があることに注意してください-受信値はクロック信号の前面に沿って固定されます。つまり、受信情報を歪めるライン上の短いパルスを「キャッチ」できます。 この問題は、受信した情報をより詳細に分析することで解決できます。たとえば、採用されたパターン0b00100111では、左から3番目の単位ビットが干渉と見なされます。 もちろん、このような方法は最適とは見なされませんが、そのようなイベントの可能性は、純粋なソフトウェア実装の障害の可能性よりも計り知れないほど低いことを理解する必要があります。 それにもかかわらず、使用されるMK 1986BE1Tでは、ハードウェアレベルで干渉に対処することができます。つまり、各入力ポートにはノイズ耐性を高めるプラグインシュミットトリガーが装備されており、さらに、入力での短いパルスを抑制するプラグインフィルターが装備されています。 残念ながら、マイクロコントローラ開発者の他の多くの興味深いソリューションと同様に、この部分の文書化は非常に不十分です。

上記の方法に基づいて、Cサブルーチンのライブラリが実装され、次の構成の1986P1TマイクロコントローラSSPモジュールを介して1-Wireインターフェイスで動作します。

1.ハードウェアの操作の最下層は、メーカーのWebサイトで利用可能なBSP MDR1986VE1Tの一部であるMKレジスタ管理ルーチンです。

2.次の層には、公開されていない低レベルの書き込みおよび読み取り関数が含まれます。

3.インターフェース実装層は、開発者に1-Wireインターフェースへのフルアクセスを提供し、以下のモジュールが含まれます。

Init1Wire-要求されたSSPモジュールのハードウェアを初期化し、制御構造へのポインターを返します。

Reset1Wire-接続されたデバイスの初期インストールを実行し、その可用性についてレポートします。

Search1Wire-インターフェースに接続されているデバイスを検索し、そのアドレスを返します。

Adres1Wire-インターフェイス上の特定のデバイスをアドレス指定します。

WriteByte1Wire-選択したデバイスに任意のバイトを書き込みます。

ReadByte1wire-選択したデバイスから1バイトを読み取ります。

4.インターフェース実装層では、デバイスとの対話を簡素化するための追加機能が作成されています。

WriteData1Wire-選択したデバイスにデータセットを書き込みます。

ReadData1Wire-選択したデバイスからデータセットを読み取ります。

5.デバイス実装レイヤーはレイヤー3に基づいており、DS1990タイプの電子キーとの対話の例として提示されています。

一般的な結論は、MK 1986BE1Tは、さまざまなデジタルデバイスを作成できる可能性がある国内メーカーの興味深い製品であり、このマイクロコントローラー用の非標準のものを含め、最小限のソフトウェアコストでさまざまなインターフェースを実装する豊富な機会を持つ訓練を受けた専門家を提供するということです。

PS投稿が一般の人にとって興味深いものである場合、次に、同じSSP I2Cインターフェイスでのすべての実装について説明できます。