マシン命令を実行するとき、データはいくつかの場所にある可能性があります:プロセッサー自体のレジスター、命令でエンコードされた定数の形式、およびRAM。 データがメモリ内にある場合、それらの位置は何らかの番号(アドレス)によって決定されます。 この記事を読む過程で明らかになるいくつかの理由により、命令にエンコードされたソースアドレスはいくつかの変換を経ます。

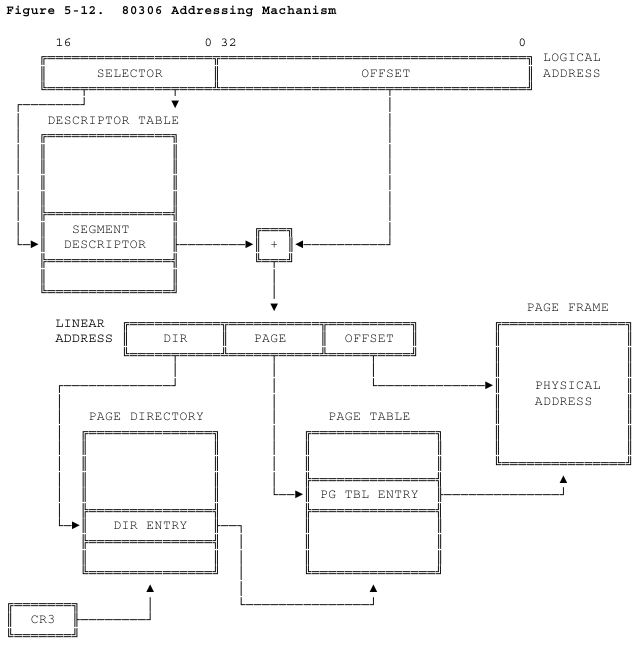

この図は、27年前に見たアドレスのセグメンテーションとページ変換を示しています。 1986 Intel 80386プログラマーズリファレンスマニュアルの図 。 面白いのは、写真の説明に2つのタイプミスがあることです。「803 0 6 M のメカニズムへの対処」。 現在、住所はより複雑な変換を経ており、イラストはもはや擬似グラフィックで行われていません。

最後から少し始めましょう-変換チェーン全体を目標に。

物理アドレス

この記事で後述する他の種類のアドレスのすべての変換の最終結果は、 物理アドレスです。 アドレス変換のための中央処理装置内の作業を終了します。

最終結果?!

実際、これで終わりではないことは容易に理解できます。 プロセッサからのデータ要求を処理する必要のあるプラットフォームには、独自のブロッキング構造を持つ複数のDRAMチップと、物理メモリの合計スペースにマッピングされるさまざまな周辺機器が存在する場合があります。 何らかの物理アドレスを使用した追加のトランザクションパスは、プラットフォームデバイス内のパスにある複数のデコーダーの構成に依存します。

実効住所

効果的な住所は旅の始まりです。 これは、個々のマシン命令の引数で指定され、その中に明示的または暗黙的に指定されたレジスタ、オフセット、およびスケーリング係数の値から計算されます。

たとえば、命令の場合(AT&T表記のアセンブラー)

addl %eax, 0x11(%ebp, %edx, 8)

宛先オペランドの実効アドレスは、次の式で計算されます。

eff_addr = EBP + EDX * 8 + 0x11

論理アドレス

実効アドレスが示されているセグメントの数とパラメーターを知らないと、後者は役に立ちません。 セグメント自体は、 セレクタと呼ばれる別の番号によって選択されます。

selector:offset

として記述された数値のペアは、 論理アドレスと呼ばれます 。 アクティブなセレクタは特別なレジスタのグループに格納されるため、多くの場合、ペアの最初の番号ではなく、ds:0x11223344のようにレジスタの名前が書き込まれます。

ここで、通常、これらの概念に初めて直面する人にとっては、頭が回転し始めます。 状況を単純化(または複雑化)するために、セレクター(およびそれに関連付けられたセグメント)の選択はほとんど常に、アクセスの「意味」に基づいて行われるという事実をいくらか助けます。 デフォルトでは、マシン命令のエンコードで特に指定されていない限り、CSセレクターの論理アドレスを使用して、DSのデータ、SSのスタックのコードアドレスを取得します。

行アドレス

実効アドレスは、セグメントの先頭からのオフセット、つまりベースです。 ベースと実効アドレスを追加すると、 線形アドレスと呼ばれる番号が得られます 。

lin_addr = segment.base + eff_addr

論理→線形変換は、常に成功するとは限りません。実行時に、記述子のフィールドに記録されたセグメントのプロパティのいくつかの条件がチェックされるためです。 たとえば、セグメントとアクセス権の境界のチェックアウト。

リアルモード

セグメンテーションが有効な場合、上記のことが当てはまります。 16ビットリアルモードでは、セレクターの意味が異なり、セレクターはベースのみを格納し、変換はセグメントチェックを実行しません。 実際、CS、DS、FS、GS、ES、SSの指定は、これら2つのモードでまったく異なる意味を持ち、混乱を招きます。

セグメンテーションは、コンピューター技術の開発のある段階で流行しました。 現在、ほとんどすべての場所で他のメカニズムに置き換えられており、特定のタスクにのみ使用されています。 そのため、IA-32eモード(64ビット)では、2つのセグメントのみがゼロ以外のベースを持つことができます。 このモードの他の4つの場合、線形アドレス==は常に有効です。

仮想アドレスとは何ですか?

文献および他のアーキテクチャのドキュメントには、別の用語- 仮想アドレスがあります 。 IA-32のIntelのドキュメントでは使用されていませんが、たとえば、セグメンテーションが使用されていないIntel®Itaniumの説明に記載されています。 IA-32の場合、virtual == linearと安全に仮定できます。

コンピューター工学に関するソビエトの文献では、このタイプのアドレスは数学とも呼ばれていました。

ページ変換

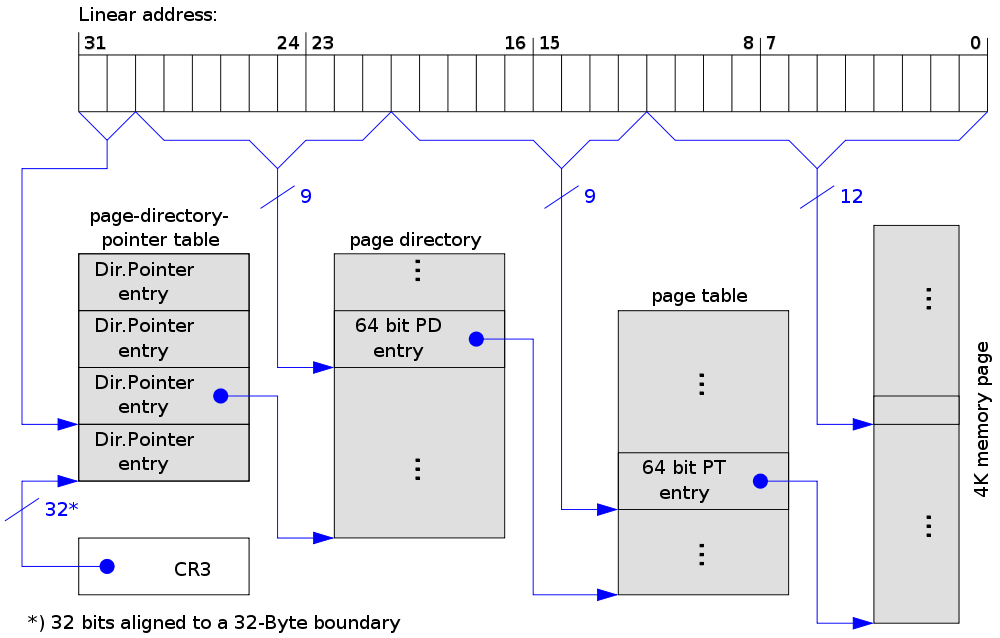

セグメンテーション後の次のアドレス変換:線形→物理-プロセッサのモード(32ビット、PAEまたは64ビット)に応じて、アルゴリズムに多くのバリエーションがあります。

ページングに影響するもの

現在、異なるプロセッサシステムレジスタからの異なるビットがページ変換プロセスにどのくらい影響するかは注目に値します。 Intel SDMの最新の9月版[1]を見て、CR0.WP、CR0.PG、CR4.PSE、CR4.PAE、CR4.PGE、CR4.PCIDE、CR4.SMEP、CR4.SMAP、IA32_EFERの完全なリストを示します。 LME、IA32_EFER.NX、EFLAGS.AC。

ただし、一般的な考え方は常に同じです。線形アドレスはいくつかの部分に分割され、各部分はメモリに格納されているシステムテーブルの1つのインデックスとして機能します。 テーブルのエントリは、次のレベルのテーブルの先頭のアドレス、または最後のレベルの場合、メモリ内のページの物理アドレスとそのプロパティに関する必要な情報です。 最下位ビットは変換されませんが、見つかったページ内のアドレス指定に使用されます。 たとえば、ページサイズが4 KBのPAEモードの場合、変換は次のようになります。

異なるプロセッサモードでは、これらのテーブルの数と容量は異なります。 次のテーブルに有効なデータが含まれていない場合、または最後のテーブルに保存されているアクセス権がページへのアクセスを禁止している場合、変換は失敗する可能性があります。 たとえば、読み取り専用としてマークされた領域に書き込む場合、または特権のないプロセスからカーネルメモリを読み取ろうとする場合。

ゲストフィジカル

Intelプロセッサにハードウェア仮想化機能が導入されるまで、ページ変換はチェーンの最後でした。 複数の仮想マシンが同じシステムで実行されている場合、それぞれで受信した物理アドレスをもう一度送信する必要があります。 これは、プログラムで行うことも、プロセッサがEPT(拡張ページテーブル)機能をサポートしている場合はハードウェアで行うこともできます。 以前は物理と呼ばれていたアドレスは、実際の物理と区別するためにゲスト物理に名前が変更されました。 EPTトランスフォームを使用してリンクされます。 後者のアルゴリズムは、前述のページ変換に似ています:共通のルートを持つ関連テーブルのセット。最後のレベルは、指定されたゲスト物理に対して物理ページが存在するかどうかを決定します。

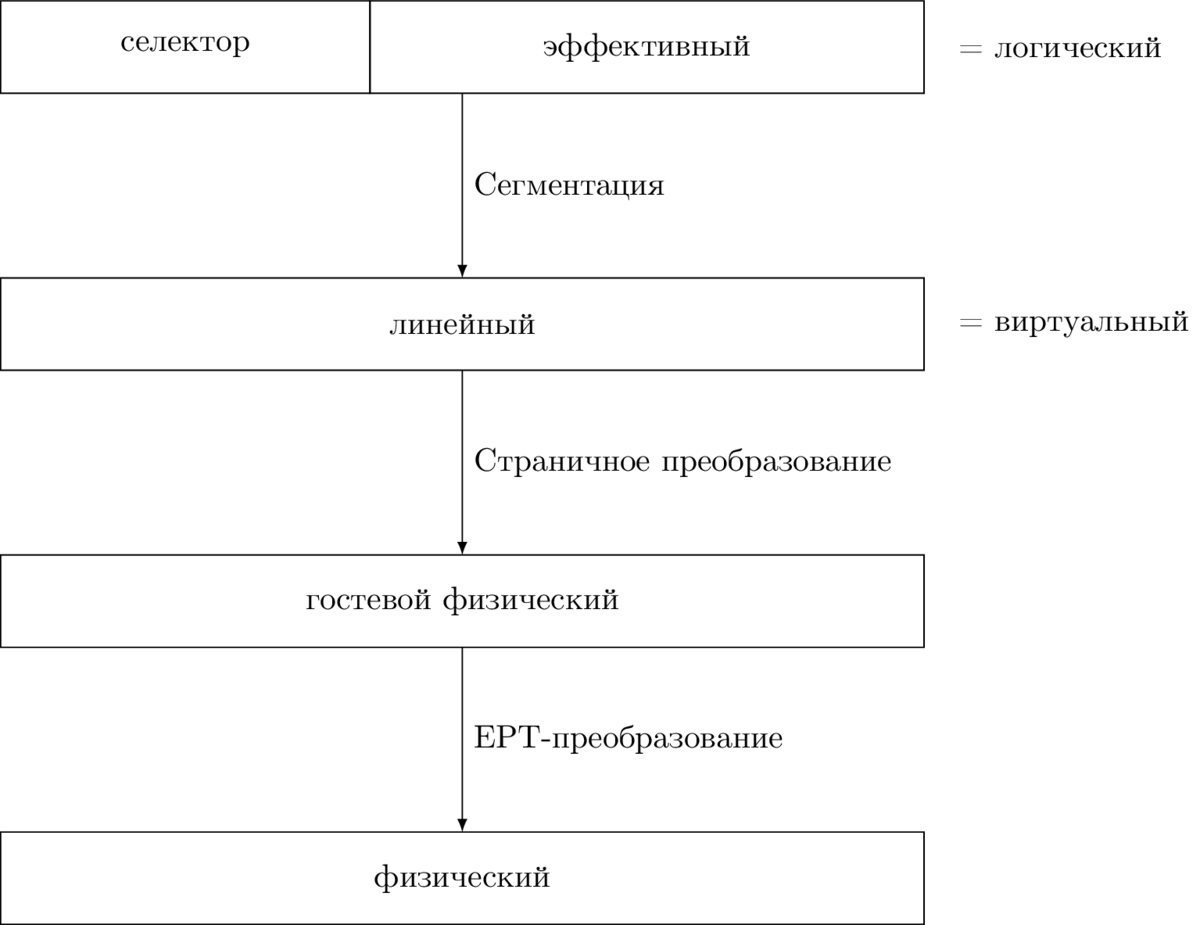

全体像

すべてのアドレス変換を1つの図にまとめようとしました。 その中で、変換は矢印で示され、アドレスタイプはフレームで囲まれています。

前述のように、各変換は、チェーンに続く形式の表現を持たないアドレスに対してエラーを返す可能性があります。 このような問題の排除は、仮想メモリの抽象化を実装する仮想マシンのオペレーティングシステムとモニターのタスクです。

おわりに

自然の中にあるもの、技術の中にあるものの進化は奇妙なことです。 合理的な設計の観点からは説明できない予期しない構造が生じます。 彼女の作品はアタビズムに満ちており、その行動の規則は、ほとんど完全に例外からなる場合があります。 このようなシステムの動作を理解するためには、最初から、すべての層の積み重ねの下で、「何も捨てないで」という原則の形で真実を見つけるために、その進化をスクロールすることがしばしば必要です。 IA-32アーキテクチャーは、進化的開発の優れた例と考える傾向があります。

PSすべては他のみんなと同じです

この記事を終えてまもなく、IBM System zアーキテクチャーに関するプレゼンテーションに出会いました。これは、仮想化をサポートしてきた長く興味深い歴史で有名です。 このドキュメントは、System zで使用されるすべてのタイプのメモリアドレスの列挙を見つけました。

ご覧のとおり、そのうち5つがあります。

- 仮想:動的アドレス変換(DAT)による実際のアドレスへの変換

- Real:プレフィックスレジスタを使用して絶対アドレスに変換

- 絶対:プレフィックスレジスタを適用した後

- 論理:プログラムから見えるアドレス(これは仮想アドレスでも実アドレスでもかまいません)

- 物理:構成配列によって絶対アドレスに変換されます

ご覧のとおり、そのうち5つがあります。

ご清聴ありがとうございました!

文学

- Intel Corporation。 インテル®64およびIA-32アーキテクチャーソフトウェア開発者マニュアル。 ボリューム1〜3、2014。www.intel.com / content / www / us / en / processors / architectures-software-developer-manuals.html