こんにちは、カブロビテス。

第1部の調査では、UEFIドライバーの開発に関するトピックがコミュニティにとって非常に興味深いことが示されたため、このシリーズのさらなるパートの執筆を開始します。 この記事では、Intel Galileoボードの作業準備、必要で望ましいハードウェアとソフトウェア、およびBSPのアセンブリとインストールに焦点を当てます。 その結果、UEFIドライバーのハードウェアデバッグに適した、すべての愛好家がアクセスできる安価なハードウェアプラットフォームができました。

エントリーと免責事項

伝統的に、あなたはあなた自身の危険とリスクで以下のすべての情報を使用することに言及する必要があります、著者はボードパフォーマンス、時間、気分および/または人類への信仰の損失の可能性について責任を負いません。 記載されているものはすべてオープンソースから引用されており、そのリストはこの記事の最後に記載されています。この出版物は、私の側のNDAの違反とは見なされません。

クッキングアイロン

ボード自体

まず最初に、何らかの方法でIntel Galileoボードを入手する必要があります。 第一世代であろうと第二世代であろうと(UEFIとソフトウェア側からは違いはありません)、主なことは、電源とUARTコンバーター(必須)、およびJTAGデバッガーとISPプログラマー(できれば)に接続できることです。 このボードは、当社によるQuark SoCの機能と展望の研究の一環として私に来たもので、ドイツのIntel駐在員事務所から直接受け取りました。 普通の人にとって、最も簡単な方法はこのボードを購入することです。UART

UARTを介してGalileo Gen 1に接続するには、AJ-COMケーブルが必要です。これは、このスキームに従って最も簡単に作成できます。

PCにCOMポートがない場合は、市販されているCOM-USBコンバーターを使用する必要がありますが、これらは安価であり、PL23xx / FT232 + MAX232からそのようなコンバーターを作成することは大きな問題ではありません。 私の場合、Intelの善良な人々はAJ-COMケーブルとPL2303 COM-USBコンバーターをGalileoの箱に入れました。

Galileo Gen1のユーザーレビューと操作経験により、Intelエンジニアは、以前はCOMポートとの互換性レベルを変更していた3.5インチステレオジャックコネクタとMAX232チップを交換し、USB-TTLケーブルと互換性のあるコームに交換しましたFTDIとここにそのようなピン配置がある:

したがって、Gen 2 UARTポートに接続するには、 TTL-232R-3V3に似たケーブルで十分です 。これも前述のPL23xx / FT232から独立して作成できます。 このような交換は、Intel(MAX232が回路から外された)と、2本ではなく1本のケーブルのみを必要とするユーザーの両方にとって有益です。 さらに、DIYエレクトロニクスの世界に少しでも精通しているほとんどすべての人がすでにUSB-TTLコンバーターを持っています。

JTAG

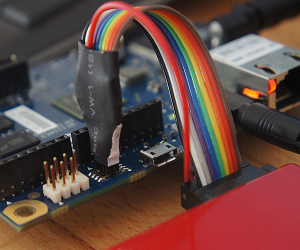

前のパートで書いたように、Galileoは、Intel XDPのような高価なコンバーターを接続する必要なく、JTAG TAPポートがすぐに利用できる、私の知る限りx86ベースのCPUボードです。 一方では、これによりハードウェアデバッグの非常に幅広い可能性が開かれ、他方では、UEFIドライバーのデバッグのほとんどすべてのケースで、UARTを介したデバッグメッセージで十分です。 一方、この機会は猶予なしに見逃されるため、デバッガー接続の削除も説明する価値があります。GalileoのJTAGコネクタとして、1.27 mmのピッチの10ピンコネクタが使用されていますが、これは接続できません-小さい伝染性のコネクタです。 Intelは、 このアダプターを「通常の」20ピンJTAGコネクターに使用することをお勧めします。これは良い提案ですが、はんだ付けができる人にとっては、より良い提案があります。 JTAGデバッガーまたは各ワイヤのBLSチップと互換性のあるコネクタで側面をはんだ付けします。 ボードの側面から見ると、次のようになります(洗浄されていないフラックスをおaびします)。

これでアダプターは不要になり、サポートされているOpenOCDのリストから任意のデバッガーにボードを接続できます。 Intelでは、GalileoでのデバッグはTinCanTools FLYSWATTER2およびOlimex ARM-USB-OCD-Hでテストされましたが、これらのデバッガーはどちらも美しいパッケージの通常のFT2232Hなので、MPSIでFTPSI 232シリーズのボードを使用してGalileoをデバッグできます。 デバッガーとデバッグの詳細については、次のいずれかをご覧ください。

ISP

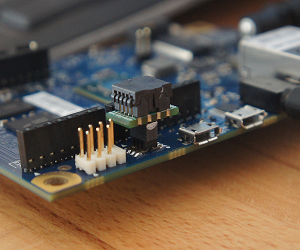

UEFIドライバーの開発とデバッグのエラーは、多くの場合、ボードのロードを停止するという事実につながり、リカバリイメージまたは外部プログラマーを使用してSPIチップの内容のリカバリを使用する必要があります。 さらに、開発にはファームウェアの継続的な更新が必要であり、標準のCapsuleApp.efiユーティリティを使用してファームウェアを更新するたびに時間がかかり、すぐに気になります。 そのため、プログラマをガリレオに接続して縫うのが理にかなっています。 残念ながら、このボードでISPプログラマーとしてFT232Hボードとflashromユーティリティを使用する試みはこれまで成功していません。この問題が解決するまで、 Samedisk ZC2511プログラマーを使用します 。 インテルは、 Dediprog SF100を使用することを提案していますが、これも非常に適しています。 既にSPIプログラマをお持ちの場合は、以下のピン配列に従って、ボードの前面の右上にあるISPコネクタに接続してみてください。

叙情的な余談、またはSPIエミュレーターについての少し

実際、ISPは進歩の頂点ではなく、専門のファームウェア開発ではSPIプログラマーの代わりにSPIエミュレーターが使用され、ファームウェアの更新時間が1〜2秒に短縮されます。 それらは高価格(1個あたり約500-700ドル)のために普通の人には利用できないので、私はそれらについて詳しくは述べません。 最大128 Mbitの容量を持つさまざまなメーカーのSPIチップをエミュレートできるSamedisk ZC25128エミュレータを使用します。 OSの観点から見ると、エミュレーターは通常のUSBフラッシュドライブのように見え、ファイルをコピーするだけでファームウェアを更新できます。 これまでのところ、私の記憶には、システムがエミュレーターからの起動を拒否した場合(ベイトレイル用のIntel CRB)が1つしかありません。そのため、ソリューションに生命権があることを認識する価値があります。 このようなデバイスの希少性(およびそれに関連して、高コスト)だけが驚くべきことです。これは、2番目のマイクロコントローラーに複数のSPIハードウェアチャネルがあり、エミュレーターの生産を妨げるものがないためです。エミュレーターとの互換性のために、Galileo Gen 1ボードを変更し、SPIチップをエミュレーターまたはZIFベッドのSPIチップのいずれかを接続する特別なコネクターに置き換えました。 次のようになります。

これで、ようやくハードウェアの準備が整いました。ソフトウェアの準備を開始できます。

調理ソフトウェア

組立プラットフォーム

Galileoには、根本的に異なる2つのソフトウェアセットがあります。これらはBSPとArduino Softwareです。 最初のセットは、UEFIファームウェアとIntelが提案するYocto Linuxの基本バージョンの両方をいくつかのバージョンでアセンブルするために必要です。最も一般的なバージョンは、galileo-spiとgalileo-fullの2つです。 1つはSPIチップから直接起動し、Arduinoスケッチを実行できる最小のLinuxシステムです。2つ目は通常のLinuxに似ていますが、SDカードからロードする必要があります。 このタイプのブートには小さな問題があります。ほとんどのGen1ボードは、SDカードから何かを開始するためにファームウェアの更新が必要なので、Intelが準備したイメージをすぐに開始することはできません。この記事ではArduinoとの互換性に関心がないため、 ソフトウェアパッケージ全体から、通常Board_Support_Package_Sources_for_Intel_Quark_vX.YZTzipと呼ばれるBSPのアーカイブのみが必要です。現在の最新バージョンは1.0.1.7です。 Intelは、BSPを構築するためのプラットフォームを、Ubuntu 12.04 x64だけで必死に選択しています。 もちろん、別のLinuxディストリビューション(Ubuntu 14.04から試しましたが、最小イメージがビルドされ、完全なイメージがなくなっています)またはOSXまたはWindowsからビルドすることもできますが、必要なバージョンを仮想マシンにインストールしてビルドを実行する方がはるかに簡単です彼女。 Ubuntuのインストールについては詳しく説明しません。BSPアセンブリの各段階でインストールする必要があるパッケージのリストのみを示します。

BSPアセンブリ

ゼロステップ

したがって、Ubuntu 12.04 x64がインストール、更新、ダウンロードされ、最後のBSPからのアーカイブがダウンロードされて解凍されました、明確にするために、〜/ Galileo /で、インターネットに接続しており、しばらく時間を過ごす準備ができています。ビルドを開始する前に、パッケージbuild-essentialおよびgcc-multilibをインストールする必要があります。 それらは、アセンブリのすべての段階で必要です。 また、各ステップで作成されるアセンブリ環境の競合を防ぐために、各ステップで〜/ Galileo /で新しいターミナルを開くことをお勧めします。

UEFIビルド

UEFIをビルドするには、 subversion 、 uuid-dev、およびiaslパッケージをインストールする必要があります 。 その後、Quark_EDKII_vX.YZtar.gzアーカイブを解凍し、解凍中に作成されたQuark_EDKII_vX.YZディレクトリに移動して、その中のsvn_setup.pyスクリプトを実行し、次にsvn updateコマンドを実行して 、ビルドする必要のあるEFI Development Kitパーツをダウンロードします。 ダウンロードが完了したら、コマンド./quarkbuild.sh -d32 GCC46 QuarkPlatfromを実行する必要があります。これにより、Quark SoC(Galileo)に基づくプラットフォームのGCC 4.6(Ubuntu 12.04の場合)を使用して、UEFI(d32キー)のデバッグバージョンの構築が開始されます。 アセンブリが完了すると、QUARK.fdファイルはBuild / QuarkPlatfrom / DEBUG_GCC46 / FV /ディレクトリに配置されます-これはファームウェアの不完全なイメージであり、次の部分で必要になります。Applicationsサブディレクトリは、UEFI Shellからファームウェアを更新するために使用されるCapsuleApp.efiユーティリティですプログラマーがいない場合は使用する必要があります。アセンブリグラブ

このボードのBDSフェーズのデフォルトのブートローダーとして、Intelはかなり変更されたGRUB v1の使用を推奨しています。 Yocto Linuxの最小ビルドでも作成することになっている場合は省略できますが、この場合は組み立てる必要があります。 gnu-efi 、 autoconf 、 libtool、およびgitパッケージをインストールする必要があります。 通常どおり、GRUBでアーカイブを解凍し、解凍後に作成されたディレクトリに移動してgitsetup.pyスクリプトを実行し、作業サブディレクトリに移動してautoreconf --installコマンドを実行し 、 CC4GRUB = 'gcc -m32 -march = i586 -fno-stack-をエクスポートしますprotector ' 、 エクスポートGNUEFI_LIBDIR = / usr / lib32 、 CC = "$ {CC4GRUB}" ./configure-quark.sh makeに時間をかけて 、バージョンにエラーがある場合は、まずエラーを修正する必要があります。 実際、コレクターはcrt0-efi.Sファイルをwork / efi / ia32 /に入れるのを忘れていましたが、それなしではGRUB(これはスタートアップコードです)をコンパイルすることができないため、ダウンロードする必要があります(たとえば、 ここから )、名前を正しく変更してコピーします上記のディレクトリに移動してから、明確な良心を持ってmakeコマンドを実行します 。 その結果、必要なgrub.efiファイルはwork / efi /にあります。Yocto Linuxの最小限のイメージの構築

SPIチップに配置される最小限のOSイメージを構築するには、 diffstat 、 texinfo 、 gawk 、およびchrpathパッケージをインストールする必要があり、前の手順に従わない場合はgitをインストールする必要があります 。 meta-clanton_vX.YZtar.gzアーカイブを解凍し、作成されたフォルダーに移動してsetup.shスクリプトを実行します。少し待つ必要があります。 アセンブリスクリプトがロードされるのを待った後、 ソースpoky / oe-init-build-env yocto_buildおよびbitbake image-spi-galileoコマンドを実行します 。その後、ソースからYoctoをダウンロードしてビルドするかなり長いプロセスが開始されます。 最小限のイメージを作成するには、約2 GBのディスクスペースが必要です。最も完全なイメージを作成するには、約35 GBが必要で、8 GBのRAMとSSDを搭載したCore i5-2500Kで約7時間かかります。 急に誰かが興味を持ったら、そのような画像の組み立てについて別の記事を書きます。水中の熊手が十分にあるからです。 一般的に、この場所で私はリラックスして組み立てプロセスを見ることを提案します。熱狂的な上記のすべてを1つのファイルにまとめる

OSイメージの準備が完了し、すべてのコンポーネントを一緒に組み立てることができます。 これを行うには、sysimageおよびspi-flash-toolsアーカイブを解凍し、sysimage_vX.YZ / sysimage.CP-8M-debug /ディレクトリに移動する必要があります。これには、他のすべてに加えて、layout.confファイルがあります。 お気に入りのテキストエディタで開き、すべてのパスとファイル名を正しいものに修正します。「PLAIN / DEBUG_GCC」を「DEBUG_GCC46」に、「image-spi-clanton.cpio.lzma」を「image-spi-galileo-clanton.cpio」に置き換えます。 lzma「メタクラントン」と「Quark_EDKII」に正しいバージョン番号を追加し、変更を保存することを忘れないでください。 次に、コマンド../../spi-flash-tools_vX.YZ/Makefileを実行します。その結果、Flash-missingPDAT.bin、Flash-missingPDAT.cap、およびFVMAIN.fvファイルがsysimage.CP-8M-debugディレクトリに作成されます。 後者はリカバリイメージとして使用され、2番目はmicroSDカードにコピーされ、UEFIシェルのCapsuleApp.efiを使用してGalileoのファームウェアを更新できます。最初のステップを完了するには、最後のステップが必要です。PlatfromデータをFlash-missingPDAT.binに追加する

最後のステップは、プラットフォーム固有の設定を追加することです。 これを行うには、spi-flash-tools_vX.YZ / platform-data /ディレクトリに移動し、お気に入りのエディターでsample-platfrom-data.iniファイルを開き、Gen1の[Platfrom Type]セクションのdata.value値を6に修正します。 Gen 2の場合、[Mrc Params] MRC / kipsbay-fabD.v1.bin(Gen 1)またはMRC / GalileoGen2.bin(Gen 2)のdata.valueで、その中のdata.type = hex.stringの例をコメントアウトします。同じセクションで[MACアドレス0]セクションのdata.value値をボードのイーサネットコネクタのラベルに印刷されたアドレスに変更すると、[MACアドレス1]はガリレオに変更できません。 その後、コマンド./platform-data-patch.py -p sample-platfrom-data.ini -i ../../sysimage_vX.YZ/sysimage.CP-8M-debug/Flash-missingPDAT.binを実行する必要があります。最後に、彼はFlash + PlatfromData.binファイルを作成し、プログラマーによるファームウェアの準備を整えます。

ヘルスチェック

前のステップで取得した画像をフラッシュし、ボードをUART経由でPCに接続し、お気に入りのターミナルを起動します(Windowsの場合、Putty / KittyまたはTeraTermをお勧めします)。対応するCOMポートに115200ボー設定、データ-8ビット、停止-1ビット、パリティとフロー制御は無効になり、電源をガリレオに接続します。次の図のようなUEFIデバッグメッセージのストリームが表示された場合、すべてが正しく行われています。 そうでない場合、彼らが言うように、 UIAを数回再チェックします。

結論と今後の計画

記事のこのパートの最後に、最初のステップでアセンブリをUEFIイメージに統合した場合に自己記述UEFIドライバーをデバッグするために正常に使用できる、準備およびテストされたハードウェアプラットフォームを取得しました。 次のパートでは、アセンブリプロセスを大幅に簡素化および高速化する方法、EDKコードベースへのドライバーの正確な統合方法、およびUARTを使用してドライバーをデバッグする方法を示します。 OpenOCDとGDBを別々に使用して、EclipseでのJTAGデバッグについて話す予定です。ちなみに、最初の部分には事実上コメントがありませんでしたが、これについてはコメントをお願いします。 ありがとう、次のパートでお会いしましょう。

情報源

Intel Quark SoC X1000ボードサポートパッケージ(BSP)ビルドおよびソフトウェアユーザーガイドIntel Quark SoC X1000でOpenOCD / GDB / Eclipseを使用したソースレベルのデバッグ

Intel Galileo Gen1回路図

Intel Galileo Gen2回路図

FTDI TTL-USBシリアルコンバーターケーブルのデータシート

Intel組み込みコミュニティ