2012年12月に3PAR 7200および7400システムのミッドレンジモデルが発表され、2013年5月に3PAR 7450モデルが発表されました。

この発表については、 「HPオールフラッシュアレイと3PARストレージシステムの10の大きな変更」を参照してください 。

過去1年間に3PARアレイにどのような革新的な技術が登場しましたか?

HP 3PAR製品は、ロシアのデータストレージ市場で最も急成長している製品として認識され、2013年には、500を超える3PARミッドレンジシステムがロシアで販売され、毎年2.5倍の成長を遂げました。

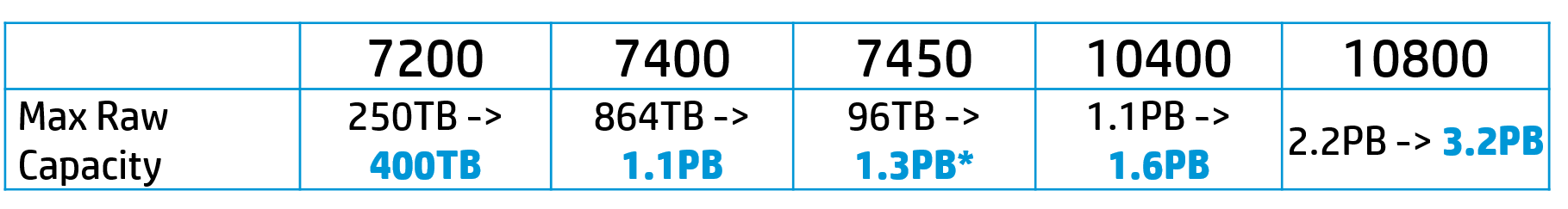

3PAR 7200モデルでサポートされるメディアの数が増えました。アレイは240個のディスクをサポートし、サポートされるraw容量は400TBに増えました。

7400モデルでは、サポートされるボリューム、スナップショット、イニシエーターの数が増加し、サポートされる容量が1.1 PBに増加しました。

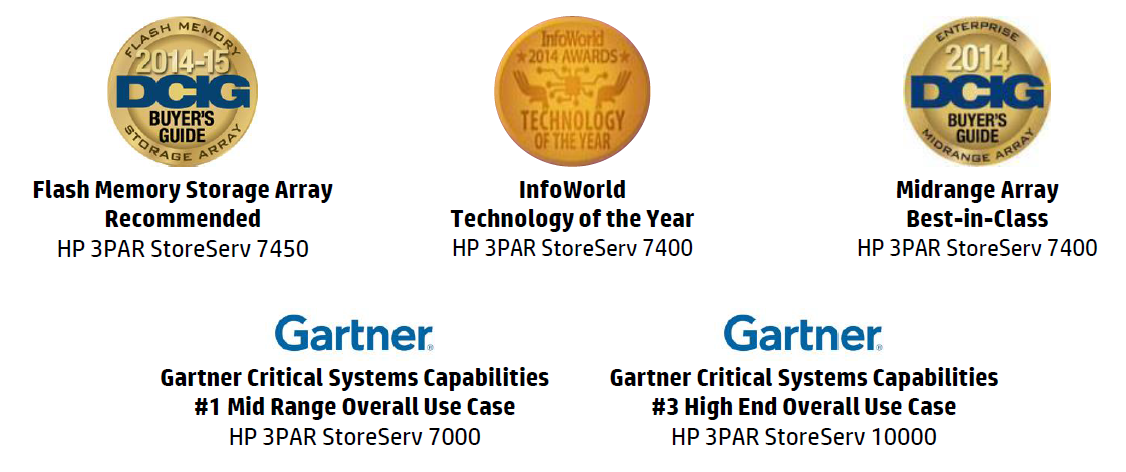

3PAR 7400モデルは、他のメーカーの50アレイと比較して200を超える指標に従って、DCIGによる2014年の最高のストレージシステムに選ばれました。

dcigbuyersguides.com/2014-enterprise-midrange-array-buyers-guide

また、InfoWorld 2014によると、7400アレイはクラス最高の名前が付けられました。

www.infoworld.com/slideshow/135876/infoworlds-2014-technology-of-the-year-award-winners-234225#slide27

3PAR 10400モデルでは、キャッシュサイズが192GBから384GBに変更されています。すでに購入済みの3PAR 10400モデルでは、キャッシュアップグレードオプションが利用可能です。 最小ファームウェアバージョンは3.1.2 MU3です。

3PAR 10800アレイの場合、サポートされるボリュームとスナップショットの数も増加し、サポートされるraw容量は3.2PBに増加しました。

新しい大容量ドライブのサポート

HP 3PAR 7000および10000モデルの場合、新しい4TB 7.2k NLディスクが発表されました。 サポートされる最大ストレージ容量も増加しました。

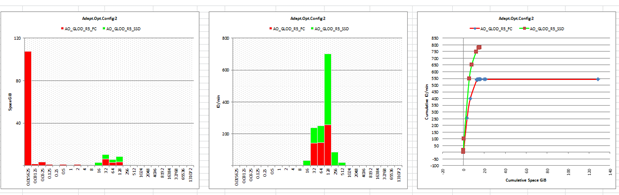

図1 3PARモデルの未加工容量増加表

オールフラッシュアレイ7450モデルの場合、1 TBあたりのコストは約50%削減され、アレイ操作の待機時間パラメーターは25%削減されます。

3PAR 7450システムのパフォーマンスについて話すと、システムパフォーマンスの改善が宣言されたことにより、HP内部テストによると、 540,000 IOPs @ 0.6msから900,000 IOPs @ 0.7msに大幅に増加しました 。

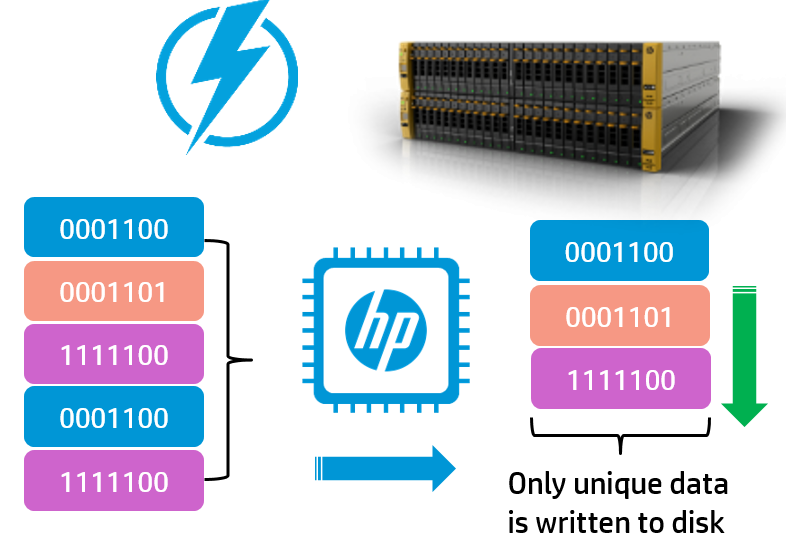

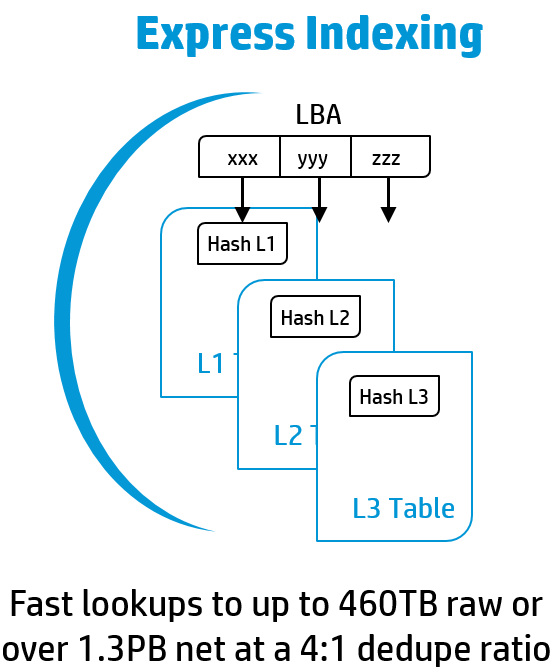

新しいリリース3.2.1では、HP 3PAR 7450は、負荷プロファイルとデータの性質に応じて、 4:1〜10:1の比率でブロック重複排除機能を追加します。 オンライン重複排除は専用のASICコプロセッサーによって実行されます。これにより、アレイのパフォーマンスは低下しません。 特許取得済みのHP 3PAR Express Indexingメカニズムにより、重複排除はシステムのスケーリングに影響を与えず、顧客は重複排除または1.3ペタバイトの使用可能容量なしで最大460テラバイトの「ネイティブ」容量のディスクアレイを取得できます。 後で、このメカニズムは他の3PARアレイに追加されます。 予備データによると、重複排除機能はすべてのモデルに無料で提供されます。

図2 HP 3PAR ASICデータ重複排除はオンラインで発生します

ゼロ検出機能のASICチップのハードウェア実装は、すべての3PARアレイで動作し、ファイバーチャネルデータストリームの反復可能なパターン(たとえば、仮想マシンの初期化時)を決定し、ディスクに物理的に書き込むことはできません。 HP 3PAR 7450の場合、これはディスクスペースの効率を改善するだけでなく、SSDの過度の摩耗も防ぎます。

3PAR 7000および10000アレイの記録容量の新しいSSDのサポートが追加されました。

480GB SSD、920GB SSD、2.5 "および3.5"フォームファクターを備えた1.9TB SSD。 したがって、3PARでは、高密度および高密度SSDのストレージレベルを注文できます。 新しいSSDドライブは、100、200、400、および800 GBドライブを使用する従来のアレイと比較して、5年保証が強化され、1Gbおよび1IOPSに関して非常に低コストです。 重複排除を使用する場合、シンプロビジョニングとゼロ検出HPは、情報のギガバイトあたり70ルーブルでストレージのコストを見積もっています。

ファームウェアの更新

MSI-Xサポート

MSI-X(Message Signaled Interrupts-eXtended)のサポートが追加され、コントローラーコンポーネントは特定の割り込みを処理するプロセッサー/コアを個別に選択でき、プログラムコードを実行せずにハードウェアレベルで完全に実行できました。 したがって、各アレイコントローラは、すべてのプロセッサコア間でよりバランスが取れています。

MSI-Xの使用は、コントローラー間の負荷分散の改善にもつながりました。

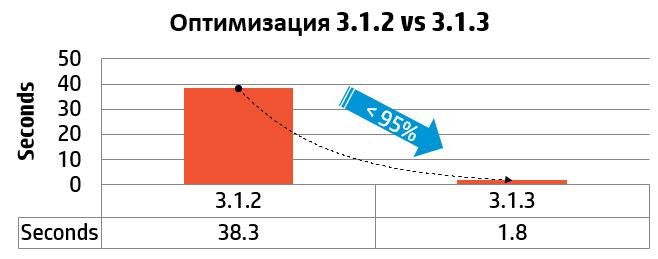

この改善の指標の1つは、仮想ボリュームの作成とホストへのプレゼンテーションの時間の短縮です。 ファームウェア3.1.3のアレイでのテストによると、プロビジョニングの時間は、ファームウェア3.1.2の同様のアレイと比較して95%に短縮されました。

図3 100ボリュームの作成時間の短縮

マイクロコード更新を使用した同様の構成の構成では、スループットが増加し、遅延が減少しました。

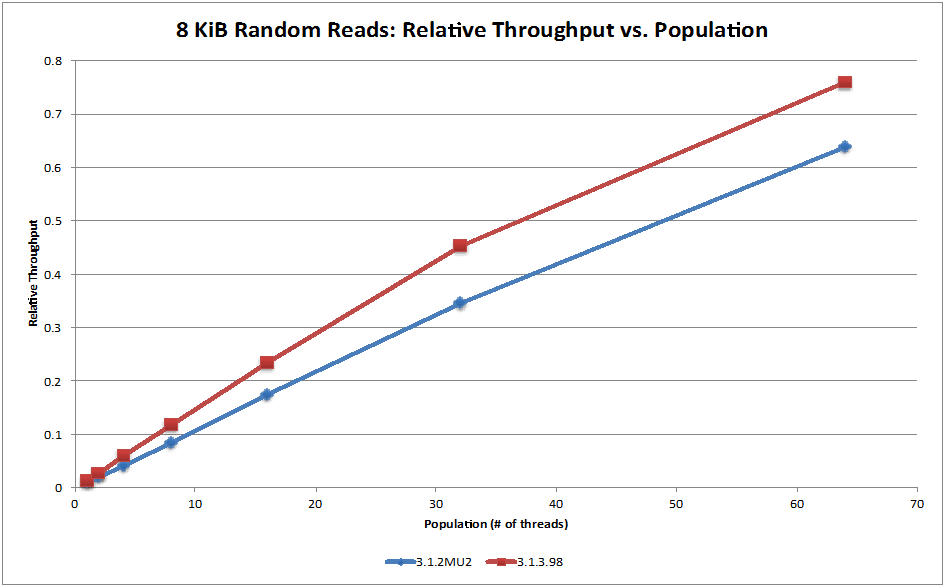

図4ファームウェア3.1.3を使用したアレイの帯域幅の増加

これらの変更の利点は、SSDの使用、ランダムな読み取りと書き込みの負荷下でのアレイの使用、および潜在的に、高負荷のデータがディスクの端に近い場所にある多数のHDDメディアを備えたアレイでの条件下で特に明白です。 IOPでのアレイ全体のパフォーマンスが向上する可能性があり、おそらく新しい高レートの3PARアレイのSPC-1ベンチマーク結果が更新されるでしょう。

SSDの改善

マイクロコードの新しいバージョンでは、SSDドライブの摩耗率が低下しています。 いくつかの世代の3PARアレイでは、SSDメディアの摩耗を減らすために次のメカニズムが使用されていることを思い出させてください。

1.各コントローラーはASICチップを使用して、ゼロブロックをSSDに書き込まずにその場で破棄します。

2.ディスクスペース仮想化を使用します。 SSD上のすべてのボリュームは、アレイ内のすべてのSSDキャリアで均等に配置され、これらのキャリアに均等に負荷がかかるため、早期の摩耗を防ぎます。

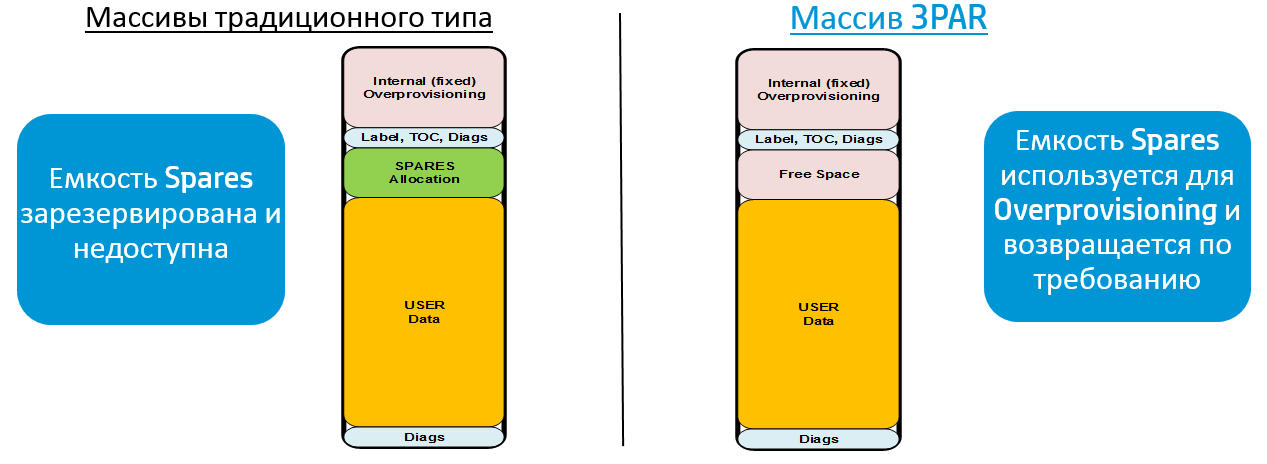

アダプティブスペアリングテクノロジーも追加されました。これにより、各SSDメディアのスペアスペースをオーバープロビジョニングに使用できるようになりました-記録操作を高速化し、SSDの寿命を延ばします。 SSDの性質により、ハードディスクなどのようにデータを直接上書きすることはできません。この場合、論理ブロックアドレス指定(LBA)と呼ばれる論理および物理データマッピングテーブルが使用されます。 データを上書きすると、新しい部分が空きブロックに書き込まれ、古い領域は古いものとしてマークされ、SSDコントローラーによって消去されます。 各書き換えプロセスは、セルの寿命をかなり短くします。さらに、オペレーティングシステムはこれらのセルの一部をスペア用に予約するため、使用できなくなり、SSDメディアの寿命がさらに短くなります。

バージョン3.1.3の3PARでは、SSDの新しい動作モードが登場しました-各SSDのスペア用に予約された容量はブロックされませんが、読み取りおよび書き込みの加速操作用に与えられ、メディアでエラーが発生した場合にのみ、この容量はスペアに戻されます。

図5スペアSSDスペースを使用して読み取りおよび書き込み操作を高速化する

これと3PAR SSDの動作における上記の改善により、HPは480GB、920GB、1.9TB SSDに5年間の保証を付けることができました。

保証は、起こりうる故障、電子的誤動作、工場の欠陥だけでなく、書き換えプロセス中の陳腐化も対象とすることに注意することが重要です。 。 これはHP SSDアレイ市場でのユニークなオファーです。

3年間のサポート期間で480GBおよび920GB SSDをすでに購入しているお客様の場合、サポートは自動的に5年延長されます。 アレイの他のコンポーネントのサポート-SASディスク、シェルフ、コントローラーは変更されませんでした-3年。

シンボリュームの機能強化

3PARは、ストレージシステムにシンボリュームを使用する先駆者であることを思い出させてください。 さらに、3PARは、メインCPUをロードせずに専用ASICチップ上のシンボリュームを操作することにより、システムパフォーマンスを無駄にすることなくすべてのタスクにシンボリュームを使用できるという建設的な利点があります。 同時に、着信データストリームもASICを自動的に通過し、ゼロブロックが検出されるとそれらは破棄されるため、ボリュームはシンのままです。 従来のアレイとは異なり、3PARのさまざまなアプリケーションにシンボリュームを使用する場合の推奨事項に制限はありません。 すべての3PARモデルのシンボリュームを操作するためのすべての機能(Get Thin、Start Thin、Stay Thin)のライセンスは無料で提供されます。

3PARのシンボリュームは、仮想メモリルックアップテーブルに類似した3レベルの高速ルックアップテーブルに配置されるようになりました。これにより、従来のタイプのアレイとは対照的に、高I / O負荷下で3PARのシンボリュームを使用できます。

データが3PARアレイで重複排除される場合、3レベルテーブルの同様のメカニズムが使用され、同一のハッシュ合計の検索が加速されます。

図6重複排除に3レベルのルックアップテーブルを使用する

3PARのシンボリュームテクノロジーのその他の利点は、次のとおりです。

3PAR Thin Technologiesテクニカルホワイトペーパーh20195.www2.hp.com/v2/GetPDF.aspx%2F4AA3-8987ENW.pdf

HP Thin Technologiesの比較比較h20195.www2.hp.com/v2/GetPDF.aspx%2F4AA4-4079ENW.pdf

HP 3PAR StoreServストレージ:重複排除と容量効率www8.hp.com/h20195/v2/GetDocument.aspx?docname=4AA4-9573ENW

永続ポートの機能強化

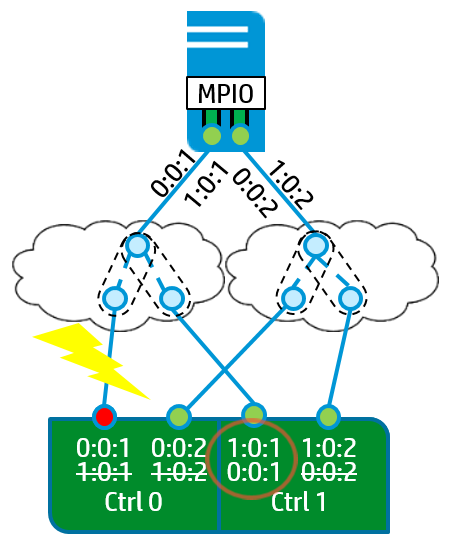

バージョン3.1.3では、Persistent Portsテクノロジーも大幅に変更され、コントローラー全体の障害だけでなく、HBA障害、光チャネルの信号損失も診断されるようになりました。 あるコントローラーから別のコントローラーへのパスの切り替え速度は約10倍低下し、ホストでMPIOメカニズムがアクティブになる前に発生します。

図7永続ポートはコントローラーによるFCパス損失を処理し、サーバーパスはオンラインのまま

適応最適化階層化の改善

3PARストレージシステムの階層型ストレージにいくつかの改善が加えられました。 特に、異なるストレージ階層間でデータブロックを移動すると、パフォーマンスパフォーマンスが低下しました。

ストレージレベルごとにデータブロックを移動するプロセスに関与するボリュームの最小IOPSしきい値を設定する機能が追加されました。 これは、ボリュームが作成された後、アプリケーションが長時間アクセスを停止した場合に当てはまります。 この場合、ブロックはNLドライブの最低ストレージレベルに自動的に下げられました。 これで、ブロックの「フリーズ」パラメーターとそのIOPSの最小値を設定できます。 各タイプのアプリケーションは、独自のティアリング構成パラメーターで構成できます。

また、階層型データストレージの作業に関する新しいレポートパラメーターを追加しました。データ領域の密度に関する一般的なレポート、各ボリュームのデータ領域の密度に関するレポート、すべてのティアリングポリシーに関する一般的なレポート(適応最適化)。

3.1.3の図8に新しいAdaptive Optimizationレポートオプションが追加されました

OpenStackサポート

OSバージョン3.1.2 MU2、3.1.3の3PARアレイは、インフラストラクチャクラウドサービスとOpenstackクラウドストレージ(ハバナ)を作成するための8番目の無料ソフトウェアリリースをサポートしています: goo.gl/hFjMl0

QoS機能の改善(Quality of Service)

待ち時間の目標を設定する機能が追加されました。 ボリュームには、高、標準、低の優先順位を設定できます。 ボリュームの1つで指定された遅延値を達成できない場合、QoSに参加している他のボリュームの遅延値は、設定された作業の優先順位に応じて変化します。

つまり 最初に、優先度が最低のボリュームの遅延パラメーターは、より高いレイテンシーに変更されます。 現在の構成で、アレイが指定の遅延インジケーターに到達できない場合、パラメーターは各ボリュームの優先度に基づいて設定されます。

ストレージシステムボリュームに提供されることが保証されている最小パフォーマンス目標(最小目標)のパラメーターを設定する機能が追加されました。

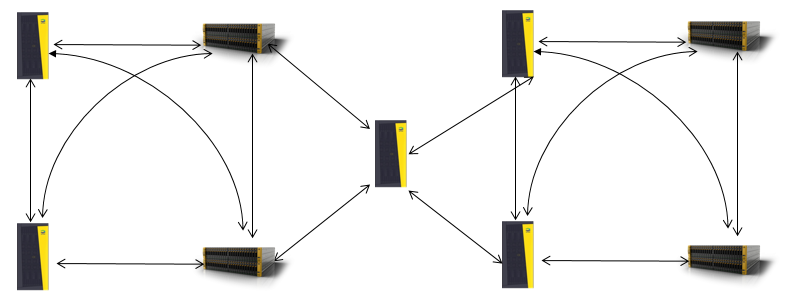

レプリケーションの改善

ファームウェアバージョン3.1.3では、3PARアレイは、1つの3PAR 7000または10,000アレイを他の3PARアレイの4つに複製する独自の機能を受け取りました。 同時に、混合タイプのチャネル(RCFC、RCIP、FCIP、およびアレイ間のさまざまなタイプのデータ交換(同期および非同期))が同時にサポートされます。

これにより、アレイを混合回路に接続できます。このモードでは、前世代のアレイ(Fクラス)がサポートされます。

図9可能な4x4レプリケーションシナリオ

この複製モードを使用すると、災害復旧をサービスとして使用できます。

この操作モードを有効にするには、追加の機器を購入したり、アレイを構成するために高度なサービスを使用したりする必要はありません;各アレイにリモートレプリケーションライセンスがあれば十分です。

HP 3PARディスクアレイは、業界で最も信頼性の高いストレージシステムの1つです。 最も要求の厳しいビジネスアプリケーションにも絶対的なデータ保護が必要です。 このため、HPは99.9999%のデータ可用性で4コントローラーHP 3PAR StoreServの信頼性の法的拘束力のある保証を含むHP 3PAR Get 6-Nines保証を発表しました。 これは、アレイのアイドル時間が1年あたり31.5秒 、 1か月あたり2.59 秒、1週間あたり0.605秒を超えないことを意味します 。 続きを読む: goo.gl/gU3Zuc

これは、ミッドレンジガートナークラスのオールフラッシュストレージシステムの機能の研究を裏付けています。 テストの結果によると、ミッドレンジのカテゴリ製品であるHP 3PAR StoreServ 7450は、すべての主要メーカーのデバイスの中で消費者の品質に関して最高のものとして認められました。 ハイエンドカテゴリでは、HP 3PAR StoreServおよびHP XPストレージシステムは、ほぼすべてのカテゴリで競合他社を上回りました。

Gartnerレポートの詳細については、次のリンクをご覧ください。

www8.hp.com/h20195/v2/GetPDF.aspx/4AA5-1876ENW.pdf

他の変更から:

仮想ストレージプロセッサがHyper-v環境で利用可能になりました。

7000および10000ストレージシステム用の直接接続銅ケーブルサポートを追加しました。

最大100mの長さのOM4光ケーブルのサポートが追加されました。 これは、10,000のストレージシステムを備えた複数のキャビネットを設置するお客様にとって興味深いかもしれません。これは、OM4 25-100mケーブルを使用して、長距離にわたってデータセンターに分散できるようになりました。

暗号化された形式でデータを保存する場合-450GB / 900GB 10kディスクおよび2TB / 4TB 7.2KのFIPS 140-2暗号化標準のサポートが追加されました。

その結果、3PAR 7450ストレージシステムの利点を、市場の他のオファーと比較してもう一度言及したいと思います。

まず、3PAR 7450アレイは、フラッシュアレイに匹敵する高いパフォーマンスを提供します。 フラッシュモジュールよりもはるかに安価なSSDドライブを使用します。 従来のストレージシステムは、時代遅れのアーキテクチャのため、高いパフォーマンスを達成できません。

第二に、3PARアレイは、フラッシュアレイのメーカーがまだ提供できない災害復旧をサポートしています。

第三に、従来のアーキテクチャのアレイと同様に、フラッシュアレイは、自動ロードバランシングを使用して4つのコントローラーに拡張することはできません。

第4に、フラッシュアレイ自体は通常、他のストレージシステムと弱く接続されているため、使用する領域が減少しますが、3PARでは、1つの管理インターフェイスとレベル間の動的なデータ移動により、1つのストレージシステムにすべてのタイプのデータを保存できます。

第5に、3PARアレイは複数のシステムからフェデレーションできますが、Flashソリューションと従来のアーキテクチャのアレイの両方ではまだ利用できません。

正しい選択をすることだけが残っています。