などなど。 この場合、I / Oポートで操作(読み取りおよび書き込み)を監視します

シーメンスSGoldラインを例として使用し、すべてがどのように機能するかを説明しようとします。

まえがき

多くの人は、このベンチャーの妥当性と有用性についてすぐに質問します。これらの電話は古くなっているためです。

最初に、電話機をARM926EJ-Sベースのマイクロコントローラを備えたデバイス(ドキュメンテーションなし)と見なし 、取得したデータを使用してニーズに合わせて独自のファームウェアを作成します。 第二に、科学的関心!

理論

先生、私たちは何を持っていますか? そして、

I / Oポート

前述したように、そこにはいくつかのデバイスとインターフェースがあります。 また、4ギガバイト(32ビット)のアドレス空間では、独自の範囲が与えられます。 はい、マイクロコントローラのアドレス空間は物理的に次のように分割されています。

0x00000000-0x00003FFF -SRAM#1

0x00080000-0x00097FFF -SRAM#2

0x00400000-0x0040FFFF -BootROM

0xF0000000-0xFFFFFFFF -I / Oポート、組み込みデバイスのレジスタ

また、悪名高いEBUを使用して、外部RAMとROMを空き物理アドレスに挿入できます。

したがって、たとえば、 USART0デバイスの場合、範囲F1000000〜F1000084が割り当てられます。

次のような稼働状態にあるようです。

この範囲の各WORD ( ARMでは4バイト)は、このインターフェイスを制御するためのレジスタです。

つまり、特定の値を特定のレジスタに書き込むことにより、コマンドまたはデータをデバイスに転送し、

そしてそれらから読み取り、データを取得してステータスを確認します。

USART0 (Universal Synchronous Asynchronous Receiver and Transmitter)がケーブルの送信機および受信機として使用されることを忘れていました。大まかに言えば、 COMポートですが、低電圧です。

そして、最も単純なケースで1バイトを転送するプロセスを詳しく見てみましょう。

#define USART_REG(a) * ( (unsigned int *) ( a ) ) #define USART0_BASE 0xF1000000 #define USART0_CLC USART0_BASE /* Clock Control Register */ #define USART0_ID USART0_BASE + 0x08 /* Module Identification Register */ #define USART0_CON USART0_BASE + 0x10 /* Control Register */ #define USART0_BG USART0_BASE + 0x14 /* Baudrate Timer Reload Register */ #define USART0_FDV USART0_BASE + 0x18 /* Fractional Divider Register */ #define USART0_TXB USART0_BASE + 0x20 /* Transmit Buffer */ #define USART0_RXB USART0_BASE + 0x24 /* Receive Buffer */ #define USART0_FCSTAT USART0_BASE + 0x68 /* Flowcontrol status register */ #define USART0_ICR USART0_BASE + 0x70 void USART0_InitAndTransmit() { unsigned char tx = 0xDD; // USART_REG(USART0_CLC) = 0x200; // USART_REG(USART0_BG) = 0x05; USART_REG(USART0_FDV) = 0xDA; // USART_REG(USART0_CON) = 0x8811; // USART_REG(USART0_TXB) = tx & 0xFF; // while(!(USART_REG(USART0_FCSTAT) & 2)); // USART_REG(USART0_ICR) = (USART_REG(USART0_ICR)) | 0x02; }

さて、つまり、デバイスに何かを転送するには、これらのいまいましいレジスタに書き込み、それらから読み取る必要があります。これを傍受に使用します。

MMUとリダイレクトテーブル

MMUは、メモリとアドレス空間を管理するためのマイクロコントローラー内のデバイスです。 含まれている場合と含まれていない場合がありますが、機能し、さまざまなメモリ領域にアクセスモードを設定します。最も興味深いのは、アドレスをリダイレクトまたはミラーリングできることです。

物理アドレスなどについて話し始めましたが、 MMUを使用して作成できる仮想アドレスがまだあります。

4ギガバイトのアドレス空間はすべて、小さなリダイレクトプレートに書き込まれます。

転送テーブルは、通常はSRAMのメモリの一部であり、 4096 MBのアドレス空間を記述します。 また、 WORDのサイズの各セルは1 MBを表します。 簡単な計算で、そのサイズ-16 Kbを見つけることができます。 テーブルの第2レベルはまだありますが、荒野に登らないでください。これは必要ありません。 したがって、最初からのセル位置は、物理アドレスについてMMUに通知し、

これは仮想に変換する必要があり、その値は仮想に書き込まれます。 セルは、キャッシュ、バッファー、アクセスモードの1 MBでこのスペースの属性も記述します。 セルが空、つまり0x00000000 (つまり、少なくとも可用性に関与するビット)である場合、セルが記述するアドレスは存在せず、プロセッサには表示されません。

そのようなテーブルの例を理解するには:

| セルアドレス | 価値 | 説明 |

|---|---|---|

| 0x0000 | 0x00000C12 | 0x00000000-0x000FFFFF / RW / Nekeshirについて説明します。 ネブフ。 |

| 0x0004 | 0x00100C12 | 0x00100000-0x001FFFFF / RW / Nekeshirについて説明します。 ネブフ。 |

| 0x0008 | 0x00200C12 | 0x00200000-0x002FFFFF / RW / Nekeshirについて説明します。 ネブフ。 |

| 0x000C | 0x00300C12 | 0x00300000-0x003FFFFF / RW / Nekeshirについて説明します。 ネブフ。 |

| 0x0010 | 0x00400C12 | 0x00400000-0x004FFFFF / RW / Nekeshirについて説明します。 ネブフ。 |

| ..... | ||

| 0x3840 | 0xF1000C12 | 0xF1000000-0xF10FFFFFから0xE1000000-0xE10FFFFFへのミラーリング |

| ..... | ||

| 0x3C40 | 0xF1000C12 | 0xF1000000-0xF10FFFFF / RW / Nekeshirについて説明します。 ネブフ。 |

| ..... | ||

| 0xFFFC | 0x00000000 | プロセッサはアドレス0xFFF00000-0xFFFFFFFFを認識しません |

そして、はい、このテーブルを自分自身で、 RAMまたはFlashの任意のセクションで、そしてMMUがそれについて知るために、 CP15コプロセッサーレジスタにアドレスを登録する必要がありますが、これは重要ではありません。

割り込みベクトル

割り込みは、ハードウェア(デバイスから)、ソフトウェア(特別な命令BKPTおよびSWIを使用 )、およびエラー(例外)からのものです。

割り込みの結果、奇妙なことに、プロセッサは現在のアドレスで命令の実行を中断し、割り込みの種類に応じて、いわゆる割り込みベクター、つまり特定のアドレスに切り替えます。 そして、この割り込み/例外のハンドラーへの遷移のための命令が通常配置されます。

これらのベクトルを検討してください。

| 下位アドレス | 上位アドレス | ベクトル | 説明 |

|---|---|---|---|

| 0x00000000 | 0xFFFF0000 | リセットする | リセットする |

| 0x00000004 | 0xFFFF0004 | Undefined_instruction | 不明な指示 |

| 0x00000008 | 0xFFFF0008 | スイ | ソフトウェア割り込み |

| 0x0000000C | 0xFFFF000C | Prefetch_abort | コマンド読み取りエラー |

| 0x00000010 | 0xFFFF0010 | Data_abort | データアクセスが拒否されました |

| 0x00000014 | 0xFFFF0014 | 予約済み | 予約済み |

| 0x00000018 | 0xFFFF0018 | IRQ | 鉄の中断 |

| 0x0000001C | 0xFFFF001C | FIQ | 鉄の中断 |

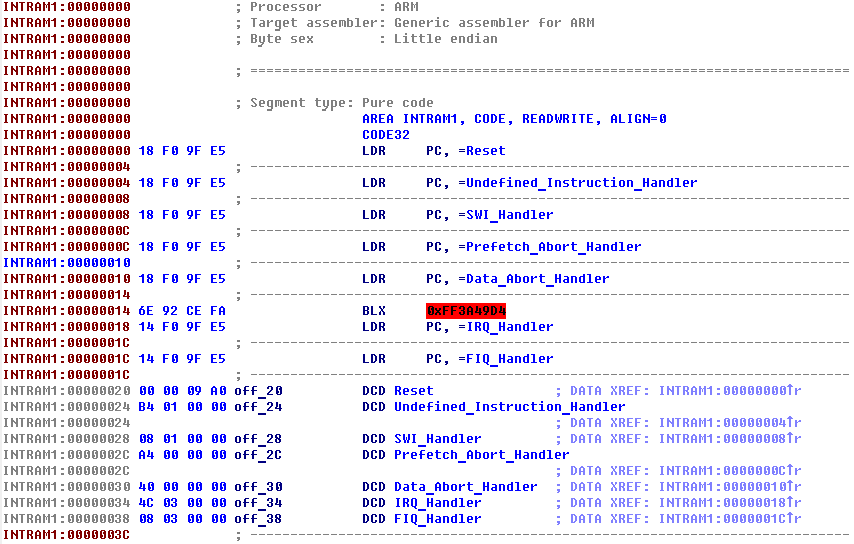

シーメンスSGoldでは 、次のようになります。

ただし、1つのデータ中止ベクトルにのみ関心があります。 この割り込みは、プロセッサがコミットしようとしたときに発生します。

存在しないアドレスまたは現在アクセスできないアドレスからの読み取り/書き込み操作。

Siemens SGoldファームウェアは、このベクトルを単にエラー登録として使用し、特徴的な音でデバイスをシャットダウンします。

つまり、ポインターが0x00000030にあるハンドラーは、独自のものに安全に置き換えることができます。

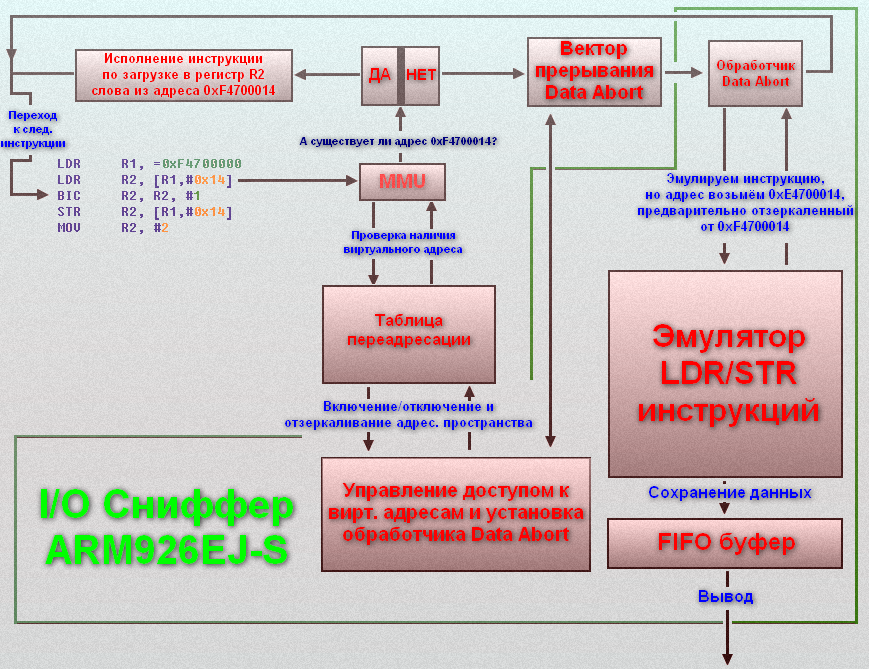

読み取り/書き込み追跡メカニズム

速度が上がったので、このfigovinaの動作を検討できます。

記事の最初の図に目を向けましょう。この言葉、ブロック図を恐れません。

ARM-アセンブラコードを見てください(その意味や完全性を探さないでください)。

LDR R1, =0xF4700000 ; R1 0xF4700000 LDR R2, [R1, #0x14] ; R2 R1 + 0x14 ( 0xF4700014) BIC R2, R2, #1 ; 0- R2 STR R2, [R1, #0x14] ; R2 R1 + 0x14 ( 0xF4700014) MOV R2, #2 ; R2 2

最も興味深い部分は、指示から始まります。

LDR R2, [R1, #0x14] ; R2 R1 + 0x14 ( 0xF4700014)

ここで、プロセッサは最初にMMUに尋ねます:「アドレス0xF4700014は存在し、そこにアクセスできますか?」

MMUは「はい」と言い、プロセッサはアドレスからコンテンツを読み取り、引き続き動作します。

Data Abort例外ハンドラーを独自のものに置き換えます;このためには、アドレス0x00000030のポインターを変更するだけです。

リダイレクトテーブルを介して、アドレススペース0xF4700000-0xF47FFFFFを0xE4700000-0xE47FFFFFにミラーリングします 。

元のアドレスをそこに消去します。 0xF4700014は存在しないことがわかります。つまり、プロセッサはそれを認識しませんが、

0xE4700014-物理アドレス0xF4700014から変換(ミラーリング)されました。

私たちはコードを繰り返し、プロセッサーはまさにその命令につまずき、アドレスの存在について尋ね、そしてあなたに挨拶します、いいえ!

パニック。 そのような場合、プロセッサは割り込みベクトルにジャンプしてどこに到達しますか? そうです、ハンドラーです。 中断されたプログラムのコンテキストを慎重に保存し、何も失われないようにします。

次に、この命令のエミュレーションがありますが、アドレスがないことを考慮して、代わりに0xE4700014を取る必要があります。

エミュレーションでは、命令の場所を決定し、実行すべきことを分析し、実際にすべてを実行し、コンテキストに適用します(保存したことを思い出してください)、操作に関するすべてのデータを書き留めます(命令アドレス、レジスタアドレス、値、および操作の種類) -決して落ち着いて復元し、プロセッサを次の命令に誘導します。

ファームウェアがアドレス0xF4700000-0xF47FFFFFで操作を実行する場合、それは必然的にハンドラーに到達し、順番に、これらの操作のログを定期的に保持します。 美しさは同じです! 確かに、1つの命令ではなく、巨大なハンドラーを実行する必要がありますが、パフォーマンスとパフォーマンスにはほとんど影響しません。

メカニズムの実装

これらすべての実装はプラットフォームに大きく依存しており、このコードは誰にも何も与えないと思います。

しかし、それなしでは何とか奇妙なものになります。 すべてがIAR 4.2環境で開発されました

arm_defs.h

#ifndef __ARM_DEFS_H__ #define __ARM_DEFS_H__ #define WORD(a) * ( (unsigned int *) ( a ) ) #define HWRD(a) * ( (unsigned short *) ( a ) ) #define BYTE(a) * ( (unsigned char *) ( a ) ) #define INS_BIT(i,b) ( ( i >> b )&1 ) #define I32_FIELD(i,b,e) ( ( ( i << ( 31 - b ) ) >> 31 - b ) >> ( e ) ) #define I32_FIELD_FAST(i,e,m) ( ( i >> e ) & m ) #define IARM_COND(i) ( ( i >> 28 )&0xF ) #define IARM_Rn(i) ( ( i >> 16 )&0xF ) #define IARM_Rd(i) ( ( i >> 12 )&0xF ) #define IARM_Rs(i) ( ( i >> 8 )&0xF ) #define IARM_Rm(i) ( ( i >> 0 )&0xF ) #define IARM_ImmHi(i) ( ( i >> 16 )&0xF ) #define IARM_ImmLo(i) ( ( i >> 0 )&0xF ) #define IARM_Imm12(i) ( ( i >> 0 )&0xFFF ) #define IARM_ShiftImm(i) I32_FIELD_FAST(i,7,0x1F) #define IARM_Shift(i) I32_FIELD_FAST(i,5,3) #define IARM_Shift_LSL 0 #define IARM_Shift_LSR 1 #define PC_ALIGN(pc) (pc & 0xFFFFFFFE) #define MAX_REGS 17 #define _R0 0 #define _R1 1 #define _R2 2 #define _R3 3 #define _R4 4 #define _R5 5 #define _R6 6 #define _R7 7 #define _R8 8 #define _R9 9 #define _R10 10 #define _R11 11 #define _R12 12 #define _SP 13 #define _LR 14 #define _PC 15 #define _CPSR 16 #define GET_PSR_N(cpsr) ((cpsr >> 31)&1) #define GET_PSR_Z(cpsr) ((cpsr >> 30)&1) #define GET_PSR_C(cpsr) ((cpsr >> 29)&1) #define GET_PSR_V(cpsr) ((cpsr >> 28)&1) #define GET_PSR_Q(cpsr) ((cpsr >> 27)&1) #define GET_PSR_I(cpsr) ((cpsr >> 7)&1) #define GET_PSR_F(cpsr) ((cpsr >> 6)&1) #define GET_PSR_T(cpsr) ((cpsr >> 5)&1) #define GET_PSR_M(cpsr) ((cpsr)&0x1F) #define SET_PSR_T(cpsr, i) (cpsr |= ( i << 5)) #define MUSR 0x10 // User Mode #define MFIQ 0x11 // FIQ Mode #define MIRQ 0x12 // IRQ Mode #define MSVC 0x13 // Supervisor Mode #define MABT 0x17 // Abort Mode #define MUND 0x1B // Undefined Mode #define MSYS 0x1F // System Mode #define MMSK 0x1F // Mask Mode #define CEQ 0 // : Z == 1 #define CNE 1 // : Z == 0 #define CCS 2 // : C == 1 #define CHS 2 // : C == 1 #define CCC 3 // : C == 0 #define CLO 3 // : C == 0 #define CMI 4 // /: N == 1 #define CPL 5 // / : N == 0 #define CVS 6 // : V == 1 #define CVC 7 // : V == 0 #define CHI 8 // : C == 1 && Z == 0 #define CLS 9 // : C == 0 && Z == 1 #define CGE 10 // , : N == V #define CLT 11 // , : N != V #define CGT 12 // , : Z == 0 && N == V #define CLE 13 // , : Z == 1 && N != V #define CAL 14 // #define CMSK 15 // // LDR / STR #define IARM_IS_LDR(i) \ ( I32_FIELD_FAST(i,26,3)==1 && INS_BIT(i,22)==0 && INS_BIT(i,20)==1 ) #define IARM_IS_STR(i) \ ( I32_FIELD_FAST(i,26,3)==1 && INS_BIT(i,22)==0 && INS_BIT(i,20)==0 ) #define IARM_LDR_I(i) INS_BIT(i,25) #define IARM_LDR_P(i) INS_BIT(i,24) #define IARM_LDR_U(i) INS_BIT(i,23) #define IARM_LDR_W(i) INS_BIT(i,21) // if Load and Store word or unsigned byte instructions #define IARM_IS_LDRHS(i) ( (i >> 25)&7 == 0 && (i >> 7)&1 == 1 && (i >> 4)&1 == 1 ) #define IARM_LDRHS_P(i) INS_BIT(i,24) #define IARM_LDRHS_U(i) INS_BIT(i,23) #define IARM_LDRHS_I(i) INS_BIT(i,22) #define IARM_LDRHS_W(i) INS_BIT(i,21) #define IARM_LDRHS_L(i) INS_BIT(i,20) #define IARM_LDRHS_S(i) INS_BIT(i, 6) #define IARM_LDRHS_H(i) INS_BIT(i, 5) /* THUMBs command detector Load / Store */ // PC-relative load #define ITHUMB_LS_PCREL(i) (((i >> 11) & 0x1F) == 0x09) #define ITHUMB_LS_PCREL_Rd(i) ((i >> 8) & 0x07) #define ITHUMB_LS_PCREL_Offset(i) (i & 0xF) // load/store with register offset #define ITHUMB_LS_WITHREGOFFSET(i) (((i >> 9) &(~0x06)) == 0x28) #define ITHUMB_LS_WITHREGOFFSET_Ro(i) ((i >> 6) & 0x07) #define ITHUMB_LS_WITHREGOFFSET_Rb(i) ((i >> 3) & 0x07) #define ITHUMB_LS_WITHREGOFFSET_Rd(i) ((i >> 0) & 0x07) #define ITHUMB_LS_WITHREGOFFSET_L(i) ((i >> 11) & 0x01) #define ITHUMB_LS_WITHREGOFFSET_B(i) ((i >> 10) & 0x01) // load/store sign-extended byte/halfword #define ITHUMB_LS_SIGNEXTBYTEHWRD(i) (((i >> 9) &(~0x06)) == 0x29) #define ITHUMB_LS_SIGNEXTBYTEHWRD_Ro(i) ((i >> 6) & 0x07) #define ITHUMB_LS_SIGNEXTBYTEHWRD_Rb(i) ((i >> 3) & 0x07) #define ITHUMB_LS_SIGNEXTBYTEHWRD_Rd(i) ((i >> 0) & 0x07) #define ITHUMB_LS_SIGNEXTBYTEHWRD_H(i) ((i >> 11) & 0x01) #define ITHUMB_LS_SIGNEXTBYTEHWRD_S(i) ((i >> 10) & 0x01) // load/store with immediate offset #define ITHUMB_LS_WITHIMMOFFSET(i) (((i >> 11) &(~0x03)) == 0x0C) #define ITHUMB_LS_WITHIMMOFFSET_L(i) ((i >> 11) & 0x01) #define ITHUMB_LS_WITHIMMOFFSET_B(i) ((i >> 12) & 0x01) #define ITHUMB_LS_WITHIMMOFFSET_Rb(i) ((i >> 3) & 0x07) #define ITHUMB_LS_WITHIMMOFFSET_Rd(i) ((i >> 0) & 0x07) #define ITHUMB_LS_WITHIMMOFFSET_Offset(i) ((i >> 6) & 0x1F) // load/store halfword #define ITHUMB_LS_HWRD(i) (((i >> 11) & (~0x01)) == 0x10) #define ITHUMB_LS_HWRD_L(i) ((i >> 11) & 0x01) #define ITHUMB_LS_HWRD_Rb(i) ((i >> 3) & 0x07) #define ITHUMB_LS_HWRD_Rd(i) ((i >> 0) & 0x07) #define ITHUMB_LS_HWRD_Offset(i) ((i >> 6) & 0x1F) // SP-relative load/store #define ITHUMB_LS_SPREL(i) (((i >> 12) & 0x0F) == 0x09) #define ITHUMB_LS_SPREL_L(i) ((i >> 11) & 0x01) #define ITHUMB_LS_SPREL_Rd(i) ((i >> 8) & 0x07) #define ITHUMB_LS_SPREL_Offset(i) (i & 0xF) #endif // __ARM_DEFS_H__

sniffer.h

#ifndef __SNIFFER_H__ #define __SNIFFER_H__ #include "arm_defs.h" extern void da_handler(); #define IO_ADDRESS 0xF0000000 #define IO_ADDRESS_MIRROR 0xE0000000 #define IO_ADDRESS_DIF 0x10000000 #define VECTOR_DATAABORT_JUMPER 0xE59FF018 #define VECTOR_DATAABORT_JUMPER_OFS 0x10 #define VECTOR_DATAABORT_HANDLER_OFS 0x30 #define MMU_ATTR 0xC12 #define MMU_TABLE 0x00090000 #define MMU_GRID(a) * ( (unsigned int *) ( (MMU_TABLE + ((a >> 20) & 0xFFF) * 4) ) ) #define MMU_GRID_MIRROR(a) MMU_GRID(a - IO_ADDRESS_DIF) #define MMU_GRID_SETATTR(a) ((a & 0xFFF00000) | MMU_ATTR) typedef struct { unsigned int r0; unsigned int r1; unsigned int r2; unsigned int r3; unsigned int r4; unsigned int r5; unsigned int r6; unsigned int r7; unsigned int r8; unsigned int r9; unsigned int r10; unsigned int r11; unsigned int r12; unsigned int sp; unsigned int lr; unsigned int pc; unsigned int cpsr; }REGISTERS; typedef struct { union regs { unsigned int a[MAX_REGS]; REGISTERS s; }; }CONTEXT; void io_sniffer_init(void (*sniff_prc)(unsigned int address, unsigned int value, unsigned int pc, char is_ldr)); void io_sniffer_deinit(); int io_sniffer_add(unsigned int io_address); int io_sniffer_remove(unsigned int io_address); #endif // __SNIFFER_H__

system.h

#ifndef __SYSTEM_H__ #define __SYSTEM_H__ __arm void SetDomainAccess(unsigned int domains); __arm void SetMemoryAccess(unsigned int domains); __arm void UnlockAllMemoryAccess(); __arm void DisableInterrupt(); __arm void EnableInterrupt(); __arm void EnableModeForOSWork(); __arm void DisableModeForOSWork(); #endif // __SYSTEM_H__

da_handler.asm

#include "arm_defs.h" EXTERN context EXTERN abt_stack EXTERN emualate_ldr_str CODE32 ARM RSEG CODE:CODE PUBLIC da_handler da_handler: // R0 - R12 LDR SP, =context STMIA SP, {R0-R12} // LDR SP, =abt_stack ADD SP, SP, #0x4000 // CPSR MRS R1, SPSR LDR R0, =context STR R1, [R0, #_CPSR*4] // PC SUB LR, LR, #0x08 STR LR, [R0, #_PC*4] // AND R2, R1, #MMSK CMP R2, #MUSR // USR, SYS MOVEQ R2, #MSYS // MRS R1, CPSR BIC R1, R1, #MMSK ORR R1, R1, R2 MSR CPSR_c, R1 // SP LR STR SP, [R0, #_SP*4] STR LR, [R0, #_LR*4] // , // ABT BIC R1, R1, #MMSK ORR R1, R1, #MABT MSR CPSR_c, R1 BL emualate_ldr_str // CPSR LDR R0, =context LDR R1, [R0, #_CPSR*4] MSR SPSR_cxsf, R1 // AND R2, R1, #MMSK CMP R2, #MUSR // USR, SYS MOVEQ R2, #MSYS // MRS R1, CPSR BIC R1, R1, #MMSK ORR R1, R1, R2 MSR CPSR_c, R1 // SP LR LDR SP, [R0, #_SP*4] LDR LR, [R0, #_LR*4] // ABT BIC R1, R1, #MMSK ORR R1, R1, #MABT MSR CPSR_c, R1 // PC LDR SP, =context LDR LR, [SP, #_PC*4] // R0-R12 LDMIA SP, {R0-R12} // // MOVS PC, LR END

sniffer.c

#include "sniffer.h" #include "system.h" CONTEXT context; unsigned char abt_stack[0x4000]; unsigned char sniffer_map[0x100]; unsigned int da_jumper = 0; unsigned int da_address = 0; void (*sniff_p)(unsigned int address, unsigned int value, unsigned int pc, char is_ldr) = 0; __arm void sniff_proc(unsigned int address, unsigned int value, unsigned int pc, char is_ldr) { if (sniff_p) sniff_p(address, value, pc, is_ldr); } __arm int emualate_ldr_str_sub(CONTEXT *context) { unsigned int cpsr; unsigned int instruction; unsigned int address; //unsigned char cond; char i, l, b, h, w, s, u, p; char rn, rd, rm; cpsr = context->s.cpsr; // ARM if (!GET_PSR_T(cpsr)) { // instruction = WORD(context->s.pc); // //cond = IARM_COND(instruction); // (LDR) if (IARM_IS_LDR(instruction)) { p = IARM_LDR_P(instruction); i = IARM_LDR_I(instruction); u = IARM_LDR_U(instruction); w = IARM_LDR_W(instruction); rn = IARM_Rn(instruction); rd = IARM_Rd(instruction); rm = IARM_Rm(instruction); int sign; unsigned int index; // if (!i) index = IARM_Imm12(instruction); // else { // if (!IARM_ShiftImm(instruction) && !IARM_Shift(instruction)) index = context->a[rm]; // else { // unsigned short si = IARM_ShiftImm(instruction); // unsigned short st = IARM_Shift(instruction); switch(st) { case IARM_Shift_LSL: index = context->a[rm] << si; break; case IARM_Shift_LSR: if (si) { index = 0; break; } else { index = context->a[rm] >> si; break; } } } } // if (u) sign = 1; // else sign = -1; // - if (!p) { address = context->a[rn]; context->a[rn] = address + index*sign; context->a[rd] = WORD(address - IO_ADDRESS_DIF); // sniff_proc(address, context->a[rd], context->s.pc, 1); } else { // - if (w) { address = context->a[rn] + index*sign; context->a[rn] = address; context->a[rd] = WORD(address - IO_ADDRESS_DIF); // sniff_proc(address, context->a[rd], context->s.pc, 1); } // /- else { address = context->a[rn] + index*sign; context->a[rd] = WORD(address - IO_ADDRESS_DIF); // sniff_proc(address, context->a[rd], context->s.pc, 1); } } } // (STR) else if (IARM_IS_STR(instruction)) { p = IARM_LDR_P(instruction); i = IARM_LDR_I(instruction); u = IARM_LDR_U(instruction); w = IARM_LDR_W(instruction); rn = IARM_Rn(instruction); rd = IARM_Rd(instruction); rm = IARM_Rm(instruction); int sign; unsigned int index; // if (!i) index = IARM_Imm12(instruction); // else { // if (!IARM_ShiftImm(instruction) && !IARM_Shift(instruction)) index = context->a[rm]; // else { // unsigned short si = IARM_ShiftImm(instruction); // unsigned short st = IARM_Shift(instruction); switch(st) { case IARM_Shift_LSL: index = context->a[rm] << si; break; case IARM_Shift_LSR: if (si) { index = 0; break; } else { index = context->a[rm] >> si; break; } } } } // if (u) sign = 1; // else sign = -1; // - if (!p) { address = context->a[rn]; context->a[rn] = address + index*sign; WORD(address - IO_ADDRESS_DIF) = context->a[rd]; // sniff_proc(address, context->a[rd], context->s.pc, 0); } else { // - if (w) { address = context->a[rn] + index*sign; context->a[rn] = address; WORD(address - IO_ADDRESS_DIF) = context->a[rd]; // sniff_proc(address, context->a[rd], context->s.pc, 0); } // /- else { address = context->a[rn] + index*sign;; WORD(address - IO_ADDRESS_DIF) = context->a[rd]; // sniff_proc(address, context->a[rd], context->s.pc, 0); } } } context->s.pc += 4; return 1; } else // THUMB { // instruction = HWRD(context->s.pc); if (ITHUMB_LS_WITHREGOFFSET(instruction)) { rd = ITHUMB_LS_WITHREGOFFSET_Rd(instruction); l = ITHUMB_LS_WITHREGOFFSET_L(instruction); b = ITHUMB_LS_WITHREGOFFSET_B(instruction); // if (l) { // if (b) context->a[rd] = BYTE(address - IO_ADDRESS_DIF); else // context->a[rd] = WORD(address - IO_ADDRESS_DIF); // sniff_proc(address, context->a[rd], context->s.pc, 1); } // else { // if (b) BYTE(address - IO_ADDRESS_DIF) = context->a[rd]; else // WORD(address - IO_ADDRESS_DIF) = context->a[rd]; // sniff_proc(address, context->a[rd], context->s.pc, 0); } } else if (ITHUMB_LS_SIGNEXTBYTEHWRD(instruction)) { address = context->a[ITHUMB_LS_SIGNEXTBYTEHWRD_Rb(instruction)] + context->a[ITHUMB_LS_SIGNEXTBYTEHWRD_Ro(instruction)]; rd = ITHUMB_LS_SIGNEXTBYTEHWRD_Rd(instruction); h = ITHUMB_LS_SIGNEXTBYTEHWRD_H(instruction); s = ITHUMB_LS_SIGNEXTBYTEHWRD_S(instruction); // if (!h && !s) { HWRD(address - IO_ADDRESS_DIF) = context->a[rd]; // sniff_proc(address, context->a[rd], context->s.pc, 0); // } else if (h && !s) { context->a[rd] = HWRD(address - IO_ADDRESS_DIF); // sniff_proc(address, context->a[rd], context->s.pc, 1); // } else if (!h && s) { context->a[rd] = BYTE(address - IO_ADDRESS_DIF); if (INS_BIT(context->a[rd], 7)) context->a[rd] |= 0xFFFFFF00; // sniff_proc(address, context->a[rd], context->s.pc, 1); // } else if (h && s) { context->a[rd] = HWRD(address - IO_ADDRESS_DIF); if (INS_BIT(context->a[rd], 15)) context->a[rd] |= 0xFFFF0000; // sniff_proc(address, context->a[rd], context->s.pc, 1); } } else if (ITHUMB_LS_WITHIMMOFFSET(instruction)) { rd = ITHUMB_LS_WITHIMMOFFSET_Rd(instruction); l = ITHUMB_LS_WITHIMMOFFSET_L(instruction); b = ITHUMB_LS_WITHIMMOFFSET_B(instruction); if (b) address = context->a[ITHUMB_LS_WITHIMMOFFSET_Rb(instruction)] + ITHUMB_LS_WITHIMMOFFSET_Offset(instruction); else address = context->a[ITHUMB_LS_WITHIMMOFFSET_Rb(instruction)] + (ITHUMB_LS_WITHIMMOFFSET_Offset(instruction) << 2); // if (l) { // if (b) context->a[rd] = BYTE(address - IO_ADDRESS_DIF); else // context->a[rd] = WORD(address - IO_ADDRESS_DIF); // sniff_proc(address, context->a[rd], context->s.pc, 1); } // else { // if (b) BYTE(address - IO_ADDRESS_DIF) = context->a[rd]; else // WORD(address - IO_ADDRESS_DIF) = context->a[rd]; // sniff_proc(address, context->a[rd], context->s.pc, 0); } } else if (ITHUMB_LS_HWRD(instruction)) { rd = ITHUMB_LS_HWRD_Rd(instruction); l = ITHUMB_LS_HWRD_L(instruction); address = context->a[ITHUMB_LS_HWRD_Rb(instruction)] + (ITHUMB_LS_HWRD_Offset(instruction) << 1); // if (l) context->a[rd] = HWRD(address - IO_ADDRESS_DIF); // else HWRD(address - IO_ADDRESS_DIF) = context->a[rd]; // sniff_proc(address, context->a[rd], context->s.pc, l); } else if (ITHUMB_LS_SPREL(instruction)) { address = context->s.sp + (ITHUMB_LS_SPREL_Offset(instruction) << 2); rd = ITHUMB_LS_SPREL_Rd(instruction); l = ITHUMB_LS_SPREL_L(instruction); // if (l) context->a[rd] = WORD(address - IO_ADDRESS_DIF); else // WORD(address - IO_ADDRESS_DIF) = context->a[rd]; // sniff_proc(address, context->a[rd], context->s.pc, l); } context->s.pc += 2; return 1; } } __arm void emualate_ldr_str(CONTEXT *context) { SetDomainAccess(0xFFFFFFFF); emualate_ldr_str_sub(context); SetDomainAccess(1); } void io_sniffer_init(void (*sniff_prc)(unsigned int address, unsigned int value, unsigned int pc, char is_ldr)) { if (sniff_prc) { UnlockAllMemoryAccess(); da_jumper = WORD(VECTOR_DATAABORT_JUMPER_OFS); da_address = WORD(VECTOR_DATAABORT_HANDLER_OFS); WORD(VECTOR_DATAABORT_JUMPER_OFS) = VECTOR_DATAABORT_JUMPER; WORD(VECTOR_DATAABORT_HANDLER_OFS) = (int)&da_handler; SetMemoryAccess(1); sniff_p = sniff_prc; for (int i = 0; i < 0x100; i++) sniffer_map[i] = 0; } } void io_sniffer_deinit() { UnlockAllMemoryAccess(); da_jumper = WORD(VECTOR_DATAABORT_JUMPER_OFS); da_address = WORD(VECTOR_DATAABORT_HANDLER_OFS); WORD(VECTOR_DATAABORT_JUMPER_OFS) = (unsigned int)&da_jumper; WORD(VECTOR_DATAABORT_HANDLER_OFS) = (unsigned int)&da_address; for (int i = 0; i < 0x100; i++) { if (sniffer_map[i]) { unsigned int io_address = IO_ADDRESS | (i << 20) | MMU_ATTR; MMU_GRID(io_address) = MMU_GRID_SETATTR(io_address); MMU_GRID_MIRROR(io_address) = 0x00000000; } sniffer_map[i] = 0; } SetMemoryAccess(1); sniff_p = 0; } int io_sniffer_add(unsigned int io_address) { if ((io_address >> 28) == 0x0F) { unsigned char sm = (io_address >> 20) & 0x0FF; if (!sniffer_map[sm]) { UnlockAllMemoryAccess(); MMU_GRID(io_address) = 0x00000000; MMU_GRID_MIRROR(io_address) = MMU_GRID_SETATTR(io_address); SetMemoryAccess(1); sniffer_map[sm] = 1; return 1; } } return 0; } int io_sniffer_remove(unsigned int io_address) { if ((io_address >> 28) == 0x0F) { unsigned char sm = (io_address >> 20) & 0x0FF; if (sniffer_map[sm]) { UnlockAllMemoryAccess(); MMU_GRID(io_address) = MMU_GRID_SETATTR(io_address); MMU_GRID_MIRROR(io_address) = 0x00000000; SetMemoryAccess(1); sniffer_map[sm] = 0; return 1; } } return 0; }

system.c

#include "system.h" #include "intrinsics.h" #pragma swi_number=0x00 __swi __arm void system_mode_sg(); #pragma swi_number=0x04 __swi __arm void system_mode_nsg(); #pragma swi_number=0x81B5 __swi __arm int is_nsg(); __arm void SetDomainAccess(unsigned int domains) { __MCR(15, 0, domains, 3, 0, 0); for (int i = 0; i < 20; i++); } __arm void SetMemoryAccess(unsigned int domains) { if (is_nsg()) system_mode_nsg(); else system_mode_sg(); __disable_interrupt(); SetDomainAccess(domains); __enable_interrupt(); } __arm void UnlockAllMemoryAccess() { if (is_nsg()) system_mode_nsg(); else system_mode_sg(); __disable_interrupt(); SetDomainAccess(0xFFFFFFFF); __enable_interrupt(); } __arm void DisableInterrupt() { if (is_nsg()) system_mode_nsg(); else system_mode_sg(); __disable_interrupt(); } __arm void EnableInterrupt() { if (is_nsg()) system_mode_nsg(); else system_mode_sg(); __enable_interrupt(); } unsigned long cpsr = 0; __arm void EnableModeForOSWork() { cpsr = __get_CPSR(); cpsr &= 0xC0; cpsr |= 0x1F; __set_CPSR(cpsr); } __arm void DisableModeForOSWork() { if (cpsr) __set_CPSR(cpsr); cpsr = 0; }

結果

最後に、このスニファーを使用して最終的に何が起こったのかを説明します。

実行可能ファイルio_sniffer.elfが電話にドロップされ、起動します。I2Cインターフェース(0xF4800000)で

操作をキャッチするようにスニファーをセットアップします。ハンドラーに加えて、ケーブルを介してすべてをリアルタイムでコンピューターに転送する特別なタスク(スレッド、スレッド)があり、データを受信してウィンドウに表示するプログラムがあります。電話のボタンを押すと、スピーカーがクリック音を発します(電話の設定でオンになります)。これはI2Cバス経由で交換されるDialogデバイスの結果です

マイクロコントローラ付き。そして理論的には、ファームウェアがこれを実行し、

このデバイスが次のようにサウンドを合成することを確認する必要があります。

I2C:キークリック

0xA07EE064|I2C |CLC |0xF4800000||0x00000100| 0xA07EE06C|I2C |BUSCON |0xF4800014||0xA0007E11| 0xA07EE070|I2C |SYSCON |0xF4800010||0x00880000| 0xA07EE07C|I2C |SYSCON |0xF4800010||0x00880000| 0xA089550C|I2C |ICR |0xF48000FC||0x00000000| 0xA0895514|I2C |ICR |0xF48000FC||0x00004000| 0xA0895518|I2C |ICR |0xF48000FC||0x00000000| 0xA0895520|I2C |ICR |0xF48000FC||0x00001000| 0xA0895868|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895878|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895888|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895938|I2C |RTB |0xF4800018||0x00001262| 0xA0895940|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895950|I2C |SYSCON |0xF4800010||0x04880000| 0xA0895964|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA0895970|I2C |WHBSYSCON|0xF4800020||0x00100000| 0xA0895540|I2C |ICR |0xF48000FC||0x00003000| 0xA0895548|I2C |ICR |0xF48000FC||0x00007000| 0xA0895374|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895388|I2C |SYSCON |0xF4800010||0x04980230| 0xA089539C|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895420|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895438|I2C |SYSCON |0xF4800010||0x00980230| 0xA0895444|I2C |RTB |0xF4800018||0x00000010| 0xA0895540|I2C |ICR |0xF48000FC||0x00003000| 0xA0895548|I2C |ICR |0xF48000FC||0x00007000| 0xA0895374|I2C |SYSCON |0xF4800010||0x00980130| 0xA0895388|I2C |SYSCON |0xF4800010||0x00980130| 0xA089539C|I2C |SYSCON |0xF4800010||0x00980130| 0xA0895590|I2C |SYSCON |0xF4800010||0x00980130| 0xA08955A8|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955B4|I2C |WHBSYSCON|0xF4800020||0x00080000| 0xA08955BC|I2C |SYSCON |0xF4800010||0x008800A0| 0xA08955DC|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955E8|I2C |WHBSYSCON|0xF4800020||0x00000080| 0xA08955F0|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955FC|I2C |WHBSYSCON|0xF4800020||0x00000020| 0xA0895530|I2C |ICR |0xF48000FC||0x00004000| 0xA07EDF94|I2C |BUSCON |0xF4800014||0x00000000| 0xA07EDF9C|I2C |CLC |0xF4800000||0x00000001| 0xA07EE064|I2C |CLC |0xF4800000||0x00000100| 0xA07EE06C|I2C |BUSCON |0xF4800014||0xA0007E11| 0xA07EE070|I2C |SYSCON |0xF4800010||0x00880000| 0xA07EE07C|I2C |SYSCON |0xF4800010||0x00880000| 0xA089550C|I2C |ICR |0xF48000FC||0x00000000| 0xA0895514|I2C |ICR |0xF48000FC||0x00004000| 0xA0895518|I2C |ICR |0xF48000FC||0x00000000| 0xA0895520|I2C |ICR |0xF48000FC||0x00001000| 0xA0895868|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895878|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895888|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895938|I2C |RTB |0xF4800018||0x00001362| 0xA0895940|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895950|I2C |SYSCON |0xF4800010||0x04880000| 0xA0895964|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA0895970|I2C |WHBSYSCON|0xF4800020||0x00100000| 0xA0895540|I2C |ICR |0xF48000FC||0x00003000| 0xA0895548|I2C |ICR |0xF48000FC||0x00007000| 0xA0895374|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895388|I2C |SYSCON |0xF4800010||0x04980230| 0xA089539C|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895420|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895438|I2C |SYSCON |0xF4800010||0x00980230| 0xA0895444|I2C |RTB |0xF4800018||0x00000010| 0xA0895540|I2C |ICR |0xF48000FC||0x00003000| 0xA0895548|I2C |ICR |0xF48000FC||0x00007000| 0xA0895374|I2C |SYSCON |0xF4800010||0x00980130| 0xA0895388|I2C |SYSCON |0xF4800010||0x00980130| 0xA089539C|I2C |SYSCON |0xF4800010||0x00980130| 0xA0895590|I2C |SYSCON |0xF4800010||0x00980130| 0xA08955A8|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955B4|I2C |WHBSYSCON|0xF4800020||0x00080000| 0xA08955BC|I2C |SYSCON |0xF4800010||0x008800A0| 0xA08955DC|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955E8|I2C |WHBSYSCON|0xF4800020||0x00000080| 0xA08955F0|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955FC|I2C |WHBSYSCON|0xF4800020||0x00000020| 0xA0895530|I2C |ICR |0xF48000FC||0x00004000| 0xA07EDF94|I2C |BUSCON |0xF4800014||0x00000000| 0xA07EDF9C|I2C |CLC |0xF4800000||0x00000001| 0xA07EE064|I2C |CLC |0xF4800000||0x00000100| 0xA07EE06C|I2C |BUSCON |0xF4800014||0xA0007E11| 0xA07EE070|I2C |SYSCON |0xF4800010||0x00880000| 0xA07EE07C|I2C |SYSCON |0xF4800010||0x00880000| 0xA089550C|I2C |ICR |0xF48000FC||0x00000000| 0xA0895514|I2C |ICR |0xF48000FC||0x00004000| 0xA0895518|I2C |ICR |0xF48000FC||0x00000000| 0xA0895520|I2C |ICR |0xF48000FC||0x00001000| 0xA0895868|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895878|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895888|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895938|I2C |RTB |0xF4800018||0x00004462| 0xA0895940|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895950|I2C |SYSCON |0xF4800010||0x04880000| 0xA0895964|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA0895970|I2C |WHBSYSCON|0xF4800020||0x00100000| 0xA0895540|I2C |ICR |0xF48000FC||0x00003000| 0xA0895548|I2C |ICR |0xF48000FC||0x00007000| 0xA0895374|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895388|I2C |SYSCON |0xF4800010||0x04980230| 0xA089539C|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895420|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895438|I2C |SYSCON |0xF4800010||0x00980230| 0xA0895444|I2C |RTB |0xF4800018||0x00000062| 0xA0895540|I2C |ICR |0xF48000FC||0x00003000| 0xA0895548|I2C |ICR |0xF48000FC||0x00007000| 0xA0895374|I2C |SYSCON |0xF4800010||0x00980130| 0xA0895388|I2C |SYSCON |0xF4800010||0x00980130| 0xA089539C|I2C |SYSCON |0xF4800010||0x00980130| 0xA0895590|I2C |SYSCON |0xF4800010||0x00980130| 0xA08955A8|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955B4|I2C |WHBSYSCON|0xF4800020||0x00080000| 0xA08955BC|I2C |SYSCON |0xF4800010||0x008800A0| 0xA08955DC|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955E8|I2C |WHBSYSCON|0xF4800020||0x00000080| 0xA08955F0|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955FC|I2C |WHBSYSCON|0xF4800020||0x00000020| 0xA0895530|I2C |ICR |0xF48000FC||0x00004000| 0xA07EDF94|I2C |BUSCON |0xF4800014||0x00000000| 0xA07EDF9C|I2C |CLC |0xF4800000||0x00000001| 0xA07EE064|I2C |CLC |0xF4800000||0x00000100| 0xA07EE06C|I2C |BUSCON |0xF4800014||0xA0007E11| 0xA07EE070|I2C |SYSCON |0xF4800010||0x00880000| 0xA07EE07C|I2C |SYSCON |0xF4800010||0x00880000| 0xA089550C|I2C |ICR |0xF48000FC||0x00000000| 0xA0895514|I2C |ICR |0xF48000FC||0x00004000| 0xA0895518|I2C |ICR |0xF48000FC||0x00000000| 0xA0895520|I2C |ICR |0xF48000FC||0x00001000| 0xA0895868|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895878|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895888|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895938|I2C |RTB |0xF4800018||0x00004662| 0xA0895940|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895950|I2C |SYSCON |0xF4800010||0x04880000| 0xA0895964|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA0895970|I2C |WHBSYSCON|0xF4800020||0x00100000| 0xA0895540|I2C |ICR |0xF48000FC||0x00003000| 0xA0895548|I2C |ICR |0xF48000FC||0x00007000| 0xA0895374|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895388|I2C |SYSCON |0xF4800010||0x04980230| 0xA089539C|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895420|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895438|I2C |SYSCON |0xF4800010||0x00980230| 0xA0895444|I2C |RTB |0xF4800018||0x00000067| 0xA0895540|I2C |ICR |0xF48000FC||0x00003000| 0xA0895548|I2C |ICR |0xF48000FC||0x00007000| 0xA0895374|I2C |SYSCON |0xF4800010||0x00980130| 0xA0895388|I2C |SYSCON |0xF4800010||0x00980130| 0xA089539C|I2C |SYSCON |0xF4800010||0x00980130| 0xA0895590|I2C |SYSCON |0xF4800010||0x00980130| 0xA08955A8|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955B4|I2C |WHBSYSCON|0xF4800020||0x00080000| 0xA08955BC|I2C |SYSCON |0xF4800010||0x008800A0| 0xA08955DC|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955E8|I2C |WHBSYSCON|0xF4800020||0x00000080| 0xA08955F0|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955FC|I2C |WHBSYSCON|0xF4800020||0x00000020| 0xA0895530|I2C |ICR |0xF48000FC||0x00004000| 0xA07EDF94|I2C |BUSCON |0xF4800014||0x00000000| 0xA07EDF9C|I2C |CLC |0xF4800000||0x00000001| 0xA07EE064|I2C |CLC |0xF4800000||0x00000100| 0xA07EE06C|I2C |BUSCON |0xF4800014||0xA0007E11| 0xA07EE070|I2C |SYSCON |0xF4800010||0x00880000| 0xA07EE07C|I2C |SYSCON |0xF4800010||0x00880000| 0xA089550C|I2C |ICR |0xF48000FC||0x00000000| 0xA0895514|I2C |ICR |0xF48000FC||0x00004000| 0xA0895518|I2C |ICR |0xF48000FC||0x00000000| 0xA0895520|I2C |ICR |0xF48000FC||0x00001000| 0xA0895868|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895878|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895888|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895938|I2C |RTB |0xF4800018||0x00004262| 0xA0895940|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895950|I2C |SYSCON |0xF4800010||0x04880000| 0xA0895964|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA0895970|I2C |WHBSYSCON|0xF4800020||0x00100000| 0xA0895540|I2C |ICR |0xF48000FC||0x00003000| 0xA0895548|I2C |ICR |0xF48000FC||0x00007000| 0xA0895374|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895388|I2C |SYSCON |0xF4800010||0x04980230| 0xA089539C|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895420|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895438|I2C |SYSCON |0xF4800010||0x00980230| 0xA0895444|I2C |RTB |0xF4800018||0x00000008| 0xA0895540|I2C |ICR |0xF48000FC||0x00003000| 0xA0895548|I2C |ICR |0xF48000FC||0x00007000| 0xA0895374|I2C |SYSCON |0xF4800010||0x00980130| 0xA0895388|I2C |SYSCON |0xF4800010||0x00980130| 0xA089539C|I2C |SYSCON |0xF4800010||0x00980130| 0xA0895590|I2C |SYSCON |0xF4800010||0x00980130| 0xA08955A8|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955B4|I2C |WHBSYSCON|0xF4800020||0x00080000| 0xA08955BC|I2C |SYSCON |0xF4800010||0x008800A0| 0xA08955DC|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955E8|I2C |WHBSYSCON|0xF4800020||0x00000080| 0xA08955F0|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955FC|I2C |WHBSYSCON|0xF4800020||0x00000020| 0xA0895530|I2C |ICR |0xF48000FC||0x00004000| 0xA07EDF94|I2C |BUSCON |0xF4800014||0x00000000| 0xA07EDF9C|I2C |CLC |0xF4800000||0x00000001| 0xA07EE064|I2C |CLC |0xF4800000||0x00000100| 0xA07EE06C|I2C |BUSCON |0xF4800014||0xA0007E11| 0xA07EE070|I2C |SYSCON |0xF4800010||0x00880000| 0xA07EE07C|I2C |SYSCON |0xF4800010||0x00880000| 0xA089550C|I2C |ICR |0xF48000FC||0x00000000| 0xA0895514|I2C |ICR |0xF48000FC||0x00004000| 0xA0895518|I2C |ICR |0xF48000FC||0x00000000| 0xA0895520|I2C |ICR |0xF48000FC||0x00001000| 0xA0895868|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895878|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895888|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895938|I2C |RTB |0xF4800018||0x00004462| 0xA0895940|I2C |SYSCON |0xF4800010||0x00880000| 0xA0895950|I2C |SYSCON |0xF4800010||0x04880000| 0xA0895964|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA0895970|I2C |WHBSYSCON|0xF4800020||0x00100000| 0xA0895540|I2C |ICR |0xF48000FC||0x00003000| 0xA0895548|I2C |ICR |0xF48000FC||0x00007000| 0xA0895374|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895388|I2C |SYSCON |0xF4800010||0x04980230| 0xA089539C|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895420|I2C |SYSCON |0xF4800010||0x04980230| 0xA0895438|I2C |SYSCON |0xF4800010||0x00980230| 0xA0895444|I2C |RTB |0xF4800018||0x00000062| 0xA0895540|I2C |ICR |0xF48000FC||0x00003000| 0xA0895548|I2C |ICR |0xF48000FC||0x00007000| 0xA0895374|I2C |SYSCON |0xF4800010||0x00980130| 0xA0895388|I2C |SYSCON |0xF4800010||0x00980130| 0xA089539C|I2C |SYSCON |0xF4800010||0x00980130| 0xA0895590|I2C |SYSCON |0xF4800010||0x00980130| 0xA08955A8|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955B4|I2C |WHBSYSCON|0xF4800020||0x00080000| 0xA08955BC|I2C |SYSCON |0xF4800010||0x008800A0| 0xA08955DC|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955E8|I2C |WHBSYSCON|0xF4800020||0x00000080| 0xA08955F0|I2C |WHBSYSCON|0xF4800020||0x00000000| 0xA08955FC|I2C |WHBSYSCON|0xF4800020||0x00000020| 0xA0895530|I2C |ICR |0xF48000FC||0x00004000| 0xA07EDF94|I2C |BUSCON |0xF4800014||0x00000000| 0xA07EDF9C|I2C |CLC |0xF4800000||0x00000001|

そして、これは、シーメンスCF75電話(スニファーがあります)からの赤外線を介した8バイトのファイル(内容を推測)habr.txt

のシーメンスCX75への転送です。

データレジスタのみをキャッチします。

USART1:IRファイル転送habr.txt

0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF C0 FF 3F 01 10 ?.. 64 77 01 FF FF FF FF 01 00 00 06 7C C1 C1 dw.....| 0xA07F1BC0|USART1 |RXB |0xF1800024|| C1 FF FF FF FF FF FF FF FF FF FF C0 FE BF 01 40 ї.@ 90 81 09 10 64 77 01 01 00 00 B1 24 00 53 49 45 ђЃ..dw....±$.SIE 4D 45 4E 53 20 43 58 37 35 3E 35 C1 MENS CX75>5 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF C0 FF 3F 01 10 ?.. 64 77 01 FF FF FF FF 01 01 00 DE 65 C1 C1 dw....e 0xA07F1BC0|USART1 |RXB |0xF1800024|| C1 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF C0 FF 3F 01 10 ?.. 64 77 01 FF FF FF FF 01 02 00 B6 4F C1 C1 FF FF dw....¶O FF FF FF FF FF FF FF FF FF C0 FF 3F 01 10 64 77 ?..dw 01 FF FF FF FF 01 03 00 6E 56 C1 C1 FF FF FF FF ....nV FF FF FF FF FF FF FF C0 FF 3F 01 10 64 77 01 FF ?..dw. FF FF FF 01 04 00 66 1B C1 C1 FF FF FF FF FF FF ...f. FF FF FF FF FF C0 FF 3F 01 10 64 77 01 FF FF FF ?..dw. FF 01 05 00 BE 02 C1 C1 FF FF FF FF FF FF FF FF ...ѕ. FF FF FF C0 FF 3F 01 10 64 77 01 FF FF FF FF 01 ?..dw.. FF 00 B1 24 00 53 49 45 4D 45 4E 53 20 43 46 37 .±$.SIEMENS CF7 35 51 CD C1 C1 FF FF FF FF FF FF FF FF FF FF FF 5Q C0 FF 93 10 64 77 01 40 90 81 09 B4 01 01 3E 82 “.dw.@ђЃ.ґ..>‚ 01 07 83 01 0F 84 01 01 85 01 04 86 01 07 08 01 ..ѓ..„..…..†.... FF 25 82 C1 C1 %‚ 0xA07F1BC0|USART1 |RXB |0xF1800024|| C1 FF FF FF FF FF FF FF FF FF FF C0 B4 73 40 90 ґs@ђ 81 09 10 64 77 01 01 01 3E 82 01 07 83 01 0F 84 Ѓ..dw...>‚..ѓ..„ 01 01 85 01 04 86 01 07 08 01 FF 60 18 C1 ..…..†....`. 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 C1 C1 C1 C1 C1 C1 C1 C1 C1 C1 C1 C1 J C1 C1 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 11 41 ґ.A 53 C1 S 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 10 µ. 80 02 01 00 34 14 C1 C1 Ђ...4. 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 31 43 ґ1C 72 C1 r 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 30 82 ґ0‚ 00 81 00 8C 70 C1 .Ѓ.Њp 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 32 µ2 00 02 84 04 4F 42 45 58 13 49 72 44 41 3A 54 69 ..„.OBEX.IrDA:Ti 6E 79 54 50 3A 4C 73 61 70 53 65 6C 04 AF C1 C1 nyTP:LsapSel.Ї 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 31 µ1 9B 6B C1 C1 ›k 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 52 02 ґR. 00 84 00 00 01 00 02 01 00 00 00 04 8D AF C1 .„..........ЌЇ 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 54 µT 84 04 01 00 04 18 B5 C1 C1 „.....µ 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 71 47 ґqG 30 C1 0 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 51 µQ 9D 08 C1 C1 ќ. 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 74 84 ґt„ 04 81 00 04 41 A3 C1 .Ѓ..AЈ 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 71 µq 9F 29 C1 C1 џ) 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 71 47 ґqG 30 C1 0 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 71 µq 9F 29 C1 C1 џ) 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 71 47 ґqG 30 C1 0 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 71 µq 9F 29 C1 C1 C1 џ) 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 71 47 ґqG 30 C1 0 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 71 µq 9F 29 C1 C1 C1 C1 C1 C1 C1 C1 C1 C1 C1 C1 C1 C1 џ) C1 C1 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 71 47 ґqG 30 C1 0 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 71 µq 9F 29 C1 C1 C1 џ) 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 71 47 ґqG 30 C1 0 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 71 µq 9F 29 C1 C1 џ) 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 71 47 ґqG 30 C1 0 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 71 µq 9F 29 C1 C1 џ) 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 71 47 ґqG 30 C1 0 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 71 µq 9F 29 C1 C1 C1 C1 C1 C1 C1 C1 C1 C1 C1 C1 џ) 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 71 47 ґqG 30 C1 0 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 71 µq 9F 29 C1 C1 џ) 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 71 47 ґqG 30 C1 0 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 71 µq 9F 29 C1 C1 џ) 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 71 47 ґqG 30 C1 0 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 76 µv 04 04 00 80 00 07 10 00 02 0B 92 AC C1 C1 ...Ђ......'¬ 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 91 49 ґ'I D7 C1 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 71 µq 9F 29 C1 C1 џ) 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 96 04 ґ–. 04 01 A0 00 07 10 00 02 0B 6F 76 C1 .. ......ov 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 98 µ˜ 04 04 01 02 00 1D 01 00 15 00 68 00 61 00 62 00 ..........hab 72 00 2E 00 74 00 78 00 74 00 00 C3 00 00 00 08 r...txt..... 8C 02 C1 C1 Њ. 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 B1 4B ґ±K F6 C1 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 91 µ' 91 CE C1 C1 ' 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 B8 04 ґ. 04 01 90 00 03 99 A7 C1 ..ђ..§ 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 BA µє 04 04 01 02 00 0E 48 00 0B 48 41 42 52 48 41 42 ......H..HABRHAB 52 96 88 C1 C1 R–€ 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 D1 4D ґM 95 C1 • 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 B1 µ± 93 EF C1 C1 “ 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 D1 4D ґM 95 C1 • 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 B1 µ± 93 EF C1 C1 “ 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 D1 4D ґM 95 C1 • 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 B1 µ± 93 EF C1 C1 “ 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 D1 4D ґM 95 C1 • 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 B1 µ± 93 EF C1 C1 “ 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 D1 4D ґM 95 C1 • 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 B1 µ± 93 EF C1 C1 “ 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 D1 4D ґM 95 C1 • 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 B1 µ± 93 EF C1 C1 “ 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 D1 4D ґM 95 C1 • 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 B1 µ± 93 EF C1 C1 “ 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 DA 04 ґ. 04 01 90 00 03 A7 34 C1 ..ђ..§4 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 DC µ 04 04 01 82 00 06 49 00 03 DD A5 C1 C1 ...‚..I..Ґ 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 F1 4F ґO B4 C1 ґ 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 D1 µ 95 8C C1 C1 •Њ 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 FC 04 ґ. 04 01 A0 00 03 47 89 C1 .. ..G‰ 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 FE µ 04 04 01 81 00 03 A4 66 C1 C1 ...Ѓ..¤f 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 11 41 ґ.A 53 C1 S 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 F1 µ 97 AD C1 C1 — 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 1E 04 ґ.. 04 01 A0 00 03 64 9C C1 .. ..dњ 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 11 41 ґ.A 53 C1 S 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 11 41 ґ.A 53 C1 S 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 10 µ. 84 04 02 01 E0 8B C1 C1 „...‹ 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 31 43 ґ1C 72 C1 r 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 31 43 ґ1C 72 C1 r 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 12 µ. 80 02 02 01 5D 39 C1 C1 Ђ...]9 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 11 µ. 99 4A C1 C1 J 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 51 45 ґQE 11 C1 . 0xA0A3F3B0|USART1 |TXB |0xF1800020|| FF FF FF FF FF FF FF FF FF FF FF FF FF C0 B5 53 µS 8F 2B C1 C1 Џ+ 0xA07F1BC0|USART1 |RXB |0xF1800024|| FF FF FF FF FF FF FF FF FF FF FF FF C0 B4 73 40 ґs@ 90 81 09 10 64 77 01 3C 38 C1 ђЃ..dw.<8

I2Cに戻りましょう。データ転送のみが監視されるようにフィルターを設定します。

クリックすると、サービス音が鳴り、バックライト、音量、振動が変更され、何かが起こっていることがわかります。

ファイル

IOSniffer_CPPBuilder_XE5.rar

IOSniffer_IAR42.rar

IOSniffer_I2C.avi