Jon Casey、IBM半導体研究開発センター

先日、IBM半導体研究開発センターの従業員であるジョンケーシーが非常に興味深いインタビューを行いました。 その中で、ケーシーは、ムーアの法則の効果が鈍化し、新しい何かが必要であるため、IBMはCMOS技術とフォン・ノイマン・アーキテクチャの価値ある代替を探していると述べた。

ジョン・ケイシー自身は外部の人間ではなく、集積回路技術の分野で非常に高い資格を持っています。 ケーシーは、最新のプロジェクトの1つを含む、非常に興味深いプロジェクトに参加しました。ムーアの法則を超えたテクノロジーの可能性の研究です。 シンポジウムでジョン・ケイシーの基調講演になったのはこのトピックであり、カリフォルニア(米国)のSEMI国際半導体機器および材料協会の業界戦略に捧げられました。

プレゼンテーションの前に、著者はEE Timesにインタビューを行い、レポートの主要なポイントを提示しました。 ケーシーはバーニー・マイヤーソンの意見に対する支持を表明し、バーニー・マイヤーソンは最近EE Timesにインタビューを行った。 「現在、ムーアの法則の差し迫った死について多くの記事が書かれており、具体的な日付も言及されています。 そのようなシステムのデータ配列は単純に巨大であるため、情報中心と呼ぶことができる新しいタイプのアーキテクチャへの移行があるのはそのためです」とケイシーは言います。

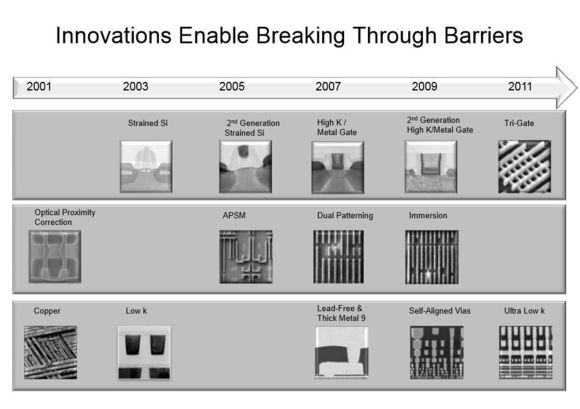

とりわけ、現在ではチップとデバイスの製造方法に変化があります。

確かに、 450 mmシリコンウェーハへの移行とハード紫外線リソグラフィー(EUV)は、ここで別の要因が経済的な実現可能性で重要な役割を果たすため、すぐには起こりません。 最初は、集積回路レベルでの体積またはいわゆる不均一小型化への移行が行われ、さらなる小型化による経済性と同様に、より高い性能が実現されます。

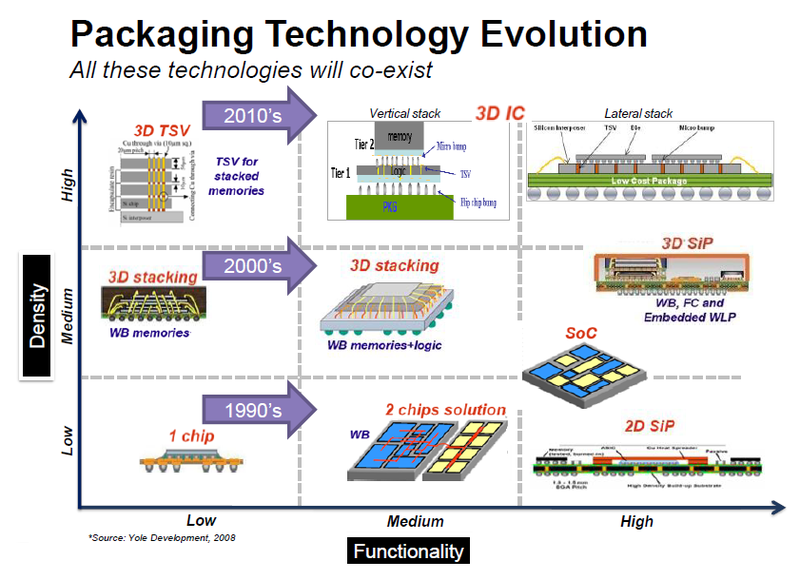

ジョン・ケイシーは、この場合の最良の解決策の1つは3D統合であり、非常に高い値の入出力速度を提供すると考えています。 したがって、Caseyによると、2つのアクティブチップの従来の3Dスタックを使用する価値があります。 このようなソリューションを導入する最初の利点は、密度が高いことです。 2番目の利点は、アクセス速度が向上し、I / O速度を最適化できることです。

これらのパラメータは、材料自体、レイアウト、および接続順序を改善することで改善できます(ジョイントの長さを短くするため)。 そして、3Dはこのための絶好の機会です。

別のオプションもあります-これは2.5D統合です。このオプションは現在、会社の専門家によって検討され、議論されています。 2.5D統合は、シリコン、有機化合物、またはガラスに基づいて実装できます。 そして現在、これらすべての機能は積極的にテストされており、重い負荷と大量のデータの下でテストされています。

2.5Dソリューションの利点は、この方法を使用すると、チップをさまざまな製造技術と組み合わせて、最終価格がそれほど高くない高性能のモジュールを取得できることです。 CMOSプロセッサクリスタルとシリコンインターポーザー上の基板に取り付けられた2つの130 nm SiGeトランジスタトランシーバーを備えた最初の45 nm シリコンオンインシュレータ制御チップで、3つのチップを組み合わせて使用することが述べられています。

その結果、チップ間のデータ転送速度が2 Tbit / sである生産的かつ機能的な混合信号トランシーバーが得られます。 これは非常に重要な成果であり、「ムーアの法則が減速する状況で速度を確保する方法」という質問への答えかもしれません。