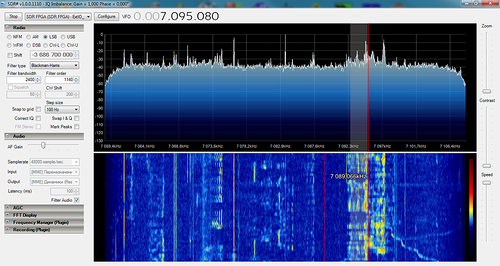

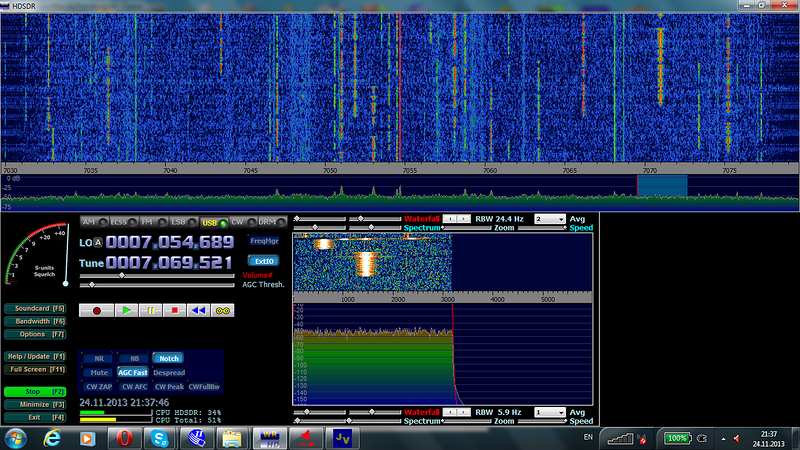

受信信号の例:

ここで SDRテクノロジーについて読むことができます 。 つまり、これは大量の情報処理をデジタル形式で行う無線信号受信技術です。 FPGAと高速ADCを使用することにより、下り周波数転送もデジタルで実行されるレシーバーを作成できます。 この方法は、DDC(デジタルダウンコンバージョン)と呼ばれます。詳細については、 こちらとこちら(より多くの理論)を参照してください 。 この手法を使用すると、アナログ部分がADCのみであるレシーバーを大幅に簡素化できます。

そして今、私の受信機についてより詳細に。

DE0-NanoデバッグボードにインストールされたアルテラFPGAに基づいています。 ただし、料金は比較的安価(学生は60ドル)ですが、配送料はかなり高くなります(50ドル)。 今では、FPGAに精通し始めている無線アマチュアの間でますます人気が高まっています。

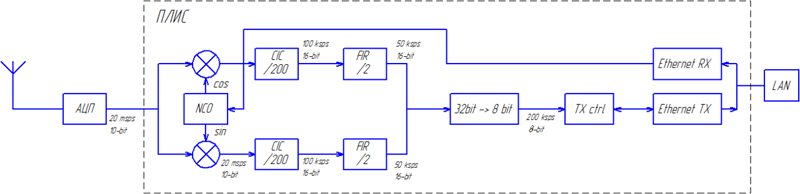

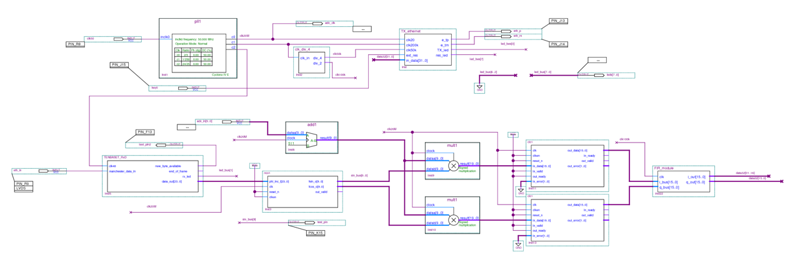

FPGAの主なタスクは、ADCからデジタル信号を「キャプチャ」し、それを低周波数領域に転送し、フィルタリングして、コンピューターに結果を送信することです。 私が実装した受信機のブロック図の形式は次のとおりです。

無線信号とデジタル情報が通過するコンポーネントを順番に検討します。

空中

ラジオのアマチュアには、「良いアンテナは最高のアンプです」という言葉があります。 実際、多くはアンテナに依存しています。 最も興味深い短波信号のほとんどは、単純なアンテナ(ワイヤなど)では受信できません。 街の外に特別な問題はありません-十分に長いワイヤは良いアンテナとして機能します(受信用)。 市では、特に大きな鉄筋コンクリートの家の中で、すべてが悪化しています。長いアンテナを伸ばすことはできず、不快なノイズがたくさんあります(家電製品は非常に高いノイズレベルを空中で発生させることがあります)。

無線信号を受信するには、アクティブフレームアンテナを使用します 。その設計については、 ここで説明します 。

私のアンテナは次のようになります。

実際、アンテナは大きな振動回路です(コンデンサはテーブル上の箱の中にあります)。 バルコニーに設置されており、非常によく機能します。 ループアンテナの主な利点は、共振現象の使用により、未使用の周波数でノイズを抑制できることですが、欠点があります-ある周波数範囲から別の周波数範囲に変更する場合、再構築する必要があります。

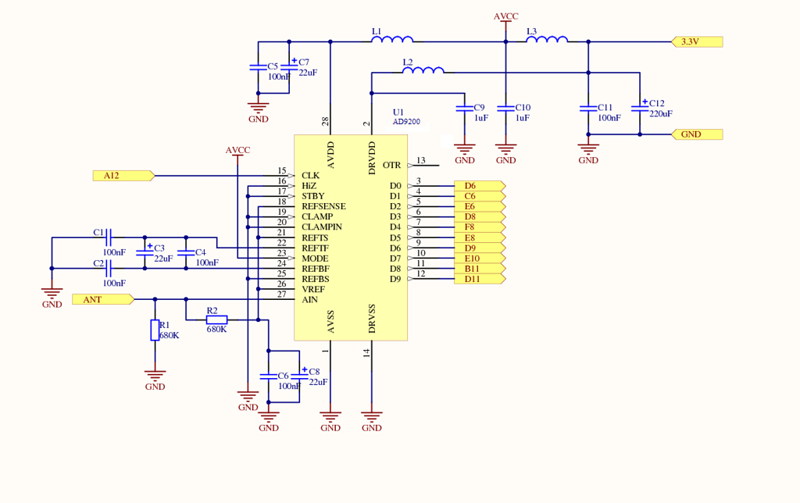

ADC

ADCの選択も簡単ではありません。 ADCは、ダイナミックレンジを拡大するために高いビット深度を備えている必要があり、DDCレシーバーの場合も高速である必要があります。 通常、16ビットの分解能と50 MSPSを超える速度のADCは、優れたDDC受信機にインストールされます。 ただし、このようなADCのコストは50ドル以上であり、実験デザインにもっとシンプルなものを入れたかったのです。

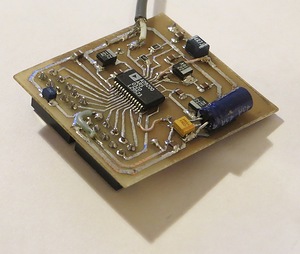

AD9200を選択しました。200ルーブルに相当する10ビット20 MSPS ADCです。 これらはDDCレシーバーの非常に平凡な特性ですが、実際に示されているように、ADCは信号の受信に非常に適しています。

ADCは別のボードにインストールされ、デバッグに挿入されます。

ボードの底部は金属化されており、金属層はADCグランドに接続されており、干渉からも保護しています。

ADCは正レベルの信号のみをデジタル化し、アンテナからの信号はバイポーラであるため、信号は基準電圧の半分だけシフトする必要があります(これには抵抗R1とR2が使用されます)。 次に、人為的に作成された定数成分がFPGAのデジタル信号から差し引かれます。

ADCがFPGAに送られた後のすべての信号処理。

ADCを使用したデータストリームは200 Mbps(10ビットx 20 MSPS)です。 そのようなストリームを直接コンピューターに転送することは非常に困難であり、処理することも非常に難しいため、信号周波数を特別に下げる必要があります。 より低い周波数に転送する場合、「ミラーチャネル」の現象が発生し、直交周波数変換が使用されます-信号は複雑な形式に変換されます(2つのI / Qチャネルに分割)。 低い周波数への転送は、元の信号にジェネレーターの信号を掛けることによって行われます。 使用するFPGAには十分なハードウェア乗算器があるため、これは問題ではありません。

Nco

入力信号を目的の周波数に転送するには、作成する必要があります。 このために、既製のQuartusコンポーネント-NCO(数値制御オシレーター)が使用されます。 ADCのクロック周波数(20 MHz)と同じクロック周波数がジェネレーターに適用され、周波数を決定する値がその制御入力に供給され、希望の周波数のデジタル正弦波信号が出力で生成され、20 MHzの周波数でサンプリングされます。 NCOは同時に余弦信号を生成できるため、直交信号を生成できます。

Cicフィルター

乗算器の出力からのジェネレーター信号とミキシングした後、信号は既に低い周波数に転送されていますが、高いサンプリング周波数(20 MSPS)のままです。 信号を間引く必要があります。つまり、サンプルの一部を破棄する必要があります。 このように不要なサンプルを破棄することは不可能です。これは出力信号の歪みにつながるためです。 したがって、信号は特別なフィルター(CICフィルター)を通過する必要があります。 この場合、レシーバーの出力で50 kHzの信号サンプリング周波数を取得したかったのです。 その結果、周波数を(20e6 / 50e3 = 400)回減らす必要があります。 間引きは2段階で行う必要があります-最初の200回、次に2回。

最初のステップはCICフィルターです。 5段フィルターを使用しました。

演算の結果、CICフィルターは信号帯域を下げることで出力信号のビット深度を増やします。 私の受信機では、人為的に16ビットに制限していました。

レシーバーには2つのチャンネルがあるため、2つのフィルターも必要です。

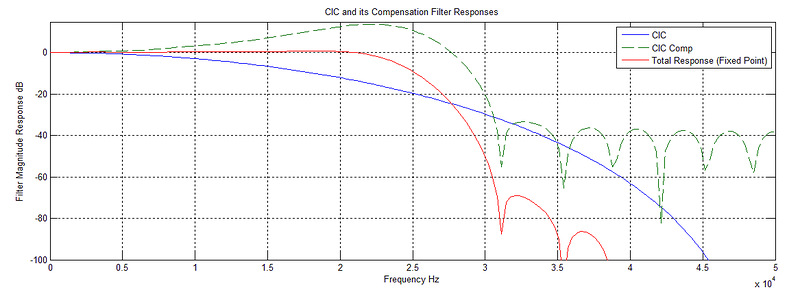

残念ながら、CICフィルターの周波数応答はかなり急峻で、出力サンプリング周波数(100 kHz)に近づくと0になります。 その曲率を補正するために、次のフィルターが使用されます。

補償FIRフィルター

このフィルターは、CICフィルターの周波数応答の低下を補償し、別のデシメーションステップ(2回)を実行するために必要です。 アルテラはすでにこのフィルタの計算方法を考慮しています。CICフィルタを作成すると、Matlabのプログラムが自動的に生成され、実行されて補正フィルタの係数を生成できます。

CIC、FIRおよび結果の周波数応答を表示します(Matlabの同じプログラムがグラフを作成します)。

25 kHzの周波数では、CICフィルターは信号を20 dB減衰させますが、FIRフィルターを使用した場合、減衰は10 dBのみであり、低い周波数では実際に減衰はありません。

FIRフィルターの出力では、デシメーションを考慮して、50 kHzの信号のサンプリング周波数があります。

信号をすぐに400回間引くことができなかったのはなぜですか? これは、FIRフィルターのカットオフ周波数がその出力の1/4でなければならないという事実によるものです。 この場合、入力と同様に、間引きなしのフィルター出力でのサンプリング周波数は100 kHzです。 この結果、上のグラフに見られるように、カットオフ周波数はわずか25 kHzになります。

両方のフィルターは、プレハブQuartusコンポーネントです。

データをコンピューターに転送する

受信したデータストリーム((16 + 16)ビットx 50 KSPS = 1.6 Mbit)をコンピューターに転送する必要があります。 イーサネット経由でデータを転送することにしました。 デバッグボードにはそのようなインターフェイスはありません。 PHYコントローラを備えた別のボードを作成し、Niosソフトプロセッサを起動し、それらを介してデータを転送するのが最も正しいでしょう。 ただし、これは設計を非常に複雑にします。 簡単な方法で行きました-イーサネットパケットはFPGA自体で形成できるため、10 Mbitの速度でデータを転送できます。 この場合、イーサネットケーブルは絶縁トランスを介してFPGA端子に接続されます。 この動作原理を備えたプロジェクトは、 こことここで見ることができます 。

基礎として、最初のプロジェクトを選択し、部分的に完成させました。 最初のプロジェクトでは、FPGAは指定されたIPおよびMACアドレスで特定のUDPパケットをコンピューターに送信します。 変更後、トランスミッタのイーサネットモジュールは1024バイトを送信し、RAMから読み取ります。 その結果、フィルター出力から取得された256ペアの16ビット信号値が1パケットでコンピューターに送信されます。 データはADCから継続的に受信され、バッチでコンピューターに送信する必要があるため、ダブルメモリバッファリングを実装する必要がありました-1つのRAMがいっぱいになると、別のRAMからのデータがイーサネット経由で送信されます。 最初のRAMがいっぱいになると、両方のRAMが「スワップ」します。かなり単純な制御モジュールがその役割を果たします。

フィルター出力のデータは、16ビット値のペアからのストリームで送信され、個々のバイトはイーサネット経由で送信されるため、ストリームを構造に変換するモジュールが導入され、32ビット50 KSPSストリームを8 200 KSPSビットに変換します。

判明したように、1.6 Mbitの速度でデータストリームを送信すると、レシーバーが接続されているデバイスはそれも検出しません(リンクなし)。 これは、データパケットが約5 msの周期で送信されるという事実によるものであり、他のネットワークデバイスに接続速度(10 Mbit)を伝えるために、8-24 msごとに特別な短パルス(NLP)を送信する必要があります。 パケット送信の頻度が高いため、イーサネットモジュールにはこれらのパルスを送信する時間がなく、自動ネゴシエーションは発生しません。

したがって、反対側のデバイスがまだ接続速度を決定できるようにするには、レシーバーの電源を入れたときにパケット送信頻度を一時的に(4倍)減らすだけで十分です。これにより、イーサネットモジュールはNLPパルスを送信することになります。

コンピューターからデータを受信する

(チューニング周波数を設定するために)受信機を制御するには、特定の値を送信する必要があります。これは、NCO周波数の設定に使用されます。

この値を受信するために、上記のサイトからのコンポーネントも使用され、データを受信するように変更され、24ビット数の形式で出力されます。 レシーバーとトランスミッターのモジュールは互いに接続されていないため、ARPを実装することはできません。実際、これはレシーバーにIPアドレスとMACアドレスがないことを意味します。 ネットワークにブロードキャストパケットを送信すると、情報を転送できます。

物理的には、トランスミッタの場合のように、ネットワークワイヤはトランスを介してデバッグボードに接続されます。 ただし、ここでは信号が非常に小さいため、任意のFPGA出力に接続することはできません。 LVDSインターフェイスをサポートするピンを使用する必要があります-これは差動です。

FPGAプログラムで使用されるリソース:

-5006 LE

-68個の9ビット乗算器(そのうち64個はFIRフィルターで使用されます)。

-16.826ビットメモリ(8 M9Kブロック)。

Quartusプロジェクトのプロジェクトビュー:

コンピューターでデータを処理する

コンピュータがデータを受信したら、処理する必要があります。 既製のプログラムを取ることをお勧めします。 通常、SDRプログラムでは、必要なデジタルフィルター、サウンドを形成してフィルター処理するように設計されたアルゴリズム、受信信号のFFT、スペクトルの構成、および「ウォーターフォール」を実装します。

私はHDSDRおよびSDRSharpプログラムを使用しますが、どちらも同じExtIOライブラリ(Winradプログラム形式)を使用したデータ入力をサポートしています。 ライブラリのソフトウェア要件は十分に文書化されています 。

このようなライブラリを作成する例を次に示します。 この例を再編集し、ネットワークからのデータの受信に追加して、2つのパケットを接着し(プログラムは少なくとも512組のI / Qサンプルを一度に粉砕します)、プログラムに送信し、プログラムの周波数を変更するときにNCOの計算値でブロードキャストパケットを送信します。 それ以前は、ライブラリを作成する必要がなかったので、C ++では強くありませんので、ライブラリにまったく最適に記述できません。

受信機フィルターの出力でのI / Q信号のサンプリング周波数は50 kHzであるため、50 kHzの帯域は受信プログラムで確認できます。 (NCOによって生成される周波数の±25 kHz)。

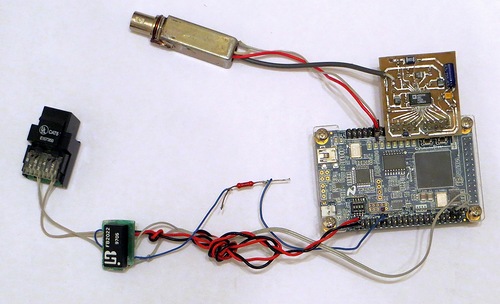

組み立てられた受信機は次のようになります。

抵抗器は、トランスの中点を3.3 V回路基板に接続します。これにより、ネットワークを介したデータの受信と送信が改善されます。

受信機が完全に組み立てられ、すべてのプログラムが作成された後、感度が十分でないことが判明しました。 アクティブなアンテナでさえ、放送ラジオ局と、高出力で動作するアマチュア無線ファンからの信号のみを受信しました。

私の知る限り、これはADCの容量が小さいためです。 感度を上げるには、BF988トランジスタ(小さな金属製の箱の中にある)に追加のアンプを作成する必要がありました。 増幅器は、受信機の感度を大幅に向上させることができました。

構造全体の外観:

電源ユニットは、アンテナアンプに電力を供給するために12 Vの電圧を提供します。金属製の丸い箱には、帯域外信号を低減するいくつかのバンドパスフィルターがあり、信号のプライムを改善します。 多くの場合、DFTなしで受信が可能です。

HFで何ができるかについて。 かなり高いノイズレベルにもかかわらず、非常に多くの信号を受信することが可能であり、放送ラジオ局はよく受信され、アマチュア無線受信機は悪くありません。

HDSDRプログラムで信号を受信する例(受信はCQ WW DXコンテスト中に実行されました):

レセプションビデオ:

WSPRnet信号を受信できる。 WSPRnetは、短いメッセージを自動的に相互に交換するアマチュアビーコンのネットワークです。 灯台からのデータはインターネット上で自動的に公開されます。 この場合、特別なプログラムをインストールすることにより、受信した信号をデコードしてネットワークに送信できます。 サイトには、特定の時間間隔のビーコン間のリンクが表示されているマップを表示する機会があります。

私が半日の入場で得たものは次のとおりです。

WSPRの重要な機能は、非常に小さい送信機電力(5 W未満)、送信信号の狭帯域、および1つのメッセージの長い送信期間(2分)です。 デコーダープログラムのデジタル処理のおかげで、非常に弱い信号を受信できます。 〜2000 kmの距離にある100 mWの灯台の信号を受信できました。

JT65アマチュア無線愛好家。 JT65は、ハム間のデジタル通信プロトコルの1つです。 WSPRと同様に、低電力で長時間の送信(1分)を使用します。 メッセージは自動的に受信されるため、受信者を長時間放置してから、受信者を確認できます。

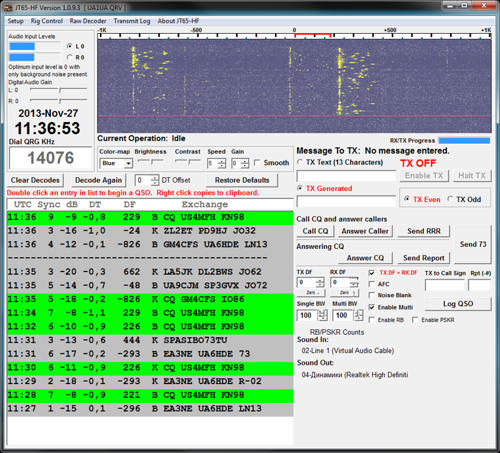

受付例:

デジタル放送(DRM)。 一部の放送ラジオ局は、音声をデジタルで送信します。 都市でそのような信号を受信することは容易ではありません-十分な信号レベルがありません。 1つのステーションを受け入れることに成功しました。

受信するのが興味深い他の多くの無線信号があります。 また、天気ファックス、RBUの正確なタイムステーション(66.6 kHzのすばらしい周波数)などがあります。

Quartus +ソースコードとExtIO dll自体のプロジェクト