故障のリスクについて最も単純なスキームを分析するために、それらは通常、すでに標準となっているタイムチャート法を使用します。 各ノードの信号は、厳密に互いの下に描かれています。 必要に応じて、ある状態から別の状態への遷移で人為的な遅延が発生し、出力信号はブール表現に従って構築されます。 この方法は、受信した信号にエラーを導入する可能性があるグラフで作業する必要があるため、良くありません。 そして、障害が発生するかどうか、そしてそれがどのように見えるかを知る必要があります。

2005年、私はこのトピックに触れ、 この記事で自分の考えを英語で表現しました。 しかし、私の良き友人は、ユーザーとの議論のためにHabrahabrで書くことを勧めました。

このトピックでは、回路を分析する手順をグラフィカルな表現から数学的な表現に移します。 この場合、論理演算を算術演算に置き換えることにより、パラメータ「時間」がブール代数に導入されます。 分析を簡単にするために、非同期のもの、つまり 外部(同期またはタイミング)信号、デジタル回路によって制御されない。

始めましょう...

1.ブール関数の論理表現から算術表現への移行

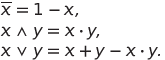

数値セットを考えます

。 否定、結合、選言の操作を定義し、それらから生成されます(たとえば、含意、代替選言など)。 これらの論理演算を集合Mの算術の観点から表現します。

。 否定、結合、選言の操作を定義し、それらから生成されます(たとえば、含意、代替選言など)。 これらの論理演算を集合Mの算術の観点から表現します。

(1)

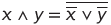

ド・モーガン法の正義を示しましょう

:

:

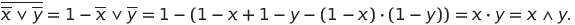

式にルールを追加する(1)

(2)

すべての正の整数mに対して、その有効性は明らかです。

回路の入力信号の関数であるブール関数の式は、算術演算と規則(2)の法則に従って簡略化できるようになりました。 単純化した後、ブール表現に戻ります。 同時に、シンボリック計算に進むことで、最小化プロセス自体を自動化できます。

2.パラメータ「時間」をブール代数に入力する

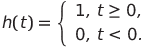

ご存じのとおり、単位ステップ関数またはヘビサイド関数は実数のセットで定義され、セットMに属する数を返します。

tが現在の時刻を示すものとします。 関数hは切り替え関数とも呼ばれることに注意してください。 次のステートメントは明らかです。 ある論理状態から別の論理状態への遷移を含む論理回路内の信号は、対応する引数で取得したヘビサイド関数の和差として表すことができます。

関数hには明らかな規則が成り立ちます

(3)

どこで

-信号が変化する時点。 ルール(3)を(1)および(2)に追加します。

-信号が変化する時点。 ルール(3)を(1)および(2)に追加します。

これで、論理回路の入力信号の解析式がわかれば、出力信号の関数の形を見つけることができます。

3.回路の論理要素の遅延

ヘビサイド関数の引数と遅延時間の差(既存の論理要素の場合、エッジの遅延(0から1への遷移)と立ち下がり(1から0への遷移)はほとんど同じであるため)論理要素の信号遅延をモデル化すると便利です。 したがって、回路の実際の論理要素は、各入力の「純粋な」遅延のリンクと理想的な論理要素の直列接続としてモデル化できます(ここで、遅延は遅延の持続時間に等しい)。 たとえば、遅延のある接続子の出力信号の方程式

入り口には形があります

入り口には形があります

どこで

そして

そして  -対応する入力信号を記述する関数。

-対応する入力信号を記述する関数。

4.失敗した状態を見つけるためのアルゴリズム

失敗した状態を見つけるために提案されたアルゴリズムは、時間図の方法に似ています。 この方法の利点は、信号のグラフィックイメージではなく、その分析式で作業することです(この場合、故障の時間特性を分析的に評価することが可能になります)。

1. DNFで指定された論理式に従って、調査対象の回路を機能させます。

2.入力信号の関数を定義します。これは、ヘビサイド関数で表される真理値表の遷移です。

3.規則(1)および(3)を適用して、回路の出力信号の式を検索するために、論理回路内の信号の経路をたどります。

4.結果の式にヘビサイド関数の差が含まれる場合、静的エラーが発生します。 遅延引数を持つヘビサイド関数が存在する場合、失敗は動的です。

5.論理回路解析の例。

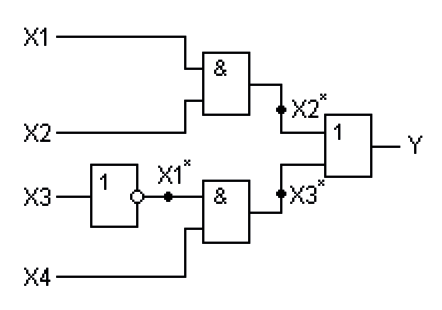

図11に示す回路の真理値表のセット1111からセット1001への遷移を調べます。 1。

図 1.ブール関数を実装する回路

。

。

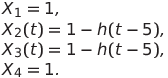

入力信号を次のように表します(簡単にするために、5時間単位に等しい時点での状態の変化を考慮します)。

すべての要素の遅延が同じであるとします

。 それから

。 それから

そのため、静的なエラーが発生しました-ヘビサイド関数の違いが結果の式に含まれています(図2)。

図 2.信号Y ( t )のグラフ。

おわりに

このトピックでは、デジタル回路の故障リスクを分析する方法を、回路内の信号の分析表現を使用して検討しました。 この場合、論理演算を算術演算に置き換える必要がありました。 ある信号状態から別の信号状態への遷移は、ヘビサイド関数によって記述されました。 タイムダイアグラムの方法について説明した変更の利点は、障害の特性を分析的に分析できることです。