2つの1.3 GHz ARMv7コア

RAM-1 GB。

150 nmの設計基準を持つ技術プロセス。

1つの200 MHz PowerPCコア。

RAM-256 MB。

上はiPhone5中央処理装置のパラメーター、下はCuriosityローバーです。 火星探査機のオンボードコンピューターは、新しいiPhoneの約200倍の費用がかかります。 なぜそう 宇宙船の中央処理装置は放射線にさらされています。 Habréには宇宙用電子機器に関する優れたレビュー記事がすでにありました。宇宙での失敗と失敗の背後にある物理的原理と効果について、さらに詳しく説明しようと思います。

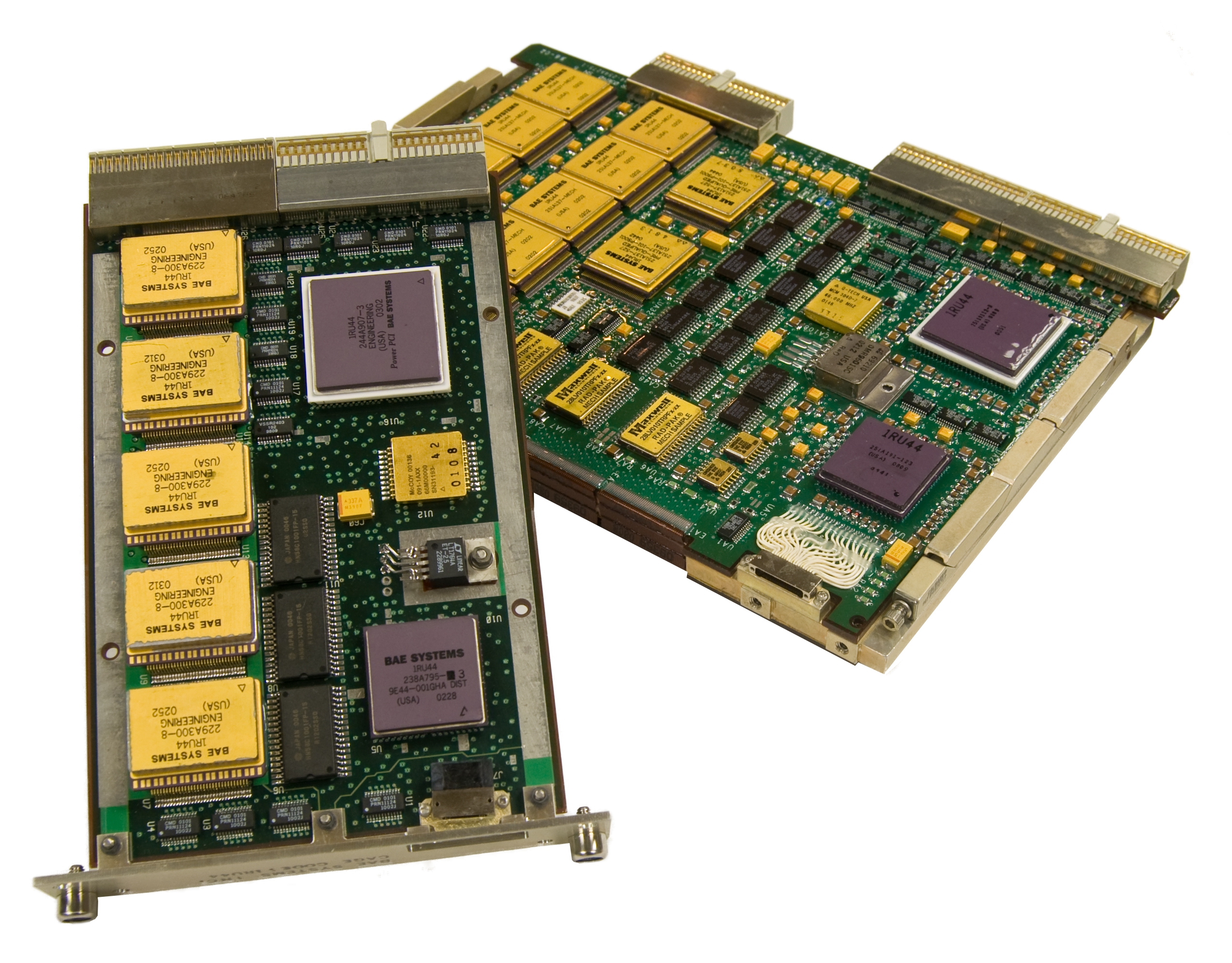

図1. BAE Systems RADシングルボードコンピューターのコストは数十万ドルで測定されます。

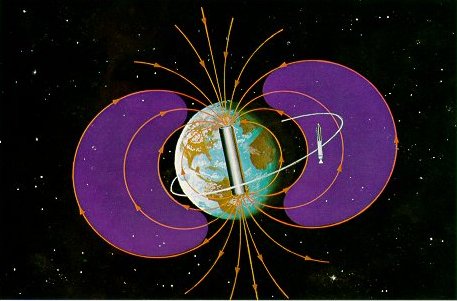

放射線の主な源は太陽と星です。 独自の発光体は、プロトンと電子を供給します。 他のすべては、たとえば重元素の核など、他の星から飛びます。 地球の放射線からの住民は、地球の放射線帯(ファンアレンベルトとも呼ばれます)に飛ぶ粒子を集める磁場によって保護されています。 これらは宇宙船にとって深刻な問題であるため、放射線帯で過ごす時間を最小限に抑えようとします。

図2.地球の放射線帯。

チップが宇宙に入るとどうなりますか? 主な影響は2つあります-総吸収線量の蓄積(総イオン化線量、TID)と、単一のイオン化粒子への曝露に関連する影響(シングルイベント効果、SEE)です。

放射線の総吸収線量は、マイクロ回路のいくつかの特性のドリフトを引き起こし、故障を引き起こします。 最も重要なメカニズムは、テクノロジーごとに異なります。 最近の超小型回路では、放射線による漏れ電流が関係しており、古い技術ではトランジスタのしきい値電圧のシフトが重要な役割を果たしていました。

マイクロ回路内の電離放射線の影響下で、 電子と正孔のペアが形成されます。 通常の条件下では、これらのペアは非常に迅速に再結合します(つまり、切り離された電子は原子によって捕獲されます)が、正孔と電子は電界で分離することがあります(反対符号の電荷が電界内で異なる方向に移動するため)。 シリコンのマイクロ回路で使用される主な絶縁体は、二酸化ケイ素(SiO 2 )です。 SiO 2内の電子と正孔の移動度は数桁異なります。したがって、シリコンによって電子がすばやく放出され、酸化物、特に酸化物とシリコンの界面に正孔が蓄積する可能性があります。

MOSトランジスタのゲート誘電体に電荷が蓄積されている場合、追加の正電圧として(またはしきい値電圧のシフトとして)動作に影響します。 その結果、nチャネルトランジスタは常に半開きになります。 厚いゲートゲート誘電体を使用する古い技術では、nチャネルトランジスタのしきい値電圧のシフトは、トランジスタが完全に閉じるのを停止するのに十分な大きさであり、当然のことながら回路動作の損失につながりました。 しかし、しきい値電圧の低下がさらに早くなると、リークのために超小型回路の総消費電流が許容レベルを超えたという事実に至りました。

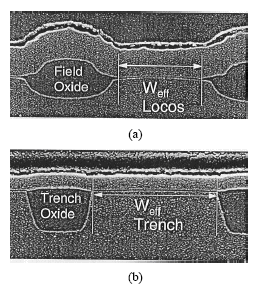

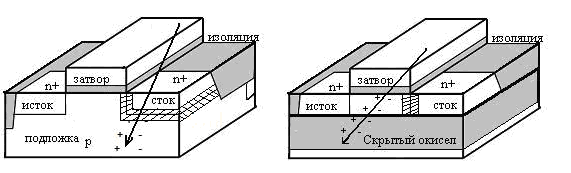

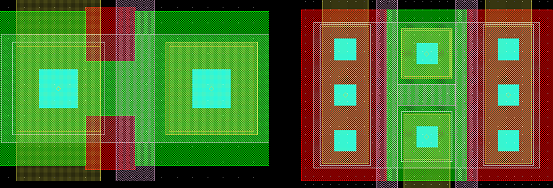

現代の技術では、ゲート誘電体の厚さは数ナノメートルであり、それらに十分な正孔を蓄積することができないため、トランジスタのしきい値電圧が大きく変化します。 したがって、決定的な役割は、マイクロ回路に存在する他の酸化物、つまり、隣接するトランジスタを分離する側面絶縁部、およびゲート誘電体の境界に電荷を蓄積することです。 図は、ゲートに沿ったMOSトランジスタの断面を示しています。 明るい層はシリコン、暗い層はSiO 2です。 横方向の絶縁がゲート絶縁体よりもはるかに厚いことがはっきりとわかります。 写真(a)と(b)の違いは、絶縁体の製造方法の違いに関連しており、トランジスタの耐放射線性に重要な役割を果たしています。

図3. LOCOSおよびSTIタイプの横方向絶縁を持つMOS構造のセクション。

厚い絶縁誘電体では、電界は非常に小さく、電子と正孔のペアの分離は不十分です。 ゲート誘電体では、電界は大きいが、酸化物自体は薄い。 しかし、遷移領域では、すべてが良好です(つまり、すべてが悪い)-酸化物はその中を充電するのに十分な厚さであり、電界は正孔と電子が効果的に分離されるように十分に大きいです。

マイクロ回路内のトランジスタは、トランジスタ自体と、サイドにある2つの寄生トランジスタの重ね合わせとして表すことができます。メイントランジスタのゲート誘電体とサイド絶縁体の間の遷移層は、ゲート誘電体の役割を果たします。 メイントランジスタのしきい値電圧は、放射線量にさらされてもほとんど変化しませんが、スプリアス構造のしきい値はゼロまで低下し、ゲートによって制御されない電流フローチャネルを作成します。 これらのチャネルを介して、電流はドレインからソースに自由に流れます-これはリーク電流と呼ばれます。

リークは、前述したように、回路の消費電流の増加(利用可能な電力が非常に控えめな宇宙船では許容できない場合があります)につながり、機能障害にさえつながります。 たとえば、最も一般的なフラッシュの問題は、ストレージ要素ではなく、上書きに使用される高電圧発生器にあります。 このジェネレーターにはキーがあり、リークのために完全に閉じるのを止めます。これがないと、メモリーを上書きするのに十分な電圧を生成できません。

単一の効果は、単一のイオン化粒子(陽子、中性子、またはより重い元素の核)がトランジスタに入り、「ソフト」(故障)と「ハード」(故障)に分けられた場合に発生します。後者は強力な回路の特徴であり、あまり理解されていない現象です。 故障オプションには、ゲート絶縁体の破壊と、ドレインとソース間の伝導チャネルの発生によるトランジスタのバーンアウト、およびサイリスタ効果が含まれます。これについては後で詳しく説明します。

「ソフト」障害には、2つの主なメカニズムがあります-一次および二次イオン化。 1つ目は重荷電粒子の特徴であり(TZZ。この文脈では、すべての原子核は陽子よりも重いと呼ばれます)、2つ目は陽子と中性子です。 微細回路を通過する際、粒子は結晶格子との相互作用により減速し、そのエネルギーの一部を与えます(このプロセスは摩擦中の加熱と比較できます)。

粒子の通過中に放出されるエネルギーは、シリコン原子をイオン化します。 通常の状態では、原子から引き離された電子の大部分が戻りますが、強い電界の近くでイオン化が発生すると、電子と正孔を分離できます。 このメカニズムは、線量が蓄積されたときに起こる現象と似ていますが、電荷キャリアはシリコンに蓄積できず、単一効果の持続時間は月単位ではなくピコ秒単位で測定されます。

シリコン内の強い電界は、閉じたトランジスタのソースpn接合であり、近くで電荷が分離すると、1つの符号の電荷キャリアが接地/電力線に落ち、2つ目がトランジスタのドレインに落ちます。 外部観測者の観点からは、プロセスの結果は、数十ピコ秒のリーディングエッジと数百のトレーリングエッジを持つ電流パルスのように見えます。 正確なパルスパラメーターは、マイクロ回路の製造技術、粒子の入射角などを含む多くの要因に依存します。

結果の電流パルスを経時的に積分すると、TZZヒットの結果として完全な電荷が放出されます。 障害を引き起こす最小の充電は、クリティカル充電と呼ばれます。 臨界電荷は、影響を受ける回路と入射粒子の両方のパラメーターに依存します。 さらに、実験的に測定することは非常に難しいため、通常は回路と粒子の相互作用をシミュレートし、さまざまな回路の故障抵抗を比較的シミュレートするために使用されます。

エネルギー放出は通常、線形エネルギー移動(LET;英語の用語は線形エネルギー移動、LET)を使用して表され、MeV×cm 2 / mgまたはより正確には(MeV /(mg / cm 3 ))/ cmで測定されます。 LETの1単位は、粒子が飛ぶ物質の単位密度あたりの移動距離のセンチメートルあたりの通過粒子によって放出されるエネルギーの量です。 一見したところ定義は非常にわかりにくいですが、この方法で選択されたユニットにはいくつかの重要な利点があります。まず、数値は実験的に測定するのが比較的簡単です。 第二に、第三に、実際に使用される値は通常1から数百の範囲です。

LETは一定値ではありません。つまり、マイクロサーキットハウジングカバー、結晶境界、および多数の層の下のトランジスタでの通過粒子のパラメータは異なります。 ただし、これより厚いケースが役立つことはありません。シリコンで移動した距離に対するLETの依存性は、通常、ある深さで最大になります(いわゆるブラッグピーク)。 同様の効果は、放射線療法や超小型回路製造の一部の操作で使用されます。注入イオンのパラメータは、特定の深さで停止し、深さで高レベルのドーピング層を作成するように選択されます。

陽子と中性子は非常に小さいLET(約0.01 MeV×cm 2 / mg)を持ちますが、高エネルギーの陽子/中性子がシリコンを通過すると、核反応の可能性があり、その生成物は短距離のイオンですが、大きなLET(最大15 MeV× cm 2 / mg)。 さらに、アルミニウムではなく銅のメタライゼーション(180 nm以下)を使用した技術プロセスでは、プロトンと第1レベルの接点に使用されるタングステンとの相互作用のメカニズムが説明されています(したがって、高感度pn接合の真上に位置しています)。 そのような反応の生成物のLETは30 MeV×cm 2 / mgに達することがあります。

故障に至る入射粒子の特徴的な最小LETは、設計基準が500-250 nmの技術では数十以内であり、陽子や中性子による一次イオン化でさえも臨界電荷が非常に小さいサブ100 nm技術では1オーダーです。誤動作を引き起こす可能性があります。 さらに、小さな臨界故障電荷は、粒子が逆バイアスされたストックpn接合だけでなく、バイアスのないソースを通過するときに十分な電荷を分離できるという事実につながります。

短い電流パルスは、マイクロ回路によってパルスノイズとして認識され、その振幅が十分に大きい場合、影響を受けるトランジスタの背後にある要素のスイッチングにつながる可能性があります。これは、放射線による障害です。 電流パルスの通過時の組み合わせ回路とアナログ回路は誤った結果を与え、記憶素子は完全に切り替えられます。 したがって、マイクロプロセッサの最も脆弱な部分はキャッシュメモリです。チップには多くのメモリがあり、故障は自然に消えることはありません。

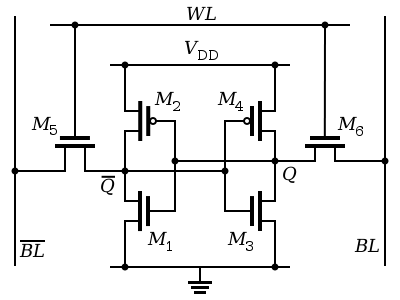

図4. 6トランジスタ記憶素子の図。

たとえば、静的メモリの6トランジスタセル(最も単純な使用されるストレージエレメント)で障害メカニズムを記述するのが最も便利です。 メモリ要素は、正のフィードバックと2つのキー(M5-M6)で接続された2つのインバーター(M1-M2およびM3-M4)で構成されています。 ストレージモードでは、2つのトランジスタが閉じられ、2つが開かれ、インバーター出力で反対の値になります。 トランジスタM1とM4を明確にするために開いてみましょう。 SLCが閉じたトランジスタ(M2またはM3)のドレインに入ると、イオン化電流パルスが発生し、セルで2つのプロセスが開始されます:正帰還トリガーと誘導電荷散逸。 これらのプロセスは独立しており(時定数は異なるトランジスタによって決定されます)、競合します(プロセスの効果は反対です)。

トランジスタM2をトランジスタとすると、電流パルスがトランジスタのドレインに現れます。 この瞬間のトランジスタM1は完全に開いており、小さな抵抗を持っています。つまり、誘導電流トランス電流がトランジスタM1を通過してグランドに流れます。 ただし、ノードnQの容量は、このノードの潜在能力がかなりの時間にわたって増大するように十分に大きくすることができます。 ノードnQの電位の増加は、第2のインバータ(M3〜M4)のスイッチングをもたらす。 この場合、第2のインバータの出力電圧は、トランジスタM1の抵抗が増加するように変化し、トランジスタM2が開く。 このプロセスが電荷吸収のプロセスよりも時間がかかる場合、ストレージエレメントが切り替わり、間違った値が書き込まれます。これは、放射線による障害(シングルイベントアップセット、SEU)です。

組み合わせロジックの障害は、ストレージエレメントの障害よりも少し簡単になります。フィードバックはなく、影響を受けるノードの可能性の増加は、次の段階に直接送信されます。 電圧振幅が十分に大きい場合、次のカスケードが切り替わります-そして、移行プロセス(単一イベントの過渡現象、ロシアの専門用語では「針」)がスキームに従って広がります。 組み合わせ論理の障害は、回路が障害にどのように応答するかに影響する追加の影響に関連付けられています。 一方では、論理マスキング効果があります:入力状態のすべての変更が回路の出力に影響するわけではありません(たとえば、2INE要素の入力の1つを切り替えても、2番目の入力に論理ゼロがある場合は出力に影響しません)。 一方、影響を受ける回路の出力に複数の要素がロードされている場合、障害は各要素の入力に行きます(クロックツリーの最初の部分で障害を想像してください)。 最後に、一時的なマスキング:組み合わせ回路の出力には、特定の間隔で値を記憶するトリガーがあります。 低周波数で動作する場合、トリガー全体が何も記憶しない時間にパルス全体が落ちる確率は非常に大きくなりますが、周波数が高くなると、パルスの持続時間(数百ピコ秒からナノ秒)はクロック信号の周期に匹敵し、大きなクロックの場合組み合わせロジックの重大な誤動作の強度は、メモリ要素の誤動作の強度よりもさらに高くなる可能性があります(ところで、組み合わせ回路の出力のトリガーも誤動作する可能性があります)。

TZChトラックの有効直径は1ミクロンのオーダーであり、最新のテクノロジーのロジックエレメントのサイズよりも大幅に大きくなっています。 したがって、キャッシュセルなどのいくつかの要素は、同じパーティクルで取得できます。 65 nmテクノロジーでは、「数個」が10になり、エラー訂正コードの適用に大きな困難が生じ、チップ要素のトポロジーを大幅に変更する必要が生じます。

TZChがトランジスタに入ると、単一の障害が発生するだけでなく、サイリスタ効果(専門用語では「ラッチ」またはラッチアップ)による条件付きのハード障害も発生する可能性があります。 この図は、ボリュームCMOSテクノロジーで作られたインバーターの断面を示し、超小型回路の層で形成されたスプリアス要素を示しています。

図5.サイリスタ効果に関係する寄生構造を示したCMOSインバーターの断面図。

2つのバイポーラトランジスタが、サイリスタとして知られるpnpn構造(ソース-ポケット-基板-ソース)を形成していることがわかります。 サイリスタのCVCは図に示されており、非線形性を持っているという特徴があります。つまり、構造上で特定の直接バイアスに達すると、抵抗が急激に低下し、それに応じて電流が増加します。

図6.サイリスタの電圧アンペア特性。

SLCがヒットすると、誘導電流パルスにより、バイポーラトランジスタが開き、寄生サイリスタ構造が低抵抗状態になる可能性があります。 その結果、グランドと電源の間に短絡が形成され、影響を受ける要素の操作性が失われ、消費電流が急激に増加し、影響を受ける要素の「焼損」と機能障害が発生します。 サイリスタ効果は、影響を受けるチップの電力をリセットすることで停止できるため、条件付きでハードに分類されます。 ただし、この方法は非常に不便であり、多数の障害があるため適用できません。 サイリスタ効果は、特に何らかの理由で特別に設計されたものの代わりに市販のチップを使用する場合、宇宙用の電子機器の開発者の主な頭痛の種の1つです。

サイリスタ効果に対処するには? トランジスタをより遠くに広げることができ、したがってトランジスタQ2のベース長を長くすることができますが、このオプションは水晶のパッキング密度の減少のために望ましくありません。 基板とポケットのドーピングレベルを上げると、電荷キャリアの移動度が低下しますが、これによりメイントランジスタの速度も低下します。

最も便利なオプションは、浮遊トランジスタの基本抵抗(RsおよびRw)を最小化することです。 , pn- , . .

– ( « » guard rings). (, -, - , - ). ( ), , .

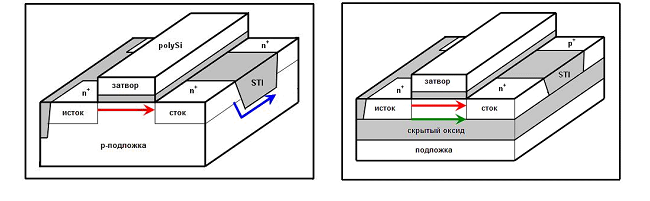

– , « » (, - Silicon on Insulator SOI). (, SOS), , , SiO 2 . , , SiO 2 ( buried oxide), – , , , . -, , NUM. pn-, - .

7. -, . .

, - « », . ( ), , .

, , , – . , , .

8. .

: , , , – ( ). , , , – , , . – . , , , . , . , , , – pn-, , . pn-. - , ( ). , , – , , .

? , , . – , ( full depleted SOI), . : .

9. . n-, – p-.

, – , – (, ). , , , . , – , , .

, , , , . , ( ).