電子製品を作成する最終段階は大量生産であり、最終的にデバイスの品質を決定するのはこれです。 組立ラインで障害が発生した場合、ユーザーは新しい電子機器の理想的なソフトウェアおよびハードウェアプラットフォームを評価できないため、機能制御とアセンブリテストは大量生産の必須段階です。

この記事の読者は、電子デバイスをテストする基本的な方法とタスクに精通し、生産における品質保証の一般的な理解を得るでしょう。 さまざまなテスト方法の長所と短所に特に注意が払われます。

生産テストの種類。 短いレビュー

一般的に、生産中の電子製品の準備とテストのプロセスは次のようになります。

- JTAG / ICTテストを使用したファームウェアおよびテスト用のスタンドの設計と作成

- 生産における品質管理と受け入れのためのテストとパラメーターのシステムの開発

- 自動または手動の機能チェック

生産プロセス中のデバイスとその個々の部品のテストは、次の方法と技術に基づいて実装できます。

1.視覚的自動制御( AOI 、 AXI )は、受託製造で使用される予備の品質チェックです。X線放射を使用して目に見えない場所や標準の光学システムをチェックするなど、プリント基板のインストールのさまざまな段階で行われます。

写真:回路基板は視覚的な自動制御( AOI )を受けています。 テスト結果に基づいて、テスターは検出された欠陥に関するデータを受け取ります。 出典: Acculogic

2.インサーキットテスト( ICT / FICT ) -プリント回路基板上の接続とコンポーネントのチェック、回路全体または個々のセクションの電気パラメーターの分析。

この方法では、プローブと実装ボードのノードとの接触を使用します。固定接触フィールド(「釘のベッド」、英語-釘のベッド)、または「フライングプローブ」(フライングプローブ)または「フライングマトリックス」のいずれかです。 多くの場合、複雑で高価な機器の使用、技術トレーニング、特別な機器の製造が必要です。

写真:フライングプローブを使用したプリント基板のテスト。

出典: Acculogic

3.周辺/境界スキャン(境界スキャン) -JTAGを使用したテスト。 マイクロチップでのIEEE 1149標準の使用に基づいています。

4.機能テスト( FCT ) -特定の機能のパフォーマンスおよびデバイスの仕様に定められたパラメーターへの準拠について、組み立てられたデバイスまたは部分的に組み立てられたデバイスの検証。

これらすべての方法により、製造プロセス中に電子機器の品質を評価できますが、場合によっては、デバイスのテストは最終段階でのみ実行されます。 このいわゆる最終最終アセンブリテスト ( EOL )は、機能と仕様のテストです。 品質だけでなく、デバイスの安定性と信頼性も評価されます。 このような電子機器の分析は、テスト対象のデバイスが動作するシステムをシミュレートする高度なベンチ装置を使用して実行されます。 そのようなチェックの結果に従って、不合格率が予備推定値を超える場合、生産技術が調整され、デバイスの次の試用バッチが開始されます。 そのため、数回の反復で。

実際には、最高の結果は、生産プロセスで使用される技術によって示されます。 機能およびインサーキットテスト、 情報をすばやく取得し、問題が発生する特定の段階を判断できます。 これにより、デバイスの最終組み立て前であっても生産プロセスを調整できます。

一般的なものから特定のものまで、これらのテスト方法をより詳細に検討します。組み立てられたデバイスまたは部分的に組み立てられたデバイスの機能の分析から始まり、プリント回路基板のインサーキットテストの機能で終わります。

本番環境での機能テスト

機能テストは、手動モードと自動モードの両方で実行できます。 当然、テスト計画を作成する際、手作業を最小限に抑え、オペレーターはデバイスの接続/切断のみを行い、適合性を監視します。

有能なアプローチにより、この技術は記録的な時間でデバイスのほぼすべての機能をカバーできます。 ただし、テストソフトウェアの開発と特別な機器の製造は不可欠です。

テストは、デバイスの主要部分(プロセッサ、メモリ、その他のモジュール)の確認と周辺機器インターフェイスの確認に分けられます。 プロセッサ部分をテストするために、特別な操作パラメーターを自動的に設定し、すべてのデバイスのマイクロ回路を初期化し、それらに問い合わせて、結果に基づいて操作性について結論を出す特別なプログラムが作成されます。 主要部分を確認した後、デバイスの各コンポーネント部分の動作モードが順次オンになり、その機能が確認されます。 たとえば、イーサネットインターフェイスをテストするために、プログラムは各ポートを交互に初期化し、複数ある場合は、一時的なMACアドレスとIPアドレスを設定し、パケットを転送して結果を分析します。

製品のテスト対象範囲は、モジュールとインターフェイスのテストに使用できる電気回路の分析に基づいて、デバイスの種類ごとに個別に決定されます。

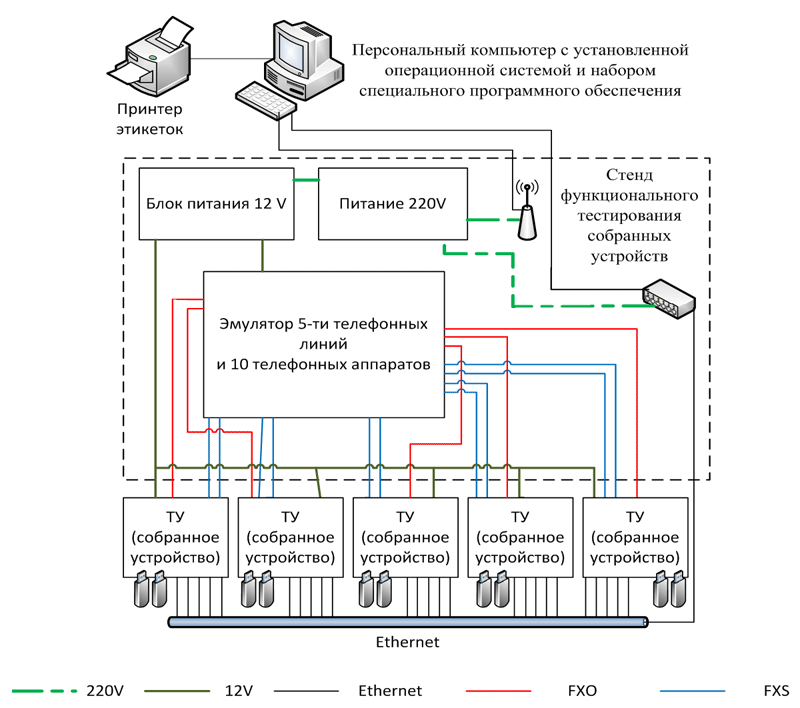

図:組み立てられたデバイスの機能テストスタンド

上記は、組み立てられたデバイスの機能テストベンチの図です。 5つのデバイスを同時にテストし、それぞれのすべての機能を順番にチェックできます。 このプロセスでは、個々のモジュールのファームウェアバージョンがチェックされ、必要に応じて、最新バージョンのファームウェアがパスします。 テストに合格すると、プログラムはデバイスにMACアドレス、シリアル番号、事前定義されたパスワードを提供します。

機能テストベンチには、デバイスのパーソナライズ、テスト済みデバイスに関する情報のリモート収集、および欠陥レポートの生成のための補助ソフトウェアとハードウェアが含まれる場合があります。

写真:シンガポールの工場で組み立てられたデバイスの機能テスト。

スキャン結果はコンピューターモニターのスタンドに同時に表示されます

7つのデバイスが接続されています。

機能テストの議論の余地のない利点には、最終ファームウェア、システムモジュールのソフトウェアバージョンの確認と更新、高レベルプロトコルと高速インターフェイスを使用したデバイスへの個人データの発行の可能性が含まれます。

機能テストスタンドは、企業の自動システム(生産)に組み込まれ、生産現場からの統計情報の収集と収集、および品質管理を提供できます。

このデバイスチェック方法の主な欠点は、周辺機器のスキャンとは対照的に、特殊な機器とライティングソフトウェアを製造する必要があることです。また、機能テストでは、欠陥のある回路とコンポーネント出力を正確に示しません。 しかし、ほとんどの場合、これらの作業の実施は、最大のカバレッジと短いテスト時間のために正当化されます。

周辺機器のスキャンを使用した実稼働環境での電子デバイスのテスト

次に、機能テストの段階の前であっても、インストールの品質を制御し、デバイスを拒否できる次のテスト方法を検討します。 これはJTAGテストです。

周辺スキャン(境界スキャン)のテストは、開発されたデバイスの品質を向上させ、大量生産の段階でコストを節約できます。 このテクノロジーの主な利点は、BGA、COB、およびQFPパッケージの超小型回路の出力へのアクセスが制限されているデバイスをテストできることです。

最近、JTAG標準が広く使用され、それに応じてチップがサポートされているため、周辺機器のスキャン方法がより利用しやすくなっています。

チップメーカーは、製品に周辺スキャンレジスタのアーキテクチャに関する情報を含むBSDLファイルを添付しています。 JTAGテスト用の最新のソフトウェアツールを使用すると、CAD回路図データを使用してプロセスを自動化できます。 これにより、JTAGテストの準備と使用が簡単になります。

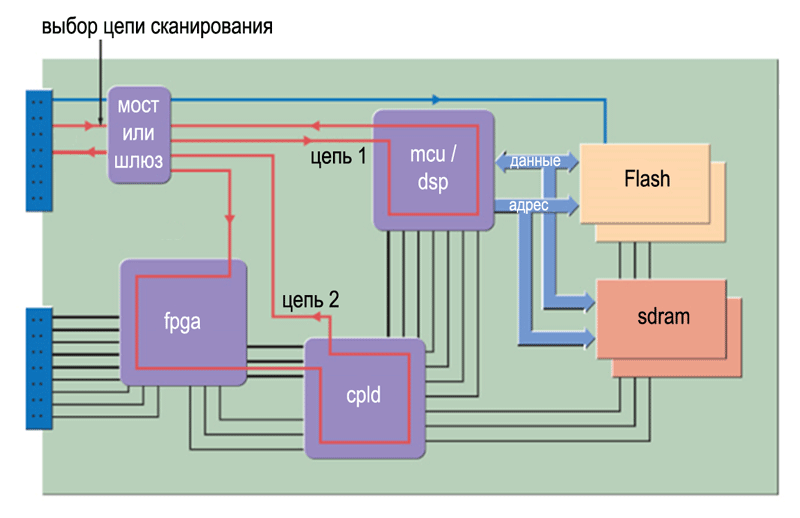

図:JTAGテストの例。 ここでは、テスト対象のチップのバスに接続されているがJTAG標準を直接サポートしていないコンポーネント(フラッシュメモリやSDRAMなど)を確認する方法を確認できます。

電子デバイスを設計するときは、製品回路の準備が必要です。 少なくとも、これはIEEE 1149.1標準をサポートするコンポーネントの使用、これらのコンポーネントの正しい接続、外部接点またはコネクタへのJTAGポートの出力です。

JTAGテストを使用すると、BGA、短絡、破損、デジタルインターフェイスを含む破損したマイクロ回路など、さまざまなタイプのケースを持つデジタルマイクロ回路の出力の「電力不足」を特定できます。 未検証のボードがプログラミング段階に進むと、メモリと周辺機器の起動に問題が発生する可能性があるため、これらすべての欠陥を識別することが非常に重要です。 この場合、問題の原因を特定することは困難です:不適切なソフトウェア設定またはインストールの失敗。 JTAGテストは、この問題の防止に役立ちます。

ただし、JTAGテストには欠点があります。 まず、これは機能テストに比べてパフォーマンスが低いことです。 第二に、この方法はデジタルエレクトロニクスのテストを目的としているため、デバイスのアナログ部分は除外されます。 第三に、JTAGテストではリンクの整合性のみがチェックされ、品質はチェックされないことを考慮することが重要です。 インピーダンス、浮遊容量など -これらの品質パラメータはすべて、高速回線の動作に大きな影響を与える可能性があります。

JTAGテストには、他にも多くの制限があります。

- JTAGをサポートしていないデジタルまたはアナログ要素に関連するインストールの欠陥を検出することは不可能であり、それらの間の接続欠陥の診断も利用できません。

- 機能テストまたは特定の時間関数である障害の検出を目的としたテストを実行することはできません。

- たとえば、ジッタ、スプリアス接続(クロストーク)、干渉などのデータバスの欠陥を検出することを目的としたテストを実行することはできません。 (PCIバスのテスト)。

しかし同時に、JTAGテストには重大な利点があります。 これは、工業用ロットでの電子デバイスのスポットテスト用のマイクロチップとモジュールのパフォーマンスの詳細な分析です。 これは重要な追加であり、場合によっては、インサーキットテストを「ネイルベッド」または「フライングプローブ」に置き換えます。 JTAGを使用すると、他の方法と組み合わせて使用する場合、完全なテスト用に機器を最適化したり、統合アプローチでテストの時間を短縮したりできます。

また、電子デバイスの小型化の要件が大きくなるにつれて、JTAGテストではプリント基板の寸法が小さくなり、「ネイルベッド」を使用したインサーキットテストのためにパッドのグループを配置する必要がなくなります。

写真:「釘の床」を使用したインサーキットテスト。 出典: Spea

インサーキットテスト

JTAGテクノロジを使用した周辺機器のスキャンはますます人気を集めていますが、20世紀の70年代から80年代にかけて開発が開始された古典的なインサーキットテスト方法は、今日でも成功裏に適用されています。

インサーキットテストは、特別な機器(ICTステーション)および機器(ニードルアダプター)を使用して、ボード上の個々のコンポーネントまたは回路の断片をチェックする技術です。 このテスト手法により、個々のコンポーネントと回路のアナログ部分を分析することができます。 また、大規模生産での使用にも成功しています。 つまり 他の最新技術が失敗した場合。

条件付きインサーキットテストは、アナログとデジタルに分けることができます。 アナログインサーキットテストでは、通常、次の特性がチェックされます:

- 短絡および断線の存在;

- 個別部品の公称値(抵抗、コンデンサ、インダクタンス、個別半導体デバイス);

- マイクロサーキットの可用性と正しいインストール。

このテスト方法を使用すると、アセンブリの多数の欠陥を検出できるため、アナログ回路内テストは多くの場合、生産欠陥分析と呼ばれます。

デジタルインサーキットテストでは、デジタル回路が真理値表と照合されます。

この技術は、テスト対象のコンポーネントの接点と針の物理的接触に基づいているため、このアプローチをテストに実装する際に多くの困難が生じます。

コンポーネントの絶え間ない小型化は、とりわけ、コンタクトパッドの物理的寸法とハウジングの下でのそれらの動きの減少につながります。 また、多層プリント回路基板では、かなりの数の接続が内層に実装されています。 これはすべて、ICTアダプター用のパッドをボードのいずれかの側面に出力する必要につながります。これにより、寸法が大きくなり、ルーティングが複雑になります。また、高周波バスの場合、これは原則として不可能です。

これらの問題の解決策の1つは、「フライングプローブ」または「フライングマトリックス」を使用したテスト方法を使用することです。 このアプローチにより、テスト用の特別なコンタクトパッドの必要性から逃れることができますが、テスト時間は大幅に増加します。これは大量生産の大きな制限です。

写真:「フライングプローブ」を使用してプリント基板をテストする別の例。 出典: Acculogic

プリント回路基板のテストおよびテスト時までにカバレッジ密度を損なうことなくインサーキットテストの技術を最適化するもう1つのおそらくおそらく主な方法は、JTAGテストと従来のICTテストを組み合わせることで構成される統合アプローチです。 このアプローチは、テストでプリント回路基板のカバレッジを予備計算し、それらをJTAGとICTに分配するときに、ICTニードルの設置場所の数を最小限に抑えることができるため、テスト可能なボードの簡素化とコスト削減を実現します。 そのような方法を使用するには、電子デバイスの設計、電気回路のテスト容易性の分析、およびそれらの調整に対する適切なアプローチが必要です。

Printscreen:テストカバレッジレポートの例。 出典: Acculogic

結論

したがって、テスト方法の選択を決定する主な基準を策定できます。

- 生産規模。

- 製品の複雑さ。

- 特別な品質要件の存在(例:責任ある使用のための電子機器)。

そのため、たとえば、小さなバッチの比較的単純なデバイスの場合、機能テストを使用するだけで十分です。 最高速度を提供します。 JTAGテクノロジーをサポートするデジタルエレクトロニクスをテストするには、周辺機器のスキャンが最適です。これにより、生産プロセスをデバッグし、初期段階で調整することができます。

大量生産を計画する場合、すべてのテスト方法のパフォーマンスを考慮に入れる必要があります。したがって、テスト範囲を最大にして単一のデバイスをテストするための最小時間を得るために、これらの組み合わせを考慮する必要があります。 たとえば、多くの場合、速度特性の観点から、機能テストやフライングプローブテストよりも、ネイルベッドテストと周辺スキャンが推奨される方法です。

したがって、 生産中の電子機器の包括的なテストです 。 現在、さまざまな技術を適切な割合で組み合わせることは、品質をチェックおよび分析するための最良の選択肢です。 このため、テストの適合性とテストカバレッジの設計前の分析が重要になります。 これにより、各プロジェクトで上記のアプローチの適用性と使用の程度を最初に計画し、正当化することができます。

&nbsp

[!?]質問やコメントを歓迎します。 プロムワッドエレクトロニクスエンジニア、プロダクションサポートセンターが回答します。