私が遭遇し、かなり長い間解決してきた1つの問題の解決策をあなたと共有したいと思います。 そして、多くのさまざまな無線電子機器の専門家(私が支援と助言を求めた)と、無線電子機器に関する2つの国内および1つの外国のフォーラムは、この問題の解決に役立ちませんでした。

これを読んでいる人が、私が起きて長い間苦しんでいた「熊手に乗らない」ことを確認したい。

問題は、1つのIDCコネクタで複数のピンを使用できないことでした。 コネクタで複数のピン(2つ以上)が使用された場合、オシロスコープでテストすると、コネクタは無音でした。

判明したように、問題はSchematicを使用するときのQuartus IIの命名規則でした。

それが有用または興味深いだろうすべての人に-私は猫をお願いします。

問題のデモンストレーション

ターゲット(手作り)デバイスでもこの問題が発生しました。 しかし、明確にするために、クジラでアルテラDE1をデモンストレーションします(図1)。

図 1-アルテラDE1開発および教育委員会

Quartus IIのファイル「Altera_DE1_pin_assignments.csv」をダウンロードし、クジラからディスクから取得したFPGAピン(プロジェクト内の名前-FPGAのピン番号)を割り当てました。

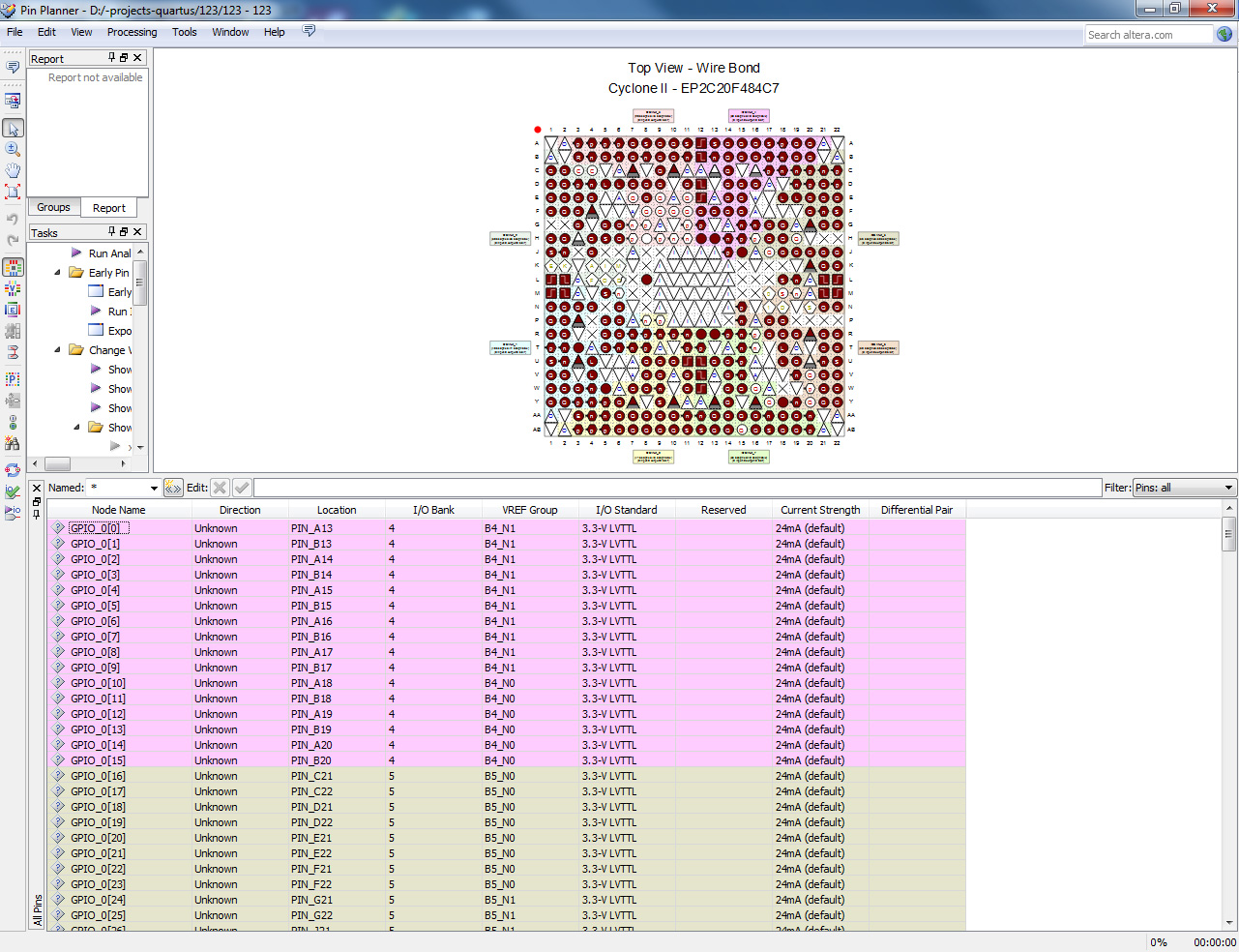

図2では、Pin Plannerで40ピンIDCコネクター「GPIO_0」のピン名を確認できます。

図 2-アルテラDE1用Quartus IIピンプランナー

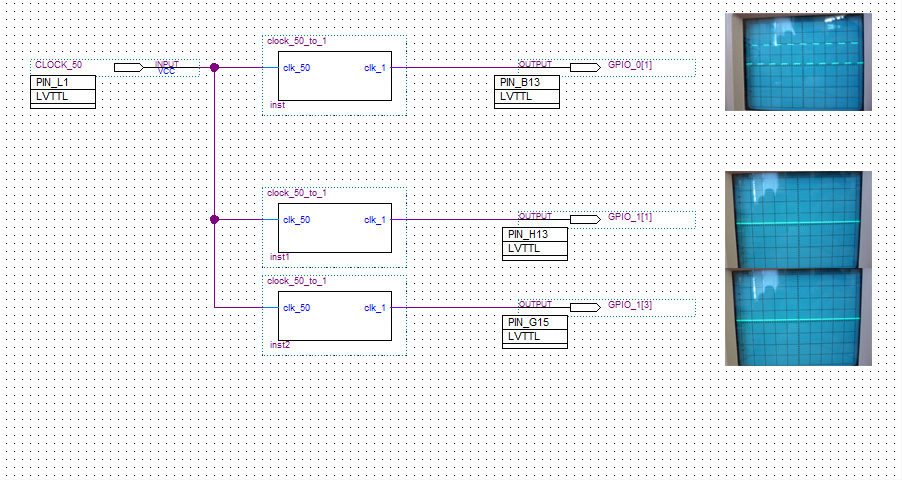

わかりやすくするために、図3に示すプロジェクトの問題を詳しく説明します。「CLOCK_50」ピンから、50 MHzブロックが(特定のFPGAピンに接続されたクジラのクロックジェネレーターから)来ます。 「Clock_50_to_1」は、Verilog言語の手書きモジュールで、カウンタを介して50 MHzクロックを1 MHzクロックに変換します(Quartus IIに組み込まれたALTPLLメガファンクションを使用すると同様の問題が観察されました)。 変換されたクロックは、2つのIDCコネクタ(GPIO_0およびGPIO_1)に出力されます。 GPIO_0コネクタでは1ピンが使用され([1])、すべてが機能しますが、GPIO_1コネクタでは2ピンが使用され([1]、[3])、信号はありません。

図 3-Quartus IIのスクリーンショットとオシロスコープの写真

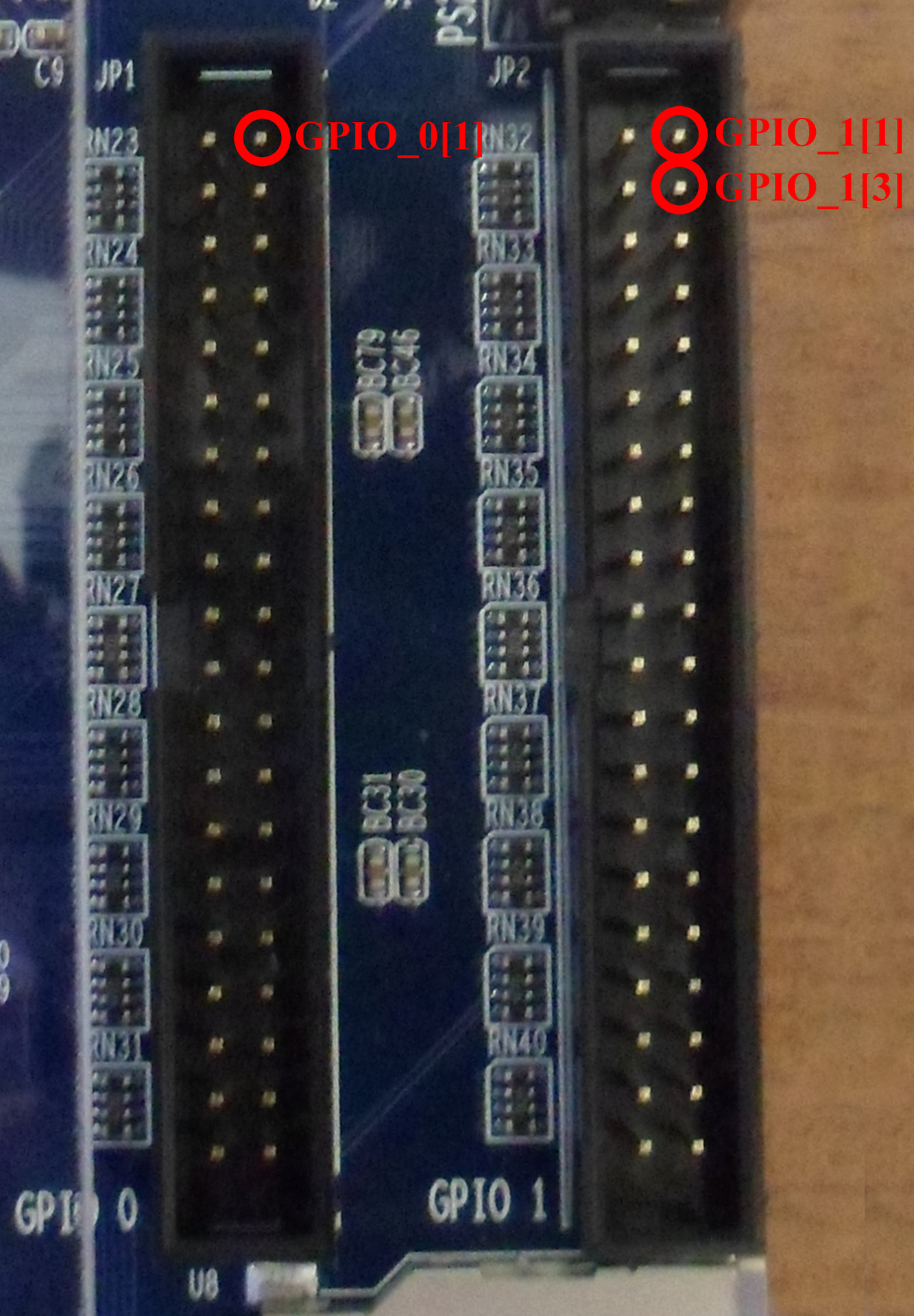

わかりやすくするために、スポイラーの写真はコネクタの写真を示しています。

問題の原因

アルテラフォーラムのユーザーの1人は、Quartus IIでプロジェクト(図3に示す)をコンパイルするときに「角を曲がった」いくつかの奇妙な警告に気付き、「これに遭遇したことはありません。プロジェクトの最上位モジュールは回路図ではなく、VerilogまたはVHDLです。

警告テキストは次のとおりです。

警告(275080):従来の命名規則を使用して、バス名「GPIO_1」の要素を変換しました。 元の名前ではなく、新しい名前に割り当てを行います。

警告(275080):「GPIO_1」という名前のバス上の変換された要素は、継承された命名規則を使用します。 元の名前ではなく、新しい名前に割り当てを行います。

-警告(275081):要素名を「GPIO_1 [1]」から「GPIO_11」に変換しました

-警告(275081):要素名を「GPIO_1 [1]」から「GPIO_11」に変換しています

-警告(275081):要素名を「GPIO_1 [3]」から「GPIO_13」に変換しました

-警告(275081):要素名を「GPIO_1 [3]」から「GPIO_13」に変換

クリティカル警告(169085):合計4つのピンのうち2つのピンに正確なピン位置の割り当てがない

特別な重要性の警告(169085):ピンの正確な位置は、合計4ピンのうち2ピンに割り当てられていません

-情報(169086):ピンGPIO_11がデバイスの正確な場所に割り当てられていません

-情報(169086):デバイスのピンGPIO_11の正確な位置が割り当てられていません

-情報(169086):ピンGPIO_13がデバイスの正確な場所に割り当てられていません

-情報(169086):デバイスのピンGPIO_13の正確な位置は割り当てられていません

警告(275080):「GPIO_1」という名前のバス上の変換された要素は、継承された命名規則を使用します。 元の名前ではなく、新しい名前に割り当てを行います。

-警告(275081):要素名を「GPIO_1 [1]」から「GPIO_11」に変換しました

-警告(275081):要素名を「GPIO_1 [1]」から「GPIO_11」に変換しています

-警告(275081):要素名を「GPIO_1 [3]」から「GPIO_13」に変換しました

-警告(275081):要素名を「GPIO_1 [3]」から「GPIO_13」に変換

クリティカル警告(169085):合計4つのピンのうち2つのピンに正確なピン位置の割り当てがない

特別な重要性の警告(169085):ピンの正確な位置は、合計4ピンのうち2ピンに割り当てられていません

-情報(169086):ピンGPIO_11がデバイスの正確な場所に割り当てられていません

-情報(169086):デバイスのピンGPIO_11の正確な位置が割り当てられていません

-情報(169086):ピンGPIO_13がデバイスの正確な場所に割り当てられていません

-情報(169086):デバイスのピンGPIO_13の正確な位置は割り当てられていません

つまり、警告を分析すると、Quartus IIの名前が変更されていることが明らかになりました。

「GPIO_11」の「GPIO_1 [1]」

「GPIO_13」の「GPIO_1 [3]」

また、GPIO_11およびGPIO_13という名前の場合、特定のFPGAピンは割り当てられません。

これについてアルテラのナレッジベースが言っていること:

Max + Plus IIソフトウェアは、回路図でのバス名のサポートが制限されており、これらの制限内で機能するようにバス内の要素の名前を変更することがあります。

たとえば、Max + Plus IIソフトウェアは、バス名a [1..0]、b [1]、b [0]をそれぞれa1、a0、b1、b0に名前変更します。

Quartus IIソフトウェアは、当初、下位互換性のためにこの動作を保持していましたが、プロジェクトに自然なバス名(角括弧付き)を保存するメソッドをサポートするようになりました。

ただし、既存のプロジェクトのソフトウェア動作の変更を避けるため、Quartus IIはBDF(ブロックデザインファイル)およびGDF(グラフィックデザインファイル)プロジェクトファイルを継承するために古い命名規則を引き続き使用します。

新しい回路図の場合、Quartus IIソフトウェアはコンパイル時にプロジェクトに実際の名前(角括弧付き)を保存します。

Quartus IIバージョン7.1以前の命名規則:

(図の名前を変更するMax + Plus II):

バスa [0..3]がパーツに分割される場合、4つのピンが作成されます:a0、a1、a2、a3

Quartus IIバージョン7.2以降の命名規則:

(QUARTUS II名前変更図):

バスa [0..3]がパーツに分割される場合、4つのピンが作成されます:[0]、[1]、[2]、[3]

たとえば、Max + Plus IIソフトウェアは、バス名a [1..0]、b [1]、b [0]をそれぞれa1、a0、b1、b0に名前変更します。

Quartus IIソフトウェアは、当初、下位互換性のためにこの動作を保持していましたが、プロジェクトに自然なバス名(角括弧付き)を保存するメソッドをサポートするようになりました。

ただし、既存のプロジェクトのソフトウェア動作の変更を避けるため、Quartus IIはBDF(ブロックデザインファイル)およびGDF(グラフィックデザインファイル)プロジェクトファイルを継承するために古い命名規則を引き続き使用します。

新しい回路図の場合、Quartus IIソフトウェアはコンパイル時にプロジェクトに実際の名前(角括弧付き)を保存します。

Quartus IIバージョン7.1以前の命名規則:

(図の名前を変更するMax + Plus II):

バスa [0..3]がパーツに分割される場合、4つのピンが作成されます:a0、a1、a2、a3

Quartus IIバージョン7.2以降の命名規則:

(QUARTUS II名前変更図):

バスa [0..3]がパーツに分割される場合、4つのピンが作成されます:[0]、[1]、[2]、[3]

問題№1を解決する方法

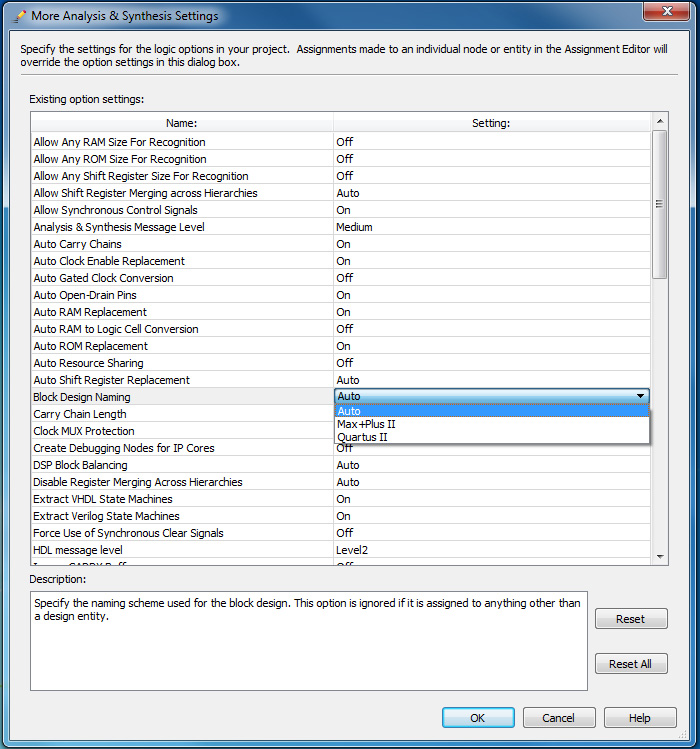

そこで、Max + Plus IIとQuartus IIの2つの名前変更スキームがあることがわかりました。

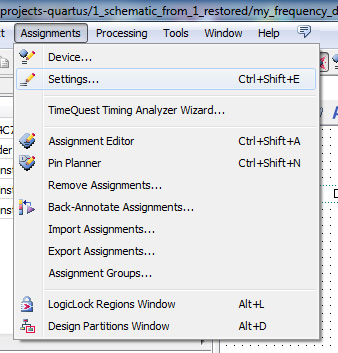

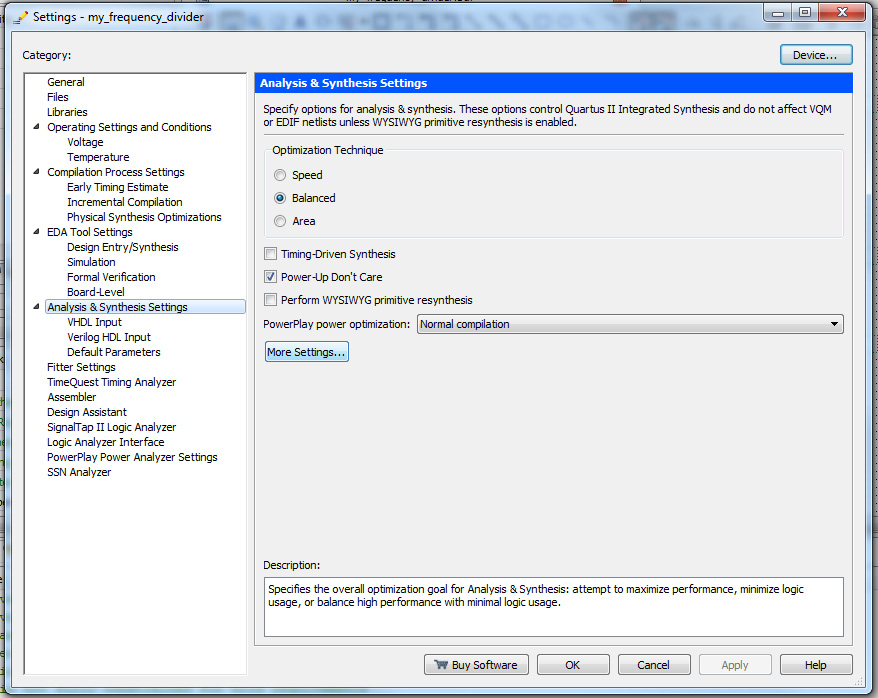

プロジェクトの場合、これらの命名規則スキームを明示的に切り替えることができます。

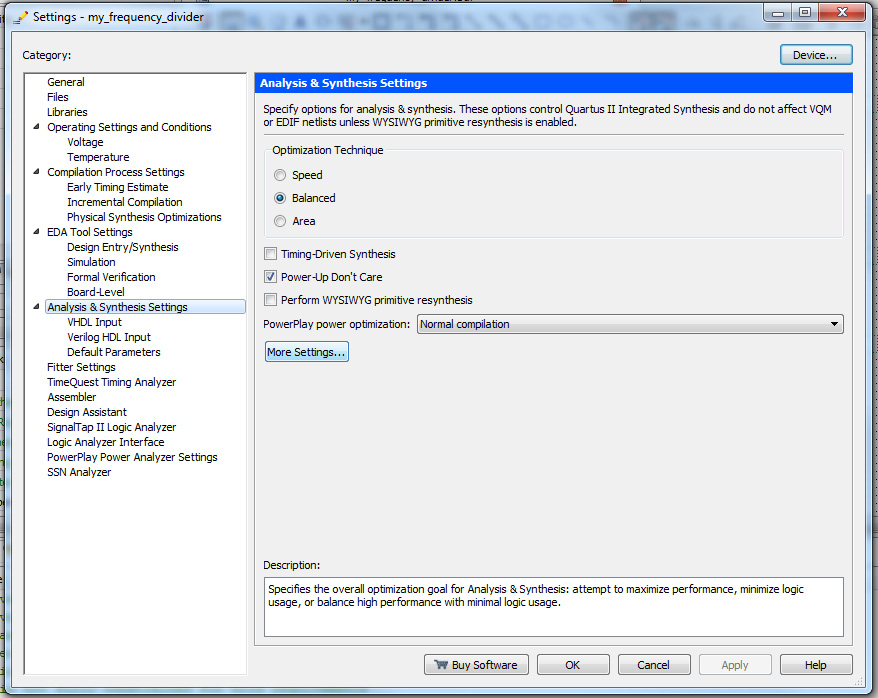

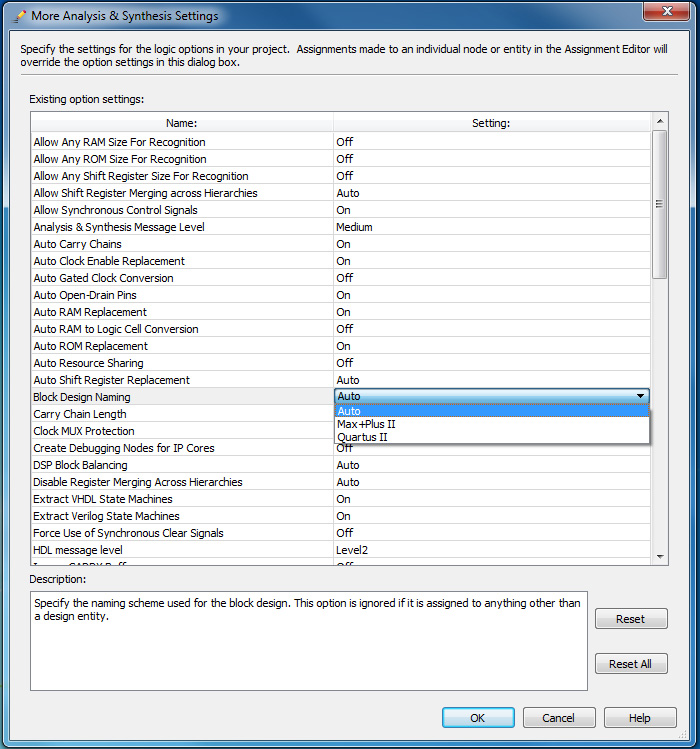

割り当て=>設定=>解析と合成の設定=>その他の設定=>ブロックデザインの命名

明確にするために、ネタバレでは、名前を変更するルールを段階的に切り替えるスクリーンショット:

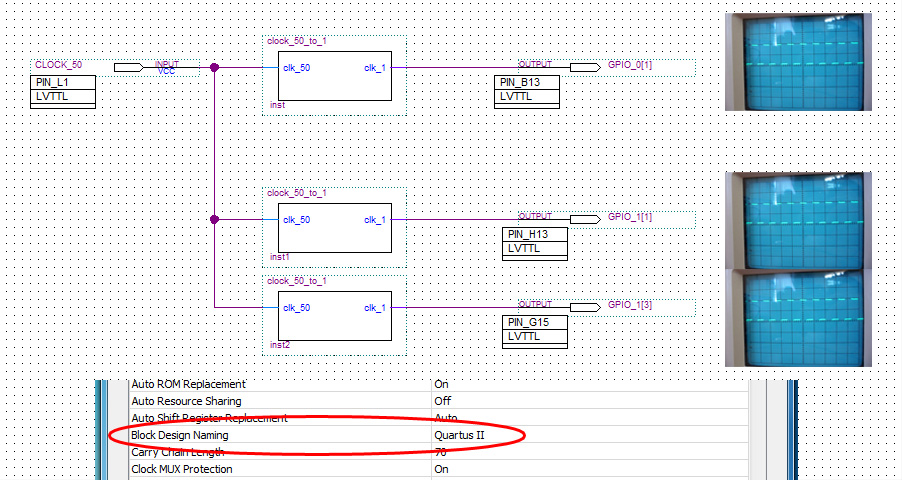

図4からわかるように、名前変更スキームを明示的にQuartus IIに切り替えると、問題は解決します。

図 4-Quartus IIのスクリーンショットとオシロスコープの写真

問題№2を解決する方法

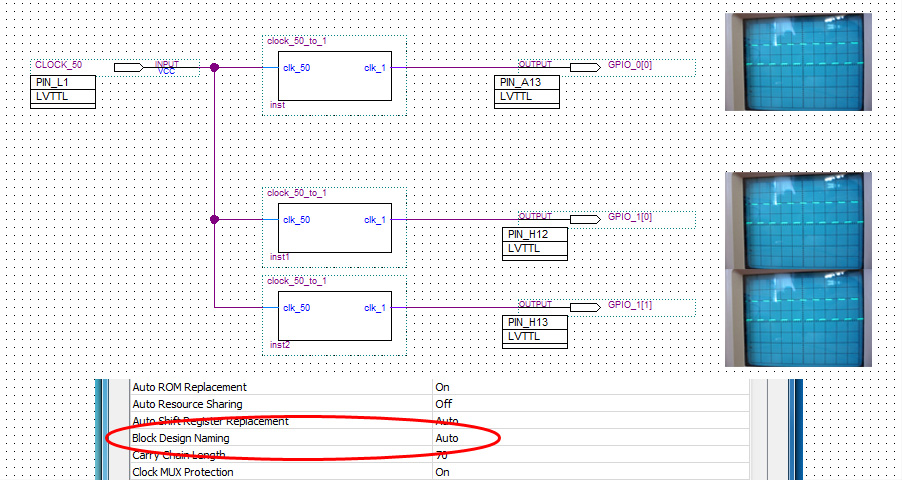

IDCコネクタのピンを順番に(0からnまで)使用し始めた場合、自動名前変更スキームが設定されていても、Quartus IIは名前を変更しません。

図 5-Quartus IIのスクリーンショットとオシロスコープの写真

わかりやすくするために、スポイラーの写真はコネクタの写真を示しています。

PS誰かの人生を楽にし、彼の時間を節約できれば、私はとても幸せです。