PCIバスには多くのトランザクションがありますが、このトピックでは以下についてのみ説明します。

- 構成トランザクション

- I / Oトランザクション

- メモリアクセストランザクション

トランザクションを行う場合、2つのオプションが可能です。

- マスターがサウスブリッジの場合

- マスターがPCIバスに接続されているデバイスの場合

すでに起こったように、PCIバスを検討する場合、マスターデバイスをマスター、スレーブデバイスをターゲット(ターゲット)と呼びます。

マスターがPCIバスに接続されたデバイスである場合のトランザクションは別の記事に値するため、この記事ではマスターがサウスブリッジの場合のトランザクションのみを扱います。

したがって、バスを使用するには、次の信号が必要です。

entity main is Port ( clk : in std_logic; AD : inout std_logic_vector(31 downto 0); IDSEL : in std_logic; CBE : in std_logic_vector(3 downto 0); FRAME : in std_logic; IRDY : in std_logic; TRDY : inout std_logic; STOP : inout std_logic; PAR : inout std_logic; RST : in std_logic; DEVSEL : inout std_logic ); end main;

clk(クロック)-PCI上のすべてのトランザクションの同期を提供し、各PCIデバイスの入力でもあります。

AD(アドレスとデータ)-バスのアドレスとデータを多重化します。

IDSEL(初期化デバイス選択)-初期化デバイスの選択。構成の読み取りおよび書き込みトランザクション中にチップを選択するために使用されます。

CBE(バスコマンドおよびバイトイネーブル)-バスコマンドおよびバイト解像度。

FRAME(フレーム)-トランザクションの開始時にマスターによって信号が発行され、その期間が決定されます。 単相トランザクションの場合、FRAMEは常に1クロックサイクル続きます。 マルチフェーズトランザクションでは、トランザクションが完了する1サイクル前にFRAMEが削除されます。

IRDY(イニシエーター準備完了)-マスターの準備完了のシグナル。 ウィザードが現在のデータフェーズを完了する意思があることを示します。

TRDY(ターゲット準備完了)-ターゲットの準備完了の信号。現在のデータフェーズを完了するためのターゲット準備完了を示します。

STOP(停止)-このシグナルは、ターゲットが現在のトランザクションを停止する場合に発行されます。

PAR(パリティ)-ADおよびCBE回線のパリティ。

RST(リセット)-リセット信号。 非同期です。

DEVSEL(デバイス選択)-デバイス選択信号。

デバイスを操作する前に、初期化する必要があります。 したがって、構成トランザクション実行の機能を検討します。

構成トランザクション 一般的な情報。

OSからの構成トランザクションのビュー

PCでPCI構成トランザクションを生成するには、CONFIG_ADDRESSおよびCONFIG_DATAという名前の2つのI / Oポートを呼び出し、それぞれアドレス0CF8hおよび0CFChを使用し、PCIバスがプロセッサに直接または間接的に接続するホスト-PCIブリッジに含めます。

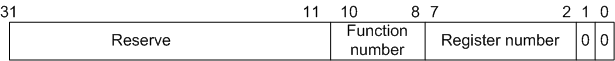

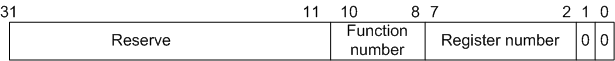

CONFIG_ADDRESSポートのサイズはダブルワードであり、ユニットとしてのみ使用可能です。 それに属するアドレスへのより小さい呼び出しは、通常のI / OトランザクションとしてPCIバスに転送されます。 このポートは読み取りと書き込みが可能で、次の形式があります。

構成トランザクションを実行する必要がある場合、PCI構成スペースレジスタのアドレスがこのポートに書き込まれ、バス番号(ビット23〜16)、デバイス(15〜11)、機能(10〜8)、およびレジスタ自体(7〜2)で構成されます。 ビット1と0には常にゼロが含まれ、最上位ビットには1が含まれている必要があります。これにより、構成トランザクションの実行が可能になります。 桁30〜24は予約されており、ゼロを含める必要があります。

実際には、構成トランザクションは、CONFIG_DATAポートの読み取りまたは書き込み、ホスト-PCIブリッジ、またはこのバスの下にあり、CONFIG_ADDRESSを介して接続されているPCIバスに対応するバスに対応する設定されたビットとバス番号を持つアドレスが書き込まれたときに生成されます1つまたは複数のPCI – PCIブリッジ(バス番号の有効範囲は、構成中にホスト– PCIブリッジによって指定されます)。 CONFIG_DATAポートへのアクセスは、アドレスがCONFIG_ADDRESSにある読み取りまたは書き込み構成レジスタと同じサイズでなければなりません。

CONFIG_ADDRESSで指定されたバス番号がホスト-PCIブリッジに直接接続されているバスの番号と一致する場合、タイプ0のアドレスを持つ構成トランザクションが生成され、CONFIG_ADDRESSポートのビット15〜11にあるデバイス番号がIDSEL信号の1つを発行するために使用されます。特定のデバイスを選択するために使用されます。 さらに、構成トランザクションのアドレスフェーズでデコードされたデバイス番号(1ユニットと残りのゼロビット)は、アドレスのビット31〜11で送信されます。

CONFIG_ADDRESSのアドレスが、ホスト-PCIブリッジに直接接続されている間違ったバスを示している場合、後者はタイプ1のアドレスで構成トランザクションを生成します。アドレスに含まれるバス番号を認識するPCI-PCIブリッジによって処理されます。 このブリッジは、タイプ0のアドレスで構成トランザクションを実行します(アドレス指定されたデバイスがこのブリッジに直接接続されたバスに接続されている場合)、またはタイプ1のアドレスでトランザクションを生成することにより、次のブリッジを通過するようにします このチェーンの長さは、理論的にはバス番号(8ビット)に割り当てられたフィールドのビット深度によってのみ制限されます。

トランザクション中に構成レジスタのアドレスが存在しないことが判明した場合(存在しないバス、デバイス、機能、またはレジスタの番号が示されている)、書き込み操作は何のアクションも実行せず、読み取り操作は各カテゴリのユニットを含む値をプロセッサに返します

トランザクションタイプ1のアドレス形式。

トランザクションのアドレス形式はタイプ0です。

CONFIG_ADDRESSポートのサイズはダブルワードであり、ユニットとしてのみ使用可能です。 それに属するアドレスへのより小さい呼び出しは、通常のI / OトランザクションとしてPCIバスに転送されます。 このポートは読み取りと書き込みが可能で、次の形式があります。

構成トランザクションを実行する必要がある場合、PCI構成スペースレジスタのアドレスがこのポートに書き込まれ、バス番号(ビット23〜16)、デバイス(15〜11)、機能(10〜8)、およびレジスタ自体(7〜2)で構成されます。 ビット1と0には常にゼロが含まれ、最上位ビットには1が含まれている必要があります。これにより、構成トランザクションの実行が可能になります。 桁30〜24は予約されており、ゼロを含める必要があります。

実際には、構成トランザクションは、CONFIG_DATAポートの読み取りまたは書き込み、ホスト-PCIブリッジ、またはこのバスの下にあり、CONFIG_ADDRESSを介して接続されているPCIバスに対応するバスに対応する設定されたビットとバス番号を持つアドレスが書き込まれたときに生成されます1つまたは複数のPCI – PCIブリッジ(バス番号の有効範囲は、構成中にホスト– PCIブリッジによって指定されます)。 CONFIG_DATAポートへのアクセスは、アドレスがCONFIG_ADDRESSにある読み取りまたは書き込み構成レジスタと同じサイズでなければなりません。

CONFIG_ADDRESSで指定されたバス番号がホスト-PCIブリッジに直接接続されているバスの番号と一致する場合、タイプ0のアドレスを持つ構成トランザクションが生成され、CONFIG_ADDRESSポートのビット15〜11にあるデバイス番号がIDSEL信号の1つを発行するために使用されます。特定のデバイスを選択するために使用されます。 さらに、構成トランザクションのアドレスフェーズでデコードされたデバイス番号(1ユニットと残りのゼロビット)は、アドレスのビット31〜11で送信されます。

CONFIG_ADDRESSのアドレスが、ホスト-PCIブリッジに直接接続されている間違ったバスを示している場合、後者はタイプ1のアドレスで構成トランザクションを生成します。アドレスに含まれるバス番号を認識するPCI-PCIブリッジによって処理されます。 このブリッジは、タイプ0のアドレスで構成トランザクションを実行します(アドレス指定されたデバイスがこのブリッジに直接接続されたバスに接続されている場合)、またはタイプ1のアドレスでトランザクションを生成することにより、次のブリッジを通過するようにします このチェーンの長さは、理論的にはバス番号(8ビット)に割り当てられたフィールドのビット深度によってのみ制限されます。

トランザクション中に構成レジスタのアドレスが存在しないことが判明した場合(存在しないバス、デバイス、機能、またはレジスタの番号が示されている)、書き込み操作は何のアクションも実行せず、読み取り操作は各カテゴリのユニットを含む値をプロセッサに返します

トランザクションタイプ1のアドレス形式。

トランザクションのアドレス形式はタイプ0です。

構成レジスタの形式:

レジスタの最小セット:

- ベンダーID-フィールドはデバイスのメーカーを識別します。 値0xFFFFを使用することは禁止されています。

- デバイスID-フィールドは特定のタイプのデバイスを識別します。 値0xFFFFを使用することは禁止されています。

- リビジョンID-デバイス識別子への追加。 ゼロになる場合があります。

- ヘッダータイプ-多機能デバイス用。 7番目のビットが0の場合、デバイスは単機能で、それ以外の場合は多機能です。

- クラスコード-読み取り専用 デバイスの一般的な機能を識別するために使用されます。 上位バイト(アドレス0Bh)は基本クラスを定義し、中央はサブクラス、下位はプログラムインターフェイス(標準化されている場合)を定義します。

- サブシステムID、サブシステムベンダーID-メーカーによって設定されます。 読み取り専用 カードとデバイスの正確な識別を可能にする識別子を保存します(システムにインストール可能)

一致するデバイスおよびメーカーID(デバイスIDおよびベンダーID)を持つ複数のカード。 - BAR0-BAR5-メモリおよび入力/出力ポートについて説明します。

メモリ領域とポートの説明は異なります:

- ビット0 = 0はメモリの兆候です。 サイズが2 GB以下

- ビット0 = 1-ポートエリアのサイン。 最大256バイトのサイズ。

エリアのサイズは次のように計算されます。 0xFFFFFFFFがBARに書き込まれます。 次に、BARから値が読み取られ、0xFFFFFFFFから減算されます。 結果は、領域のサイズです。 下位ビットの単位は考慮されません。

一般的な取引アルゴリズム

マスターは、ADバス上のデバイスアドレス、CBEバス上で実行されるコマンドを公開し、FRAME信号を0に設定し、IRDY信号を0に設定します。次に、マスターはターゲットがTRDYおよびDEVSEL信号を設定するのを待ちます。 また、ターゲットは、要求されたデータをADバスに公開します。 データは、IRDY、TRDY、およびDEVSELが論理ゼロのときに有効と見なされます。

実装

FPGAの結論にアクセスするには、特別なコンポーネントが必要です。Z-状態を操作するためのI / Oバッファー。

したがって、ADバスの場合、接続は次のようになります。

signal AD_I: std_logic_vector (AD'range); signal AD_O: std_logic_vector (AD'range); signal AD_T: std_logic; AD_BUF: for iCount in AD'low to AD'high generate begin IOBUF_AD : IOBUF generic map ( DRIVE => 12, IOSTANDARD => "PCI33_3", SLEW => "SLOW") port map ( O => AD_I(iCount), IO => AD(iCount), I => AD_O(iCount), T => AD_T ); end generate;

どこで

- O-バッファ出力。

- IO-FPGAピンに直接接続されたバッファの入力/出力。

- I-バッファ出力。

- T-入力制御、ユニットレベル-入力、ゼロレベル-出力。

残りの信号についても同様に、記事を煩雑にしないために引用しません。

上記で書いたように、トランザクションの開始時に、ADバスにアドレスが設定されると、FRAME信号は常にゼロになります。 以下は、AdrPhASE信号を生成するコードです。その間、後の作業のためにアドレスバスとコマンドバスをクリックする必要があります。 実際、AdrPhASE信号は、トランザクションの開始を一意に識別するFRAME信号の立ち下がりエッジにすぎません。

signal AdrPhASE: std_logic; signal FRAME_D: std_logic; signal Addres: std_logic_vector(AD_I'range); signal Command: std_logic_vector(CBE'range); signal bCfgTr: boolean; process (clk_i, RST_I) begin if (RST_I = '0') then FRAME_D <= '1' after cTCQ; elsif (rising_edge(clk_I)) then FRAME_D <= FRAME_I after cTCQ; end if; end process; AdrPhASE <= not FRAME_I and FRAME_D; process (clk_I, RST_I) begin if (RST_I = '0') then Address <= (others => '0') after cTCQ; Command <= (others => '0') after cTCQ; bCfgTr <= false after cTCQ; elsif (rising_edge(clk_I)) then if (AdrPhASE = '1') then Address <= AD_I after cTCQ; Command <= CBE_I after cTCQ; bCfgTr <= (IDSEL_I = '1') after cTCQ; end if; end if; end process;

さらに、装置全体の動作を機械を使用して説明できます。

機械コード

type TSM_PCI_T is (sIDLE, sDECODE, sCFG_READ, sCFG_WRITE, sIO_READ, sIO_WRITE, sMEM_READ, sMEM_WRITE); signal smPCI_T: TSM_PCI_T; process(clk_I, RST_I) begin if (RST_I = '0') then smPCI_T <= sIDLE after cTCQ; elsif (rising_edge(clk_I)) then case (smPCI_T) is when sIDLE => if (AdrPhASE = '1') then smPCI_T <= sDECODE after cTCQ; end if; when sDECODE => if (bCfgTr and Address(10 downto 8) = b"000" and Command(3 downto 1) = b"101") then if (Command(0) = '0') then smPCI_T <= sCFG_READ after cTCQ; else smPCI_T <= sCFG_WRITE after cTCQ; end if; elsif (Command(3 downto 1)= b"001") and (Addres(31 downto 8) = BAR0(31 downto 8))then if (Command(0) = '0') then smPCI_T <= sIO_READ after cTCQ; else smPCI_T <= sIO_WRITE after cTCQ; end if; elsif (Command(3 downto 1) = b"011") and (Addres(31 downto 16) = BAR1(31 downto 16)) then if (Command(0) = '0') then smPCI_T <= sMEM_READ after cTCQ; else smPCI_T <= sMEM_WRITE after cTCQ; end if; else smPCI_T <= sIDLE after cTCQ; end if; when sCFG_READ => if (IRDY_I = '0') then smPCI_T <= sIDLE after cTCQ; end if; when sCFG_WRITE => if (IRDY_I = '0') then smPCI_T <= sIDLE after cTCQ; end if; when sIO_WRITE => if (IRDY_I = '0') then smPCI_T <= sIDLE after cTCQ; end if; when sIO_READ => if (IRDY_I = '0') then smPCI_T <= sIDLE after cTCQ; end if; when sMEM_READ => if (IRDY_I = '0') then smPCI_T <= sIDLE after cTCQ; end if; when sMEM_WRITE => if (IRDY_I = '0') then smPCI_T <= sIDLE after cTCQ; end if; when others => smPCI_T <= sIDLE after cTCQ; end case; end if; end process;

上記を理解するために、CBEバス経由で送信される可能性のあるコマンドを示します。

- 0010 I / O読み取り

- 0011 I / O書き込み

- 0110メモリー読み取り

- 0111メモリ書き込み

- 1010構成の読み取り

- 1011構成の書き込み

各チームには、マシンの独自の状態があります。 これへの移行は、メモリおよびI / OポートにアクセスするトランザクションのCBEバスとADバスの現在の状態に依存します。 マスターからIRDY信号を受信すると、初期状態への出口が実行されます。

設定を読む

前述のように、デバイスの処理にはタイプ0のトランザクションが使用されますが、デバイスは単機能であるため、機能番号は000であり、制御マシンでチェックされます。 レジスタ番号(ADバスのビット7..0)に応じて、目的のレジスタが上の図に従ってADバスに発行されます。

構成読み取りコード

signal CfgRData: std_logic_vector(31 downto 0):=x"00000000"; signal CommandReg: std_logic_vector(15 downto 0) := x"0000"; signal StatusReg: std_logic_vector(15 downto 0) := x"0200"; signal LatencyTimer: std_logic_vector(7 downto 0) := x"00"; signal CacheLineSize: std_logic_vector(7 downto 0) := x"00"; signal BAR0: std_logic_vector(31 downto 0) := x"00000001"; signal BAR1: std_logic_vector(31 downto 0) := x"00000000"; signal InterruptLine: std_logic_vector(7 downto 0); process (clk_I) begin if (rising_edge(clk_I)) then case (Address(7 downto 0)) is when x"00" => CfgRData <= x"00017788" ; --Device ID and Vendor ID when x"04" => CfgRData <= StatusReg & CommandReg; --Status Register, Command Register when x"08" => CfgRData <= x"10000001"; -- Class Code and Revision ID when x"0C" => CfgRData <= x"0000" & LatencyTimer & CacheLineSize; -- BIST, Header Type(bit 7 = 0, single, bits 6-0 = 0, type0), Latency Timer(for masters), Cache Line Size (bit 2 in 1) when x"10" => CfgRData <= BAR0; -- Base Adress 0 (Register IO address decoder) when x"14" => CfgRData <= BAR1; -- Base Adress 1 when x"28" => CfgRData <= x"00000000"; -- CarfdBus CIS Pointer when x"2C" => CfgRData <= x"00017788"; -- Subsystem ID, Subsystem Vendor ID when x"30" => CfgRData <= x"00000000"; -- Expanxion Rom Base Address when x"34" => CfgRData <= x"00000000"; -- Reserved, Capabilitis Pointer when x"38" => CfgRData <= x"00000000"; -- Reserved when x"3C" => CfgRData <= x"004001" & InterruptLine; -- Max_Lat(only bus master), Min_Gnt, Interrupt Pin, Interrupt Line when others => CfgRData <= (others => '0'); end case; end if; end process;

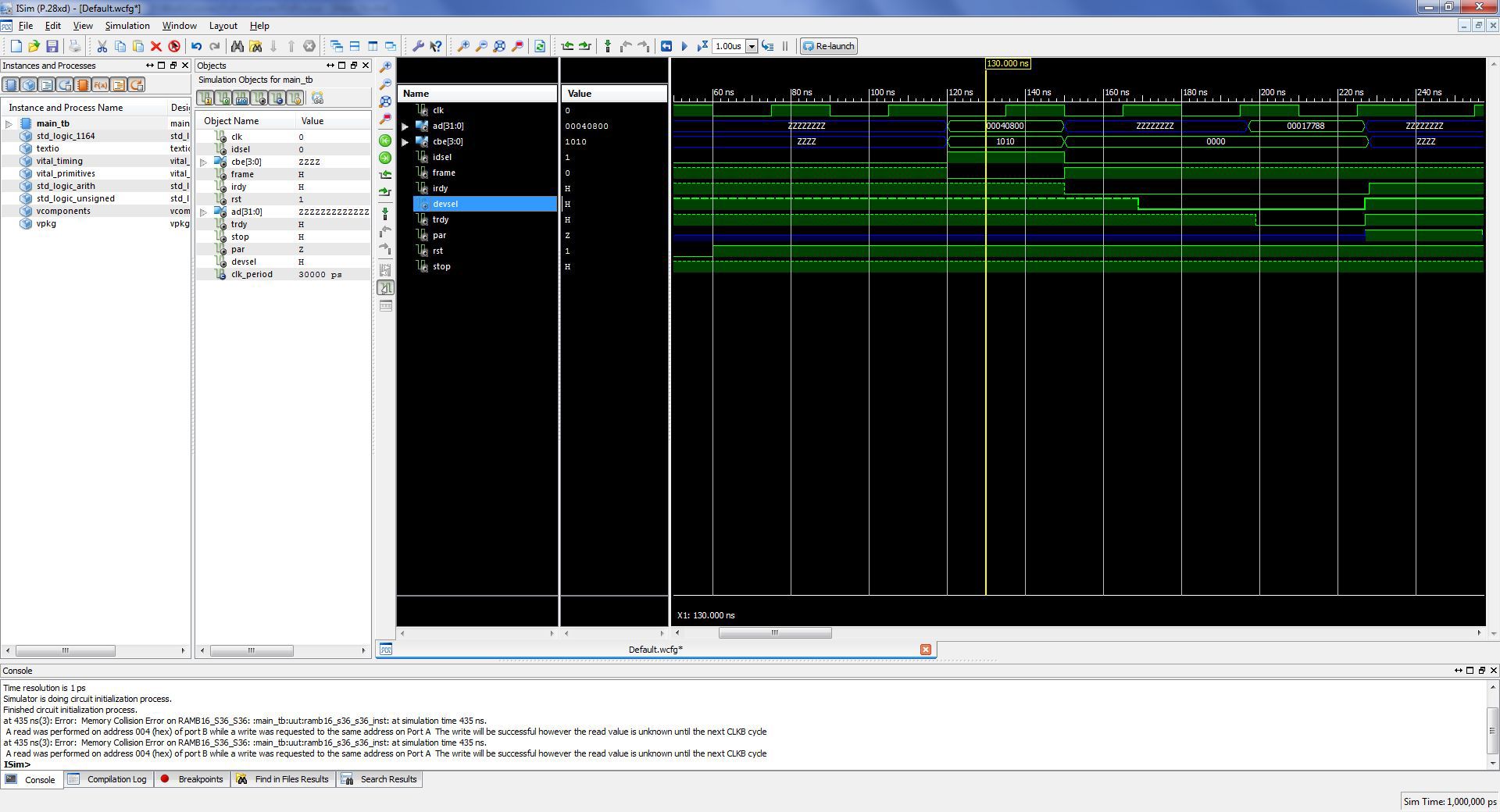

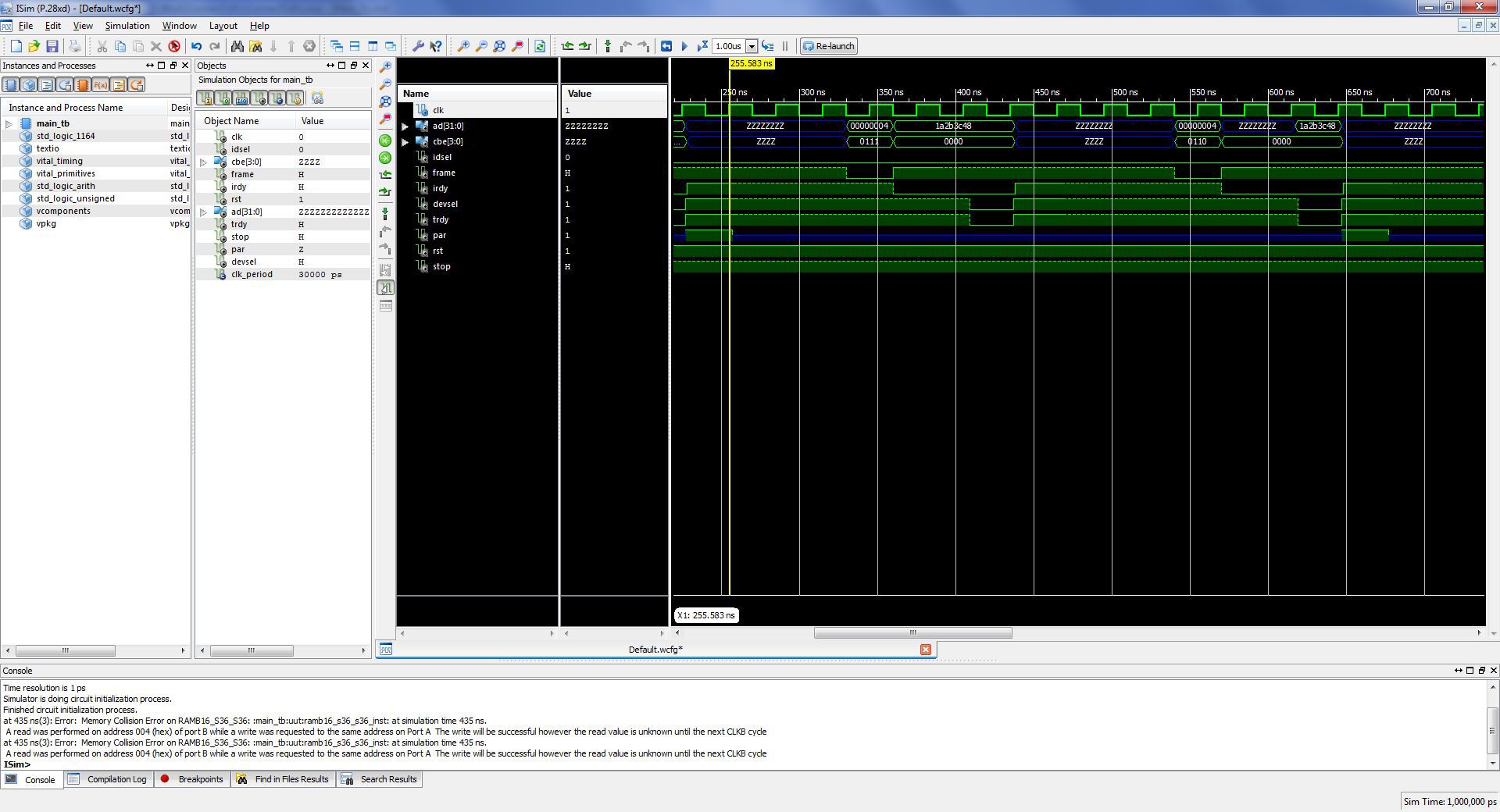

これは、シミュレーターで構成を読み取る方法です。

構成レコード

ADバスでは、マスターが記録用のレジスタアドレスを設定し、次のクロックサイクルで、書き込まれるデータが設定されます。 BAR0では、ビット7..0は読み取り専用で、BAR1では、ビット15..0は読み取り専用です。 したがって、I / Oアドレスは256、メモリアドレスは4,294,967,296です。

構成レコードコード

process(clk_I, RST_I) begin if(RST_I = '0')then CommandReg <= x"0000" after cTCQ; StatusReg <= x"0200" after cTCQ; LatencyTimer <= x"00" after cTCQ; CacheLineSize <= x"00" after cTCQ; BAR0 <= x"00000001" after cTCQ; BAR1 <= x"00000000" after cTCQ; elsif(rising_edge(clk_I)) then if (smPCI_T = sCFG_WRITE) then case(Address(7 downto 0)) is when x"04" => if (CBE_I(1) = '0') then CommandReg(15 downto 8) <= AD_I(15 downto 8) after cTCQ; end if; if (CBE_I(0) = '0') then CommandReg(7 downto 0) <= AD_I(7 downto 0) after cTCQ; end if; when x"0C" => if (CBE_I(1) = '0') then LatencyTimer <= AD_I(15 downto 8) after cTCQ; end if; if (CBE_I(0) = '0') then CacheLineSize <= AD_I(7 downto 0) after cTCQ; end if; when x"10" => if (CBE_I(3) = '0') then BAR0(31 downto 24) <= AD_I(31 downto 24) after cTCQ; end if; if (CBE_I(2) = '0') then BAR0(23 downto 16) <= AD_I(23 downto 16) after cTCQ; end if; if (CBE_I(1) = '0') then BAR0(15 downto 8) <= AD_I(15 downto 8) after cTCQ; end if; when x"14" => if (CBE_I(3) = '0') then BAR1(31 downto 24) <= AD_I(31 downto 24) after cTCQ; end if; if (CBE_I(2) = '0') then BAR1(23 downto 16) <= AD_I(23 downto 16) after cTCQ; end if; when x"3C" => if (CBE_I(0) = '0') then InterruptLine <= AD_I(7 downto 0) after cTCQ; end if; when others => null; end case; end if; end if; end process;

ポートへの書き込み

ADバスでは、マスターが記録用のレジスタ番号を設定し、次のクロックで書き込まれるデータが設定されます。

1つのレジスタを書き込むための例を示しますが、残りは同じ方法で書き込まれます。

signal IOReg0: std_logic_vector (31 downto 0); process(clk_I, RST_I) begin if(RST_I = '0') then IOReg0 <= x"00000000" after cTCQ; elsif (rising_edge(clk_I)) then if (smPCI_T = sIO_WRITE and Address(7 downto 0) = x"00") then if (CBE_I(0) = '0') then IOReg0( 7 downto 0) <= AD_I( 7 downto 0) after cTCQ; end if; if (CBE_I(1) = '0') then IOReg0(15 downto 8) <= AD_I(15 downto 8) after cTCQ; end if; if (CBE_I(2) = '0') then IOReg0(23 downto 16) <= AD_I(23 downto 16) after cTCQ; end if; if (CBE_I(3) = '0') then IOReg0(31 downto 24) <= AD_I(31 downto 24) after cTCQ; end if; end if; end if; end process;

読み取りポート

ADバスでは、マスターが読み取るレジスタ番号を設定します。 その後、デバイスは要求されたデータをADバスに発行します。

ポート読み取りコード

signal IORDate: std_logic_vector (31 downto 0); process (clk_I, RST_I) begin if (RST_I = '0') then IORDate <= x"00000000"; elsif (rising_edge(clk_I)) then case (Address(7 downto 0)) is when x"00" => IORDate <= IOReg0 after cTCQ; when x"04" => IORDate <= IOReg1 after cTCQ; when x"08" => IORDate <= IOReg2 after cTCQ; when x"0C" => IORDate <= IOReg3 after cTCQ; when x"10" => IORDate <= IOReg4 after cTCQ; when x"14" => IORDate <= IOReg5 after cTCQ; when x"18" => IORDate <= IOReg6 after cTCQ; when x"1C" => IORDate <= IOReg7 after cTCQ; when x"20" => IORDate <= IOReg8 after cTCQ; when x"24" => IORDate <= IOReg9 after cTCQ; when others => IORDate <= (others => '0'); end case; end if; end process;

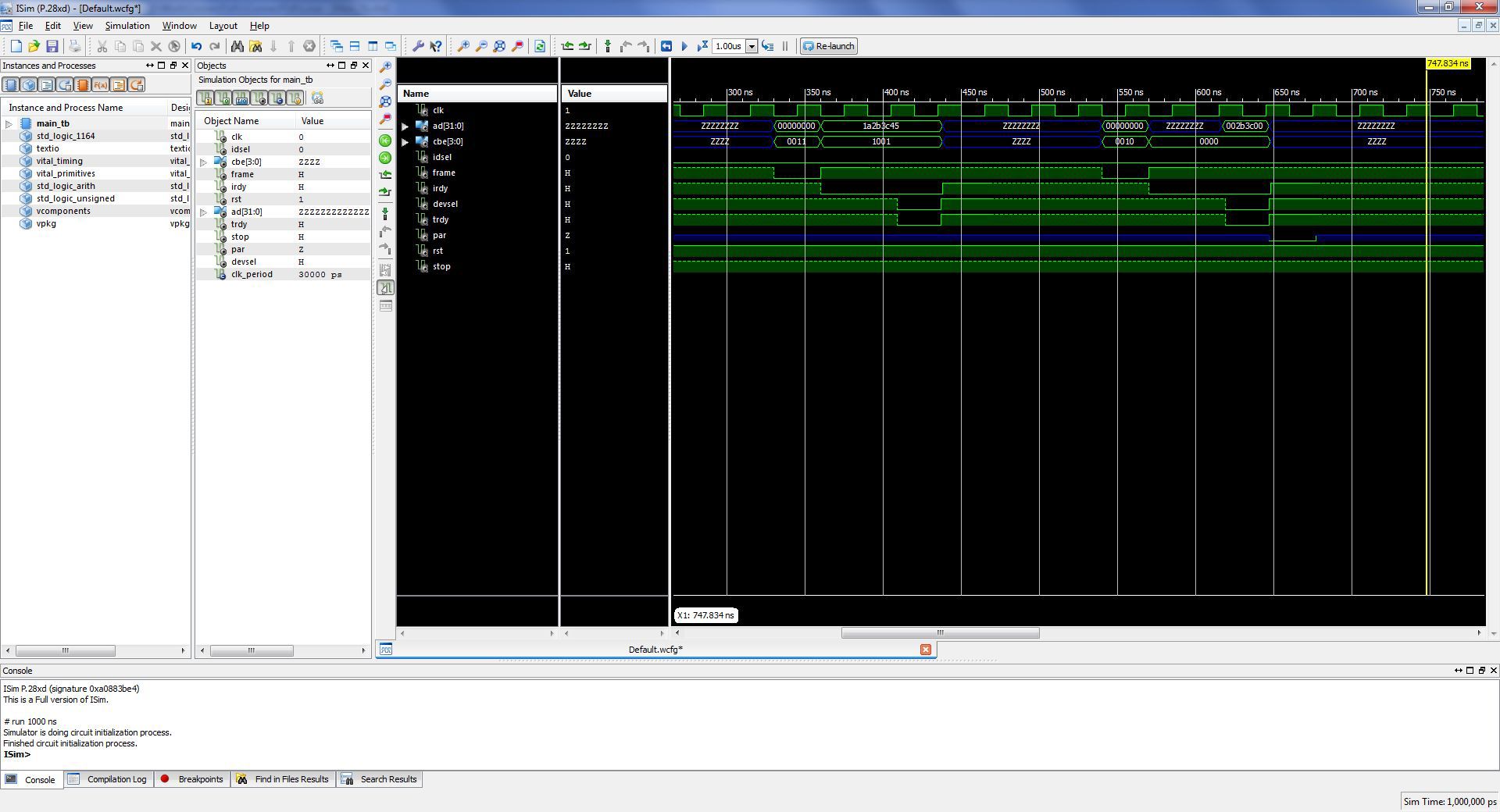

これは、入力/出力ポートの書き込みおよび読み取りの様子です。

メモリの書き込みと読み取り

ADバスでは、マスターはデータを書き込むアドレスを設定し、次のクロックでデータ自体を設定します。 ADバスで読み取る場合、マスターは読み取るアドレスを設定し、データ自体がADバスをターゲットにします。

データはポートAのRAMに書き込まれ、ポートBから読み取られます。

メモリアクセスコード

signal RamWrEn: std_logic; signal RamOutputDate: std_logic_vector (31 downto 0); signal RamInputDate: std_logic_vector (31 downto 0); signal RamRst: std_logic := '0'; RAMB16_S36_S36_inst : RAMB16_S36_S36 port map ( DOA => open, -- Port A 32-bit Data Output DOB => RamOutputDate, -- Port B 32-bit Data Output DOPA => open, -- Port A 4-bit Parity Output DOPB => open, -- Port B 4-bit Parity Output ADDRA => Address(8 downto 0), -- Port A 9-bit Address Input ADDRB => Address(8 downto 0), -- Port B 9-bit Address Input CLKA => clk_I, -- Port A Clock CLKB => clk_I, -- Port B Clock DIA => RamInputDate, -- Port A 32-bit Data Input DIB => x"00000000", -- Port B 32-bit Data Input DIPA => x"0", -- Port A 4-bit parity Input DIPB => x"0", -- Port-B 4-bit parity Input ENA => '1', -- Port A RAM Enable Input ENB => '1', -- PortB RAM Enable Input SSRA => '0', -- Port A Synchronous Set/Reset Input SSRB => '0', -- Port B Synchronous Set/Reset Input WEA => RamWrEn, -- Port A Write Enable Input WEB => '0' -- Port B Write Enable Input ); process(clk_I) begin if (rising_edge(clk_I)) then if (RST_I = '1') then RamRst <= '0'; else RamRst <= '1'; end if; end if; end process; process(clk_I, RST_I) begin if(RST_I = '0') then RamInputDate <= (others => '0') after cTCQ; RamWrEn <= '0' after cTCQ; elsif (rising_edge(clk_I)) then if (smPCI_T = sMEM_WRITE) then if (CBE_I(0) = '0') then RamInputDate(7 downto 0) <= AD_I( 7 downto 0) after cTCQ; end if; if (CBE_I(1) = '0') then RamInputDate(15 downto 8) <= AD_I(15 downto 8) after cTCQ; end if; if (CBE_I(2) = '0') then RamInputDate(23 downto 16) <= AD_I(23 downto 16) after cTCQ; end if; if (CBE_I(3) = '0') then RamInputDate(31 downto 24) <= AD_I(31 downto 24) after cTCQ; end if; RamWrEn <= '1' after cTCQ; else RamWrEn <= '0' after cTCQ; end if; end if; end process;

これは、シミュレーターでのメモリーの書き込みおよび読み取りの様子です。

ADバス上のデータは次のように出力されます。 マシンの状態に応じて、対応するレジスタが出力バッファに接続されます。

process (clk_I, RST_I) begin if (RST_I = '0') then AD_O <= (others => '0') after cTCQ; elsif (rising_edge(clk_I)) then if (smPCI_T = sCFG_READ) then AD_O <= CfgRData after cTCQ; elsif (smPCI_T = sIO_READ) then AD_O <= IORDate after cTCQ; elsif (smPCI_T = sMEM_READ) then AD_O <= RamOutputDate after cTCQ; end if; end if; end process;

ADバスにデータを発行するためのイネーブル信号は、次のように生成されます。

process (clk_I, RST_I) begin if (RST_I = '0') then AD_T <= '1' after cTCQ; elsif (rising_edge(clk_I)) then AD_T <= not b2l(smPCI_T = sCFG_READ or smPCI_T = sIO_READ or smPCI_T = sMEM_READ) after cTCQ; end if; end process;

DEVSEL信号の開発の例として、STSコンポーネントについても追加したいと思います。

DEVSEL_STS : entity WORK.componentIO(Behavioral) port map (iD => DEVSEL_O, oT => DEVSEL_T, clk => clk_I, rst => RST_I)

制御信号のアクティブレベルはゼロに等しいため、Z-状態に切り替えて回線を解放するには、まず論理ユニットのレベルを発行してから、Z-状態に転送する必要があります。

おわりに

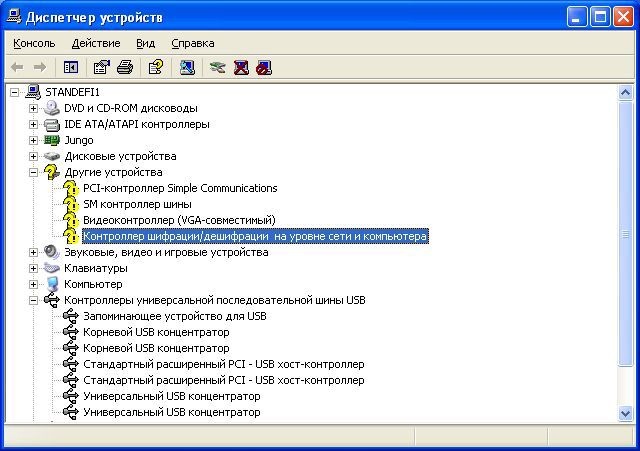

結論として、PCIバスでのトランザクションの実行は見た目ほど難しくありません。 開発されたファームウェアがFPGAにアップロードされました。 FPGAを搭載したボードがPCIスロットに挿入され、コンピューターの電源がオンになりました。 システムはボードを検出し、そのドライバーを要求しました。

うまくいく! :)

drive.google.com/file/d/0B-i4aT8Q0ZNxc1VkV3J2b0dTRlU/view?usp=sharingプロジェクト自体。 xilinx ise 14.2を開きます。