メーカーは、3つの大胆なマーケティングステートメントを作成しました。

- システムは書き込み、読み取りを問わず、速度は同じです。

- このすべてにより、応答時間は1か月の一定負荷の後でも250〜500マイクロ秒で安定しています。

- コンポーネントを「ホット」に取り出すことができます-システムには何も起こりません。

まず、スペースを数十個の仮想ボリュームに分割し、20/80モード(記録の80%)で4キロバイトのブロックで記録する多数のアプリケーションを起動しました。 そして、彼らはモジュールを5日間負荷をかけ続けました。 マーケティングが嘘をついていることが判明しました:記録速度はプレゼンテーションで述べられた1ミリ秒から非常に遠く、平均は0.4ミリ秒でした(40/60で0.25に達しました)。

その後、オフィスでのITディレクターのテストドライブ中に、実際の問題が発生し始めました。 実際、私は招待状で、災害復旧ソリューションのデモ中に何らかの形でデータセンターのラックを「ライブ」に削減し、その後、イベントを平和的に終了する機会はなかったと述べました。 聴衆は血を待っていたので、ドライバーでサービスエンジニアに電話しなければなりませんでした。

450k IOPSで、2人のファンを引き抜くことから始めました。 これは観客にほとんど感銘を与えませんでした。なぜなら、私は2つのコントローラーのうちの1つに行き、ヴァイオリンがそれに対して何を言っているかを見たかったからです。 2つのファンを差し引くと、システムがひどくうなります(残りは自動的に加速します)。そのため、エンジニアが2つのコントローラーの1つを取り出して、ハードウェアが3分の1の速度で「サンク」するだけで、「お母さん」のような音しか聞こえませんでした。

注意、トラフィック:カットシーンスキームとスクリーンショット。

同時に何がどのように機能し、そのような速度がどこから来るのかを知るには、遠くから始めなければなりません。 最新のフラッシュストレージのアーキテクチャについて十分に理解している場合は、システムアーキテクチャに直接スクロールします。 または、ある大手ホスティング会社の代表者が言ったように、「彼女が速いことは知っていますが、彼女が何をしているのかさえ知りません。」

はじめに

むかしむかし、そのような独立したストレージシステムはありませんでした。サーバーには、すべての情報が記録されたハードディスクがありました。 その後、より多くの情報を書き込む必要があり、その結果、磁気テープ、ディスクアレイ、およびフラッシュディスクアレイに作成された個別のストレージが割り当てられました。

さらに、プロセッサの開発速度は、ドライブの開発速度を大幅に上回りました。 ディスクアレイが徐々にボトルネックになりました。 ハードディスク自体の物理的なハードウェアの制限を考えると、追加の冗長性を備えた巨大な高速RAIDの組み立てを開始し、直接記録する前にアルゴリズムを最適化しました。 しかし、それでも頭の上に飛び越えることはできず、速度は基本的に数年間増加しませんでした。

その後、最初のフラッシュドライブが登場しました。 ここに非常に興味深い点があります。現在のインフラストラクチャを考えると、アーキテクチャ全体の各フラッシュドライブは、通常のハードドライブのレベルよりも高速でした。 つまり、フラッシュソリューションは古いハードドライブの代わりになりました。そして、記録コントローラーの前のテクノロジースタック全体は、ドライブボックス内に既に通常の磁気ディスクで動作していると考えていました。 そして、これはすぐにフラッシュテクノロジーに完全に不要な操作の巨大なオーバーヘッドを意味しました:たとえば、最適化アルゴリズムを備えたストレージキャッシュは完全に不要であり、単にデータの余分な遅延です(オフにしても、データは依然としてマイクロサーキットを「飛びます」)古典的なセクターの記録スキームは、完全に不必要なスローダウンにもつながりました。 同時に、フラッシュドライブ自体の記録方式が異なっていたため、HDDからフラッシュにインターフェイスを投げる、フラッシュとして書き込む、さらにガベージコレクターアナログを使用して記録するたびに、3回作業する必要がありました。 アプローチ自体は、市場でのSSDの普及によって変化していません-バス、キャッシュ、書き込みアルゴリズムに関するすべての同じ問題。

その結果、ある時点で、ヴァイオリンの人々はこの写真を見て、簡単な質問をしました:なぜフラッシュメモリチップが従来のHDDよりもDRAMに近い速度で動作し、同時に不揮発性である場合、間違いなく既存のアーキテクチャにねじ込まなければならないクラシックドライブの代わりにストレージ? 答えは、低レベルのプロトコルとハンドラーの巨大な時代遅れの艦隊にのみありました。 問題は、システム全体をゼロから開発する必要があることです。これは、時間とお金の重大な投資を意味します。

バイオリンのエンジニアはそれを止めませんでした、彼らはチップアーキテクチャへのアクセスを許可するフラッシュメモリ東芝のメーカーと契約を結びました。 その結果、しばらくして、多くの作業を行った後、SSDと比較しても非常に低い遅延レベルで、情報へのアクセス速度を大幅に向上させるサーバーストレージを作成することができました。

古い方法で動作していたスタック全体を削除するには、ディスクという概念自体を取り除く必要がありました。 その結果、フラッシュドライブとは言えないものができました。DRAMに似た自然なマイクロ回路がテーブルにあります。

フラッシュ制限

第一に、セルあたりの書き込みサイクル数が制限されています。 サーバー用の最初のフラッシュドライブは、1〜2か月の集中的な作業でストリーミングされていました。 しかし、場合によっては、ハードドライブを使用するよりも優れている場合があることに注意してください。ハードドライブは、メカニックのために予測不可能な瞬間に飛行する傾向があり、フラッシュドライブとマイクロチップは常に正確な障害点を認識し、事前に警告することができます

第二に、フラッシュドライブでは、従来の磁気ディスクとは異なり、古いデータの上に新しいデータを上書きする方法はありません。記録は空のセルでのみ行うことができます。 つまり、古典的な読み取りと書き込みに加えて、3番目の操作である消去が表示されます。 これは問題にならないようです。上書きする前にセルをクリアする必要がありますが、ここで主な危険性があります。読み取りと書き込みとは異なり、消去操作は非常に遅いです。 時々。

第三に、最初の2つの制限を回避することに成功した場合、3つ目が発生します。コントローラーが「ボトルネック」になる可能性があり、この経済全体を管理し、読み書き用のデータを準備する必要があります。

これらの制限を回避しないと、通常のSSDで電力が20〜40%増加するだけです。 周りを回れば、素晴らしい数字を達成できます。 ヴァイオリンはこれらの問題を非常に興味深いことに解決しました。

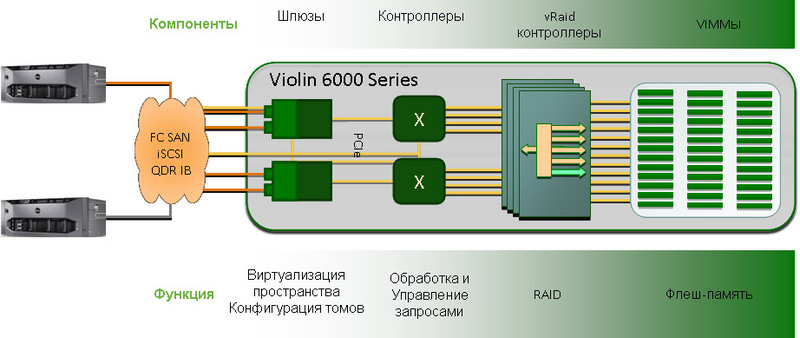

システムアーキテクチャを見てみましょう

これは、システム全体がどのように見えるかです

「フラッシュメモリファブリック」として指定されたエリアでは、大きな黒いファンが見ているマイクロ回路の巨大な山を見ることができます。 これは、このようなボード上のここにあるフラッシュメモリです。

個別のブリックフラッシュ工場。

1つのモジュールには、16個のチップフラッシュメモリ、複数のDRAMモジュール、1つの「ブリック」用の1つのFPGAカードがあります。 工場のレンガは最大64個です。 ボード内のすべてのデータ操作はFPGA上でローカルに実行されるため、これらの懸念事項を伴う外部コントローラーをロードする必要はありません。

これらのことの隣に4つの仮想RAIDコントローラーがあり、これらはRAID 3 4 + 1と同様のアルゴリズムを使用して、パリティによるデータ整合性の確保に関与しています。 デフォルトでは、コントローラーはメモリーカードをコントローラーごとに5個と1個のHotSpareの「責任」グループに分けます。 ただし、このパーティショニングはある程度「仮想」であり、各モジュールから各モジュールへの同じ速度のアクセスは、アレイのスイッチング構造によって常に保証されます。 従来のストレージアーキテクチャで言うように、バックエンドは完全に正直なアクティブ/アクティブです。

整合性メカニズムは、複数のメモリカードが次々に故障してもデータを保存します。主なことは、2つのRAID 1スロットが同時に「死ぬ」ことはなく、FLASHドライブでの再構築もはるかに高速になることです。 確かに、特殊な点があります:標準的な交換では、システムは破損したモジュールを認識し、自動的に電源をオフにします(または、インターフェイスからモジュールの電源をオフにすることができます)。その後、モジュールが引き出され、インターフェイスに新しいモジュールがインストールされてアクティブになります。 最も面白いのは何ですか-すべてを「ホット」に変更できます。 テスト中に、さまざまなアプリケーションで最大数百のボリュームを作成し、20分間隔で4つのモジュールを順次取り外しました(1つは緊急、3つはインターフェイスを介した予備シャットダウン)-すべてが時計のように機能しました。

アレイの電源のバッテリーやスーパーキャパシタなど、外部電源障害が発生した場合の特別な保護は提供されません。 これは、アレイが突然の停電から保護されていないことを意味するものではありません。最後のトランザクションをフラッシュにリセットするのに十分なエネルギーが電源ユニットに保存されており、十分な余裕があります。 電流が消えると、システムは残りのエネルギーを使用してFLASHにすべてのデータを40回以上記録できます。

ここからさらに進んで、アーキテクチャの観点から、アレイが外部と通信する方法を確認します。

システム構成

そのため、入力には、標準のSANインターフェイスを介してデータを送信するサーバーからのデータがあり、目的の速度と規模で外部ユニットを操作できます。 その後、データがゲートウェイに到着し、そこで有用な情報がPCIe x8ベースのトランスポートインフラストラクチャに送信されます(このような速度で動作するのに遅くなるものは原則として動作せず、必要な遅延レベルを維持しません)。4KBのブロックでvRAIDコントローラーに配信されます。 その後、パリティが計算され、5つのメモリプランクのうち1つ(プランクあたり1 KB)に書き込まれます。

トランスポートインフラストラクチャ(バイオリンの用語では仮想マトリックス)は完全に受動的であり、2つの冗長ACMモジュールによって制御されます。 これらのモジュールはアレイの純粋な制御要素であり、データ処理のロジックに直接関係せず、その機能は純粋に制御し、電源を「制御」し、システムの状態を監視します。 トランスポートインフラストラクチャは、コンポーネントの一部に障害が発生した場合でもViolinパッケージ内ですべてを通信する機能を提供しますが、パッシブボードをカウントできない限り、単一障害点を作成しませんが、障害の確率はデータセンターで火災が発生する可能性があるとします。

今、最も面白くて難しいこと:記録のためのフラッシュ技術の制限をどうするか? 解決策は一般に複雑ではありませんが、バイオリン開発者によると、この単純さは彼らに最も困難をもたらしました。 この問題は、データの関連性が失われた直後にセルを事前にクリーニングすることで解決されます。 次のように機能します:ご存知のように、各フラッシュメモリチップの実際の未処理容量は、宣言されているよりもはるかに多く、これは負荷プロファイルに関係なくセルを均一に劣化させるために行われます。したがって、物理レベルでは、チップへの各書き込みは新しいセルに行き、古いセルは使用可能としてマークされますレコード。 同時に、古いデータは元の場所に残るため、空のセルがない状態にすぐになり、各レコードの前にセルをクリーニングする必要があります。その結果、速度が壊滅的に低下します。

これがいわゆる SSDのパフォーマンスグラフのブレーク

バイオリンの動作は少し異なります。各チップのFPGAは各セルの情報の関連性を監視し、データが不要になった場合は、ガベージコレクターと呼ばれる特別なバックグラウンドプロセスでデータをクリーニングします。 したがって、各レコードは常に空のセルに移動します。これにより、パフォーマンスの低下が回避され、フラッシュメモリチップが読み取りだけでなく書き込みにも可能な限り効率的に使用されます。

アーキテクチャをもう一度見てみましょう。

- コントローラはデータを受信し、さらに送信します。

- 制御モジュールは、PCIe x8を介してすべてのコンポーネントを相互に交換し、コンポーネントの監視と制御を提供します。

- フラッシュファクトリは、データを個別のモジュールに分散し、ピークに応じてすべてのバランスを取り、さらに内部パスの均一な摩耗と冗長性を確保します。

FPGAチップ上のハードウェアに実装できるものすべて、つまり、通常とは根本的に異なるレベルの相互作用と処理速度が提供されます。

鉄定規

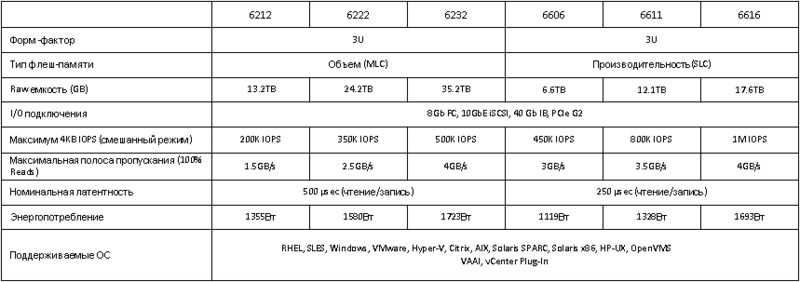

次に、別のメモリチップでさらに下を見てみましょう。 実際には、チップに記録するための2つの技術-SLCとMLCがあります。 SLCは、各メモリ位置に1ビット、MLC-さらに多くを格納します。 その結果、同じ物理チップ上で、SLCはより高速でより長いモジュール寿命を提供し、MLCはより多くのスペースを確保できることがわかりました。

この場合、依存関係が線形になる前に、SLCは2倍の速度で半分のスペースを提供しました。 ただし、賢いViolinソフトウェア(低レベルのデータ処理を掘り下げるのにほぼ2年を費やした)のおかげで、MLCはSLCとは書き込み速度が約50%異なります。 バイオリンの統計によると、MLCチップのリソースも増加します。最大書き込み負荷であっても、メモリモジュールは少なくとも4〜5年は存続します。

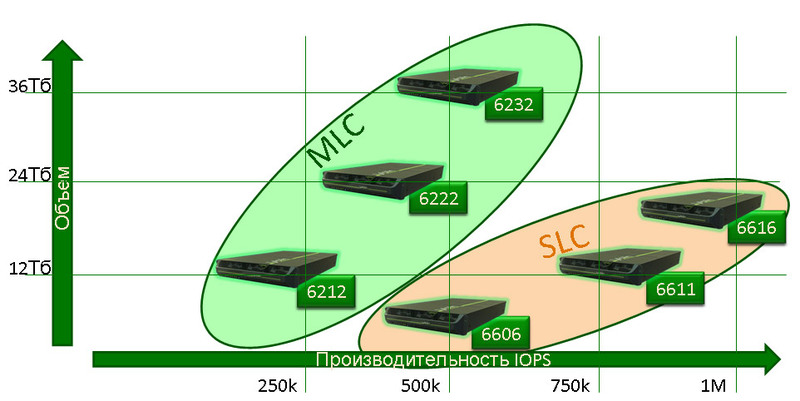

場所の規模と作業速度に応じた新世代のラインナップは次のとおりです。

表の違いは次のとおりです。

これはデータセンターでどのように見えるかです:

設置時-3Uケースのすべてのアレイ、電力-480ワットの2ブロック、放熱-強力な3 Uサーバーのように。

インターフェースと管理

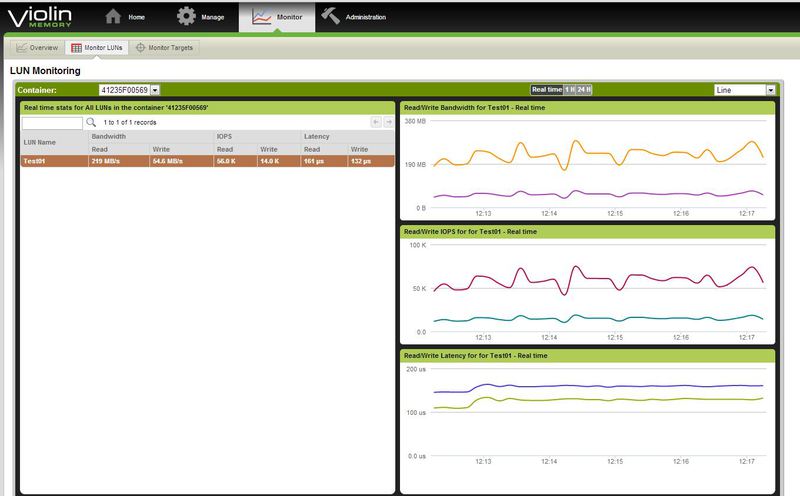

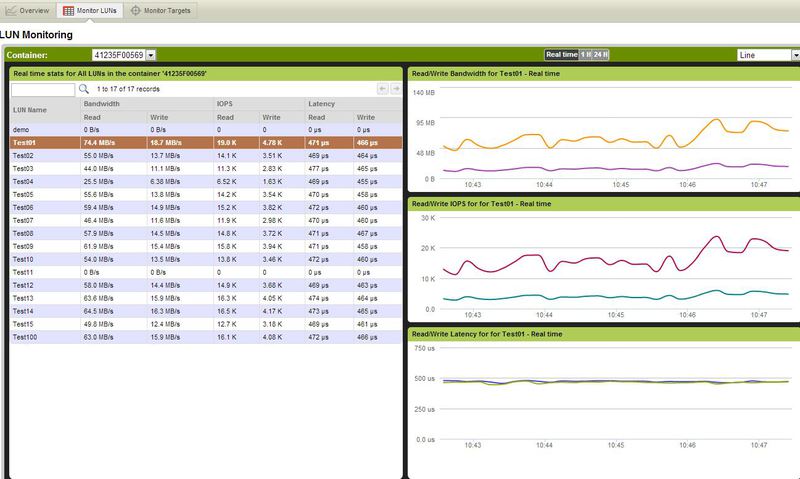

アレイのIOPS統計。これは、1つのIBM 3850X5サーバーが作成できる最大負荷です。

同じ統計ですが、メガバイト/秒です。

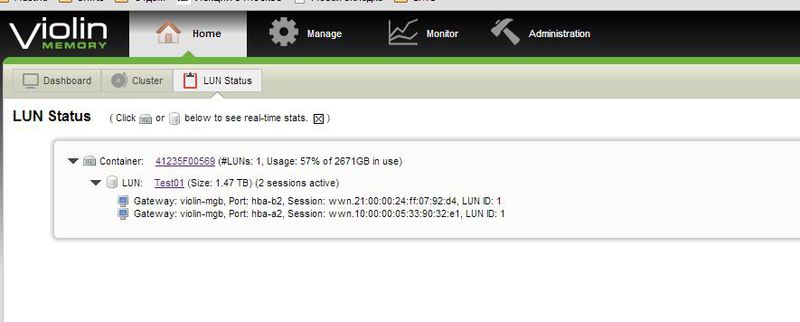

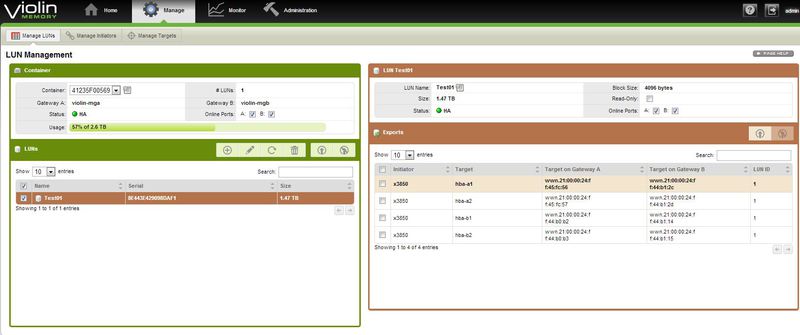

ボリューム設定を表示します。

システムは非常にシンプルで管理しやすいため、バイオリンはインターフェースを非常に重要視しています。利便性と操作性、そしてインターフェース自体の実際の反応速度と可視性です。

単一の月の統計を表示します。

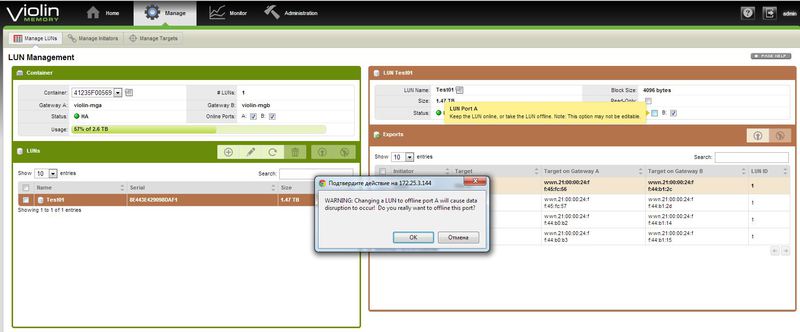

動作中の「愚か者」からの保護。 アクセスの中断またはデータの損失につながる可能性のあるアクションについては、追加の確認が必要です。

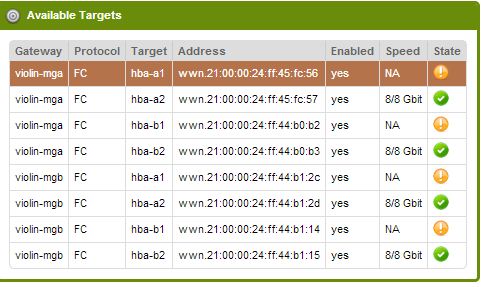

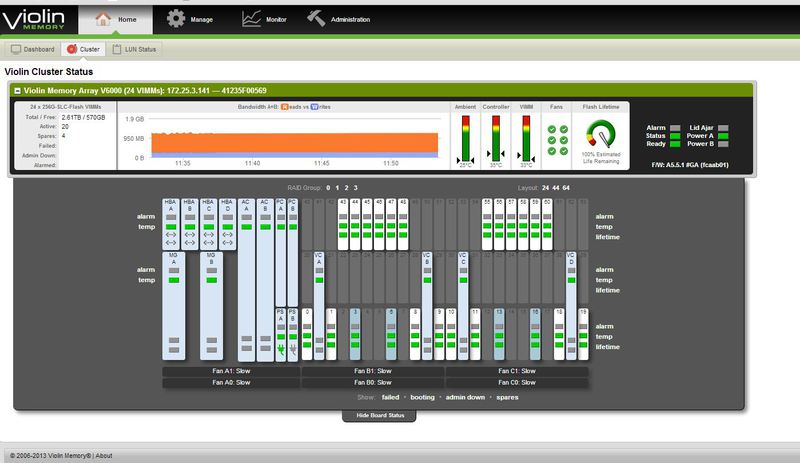

アレイポートの状態。

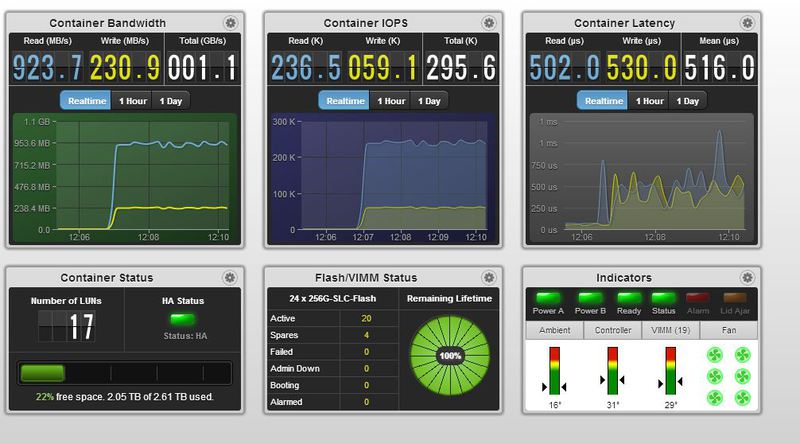

一般的な配列統計のウィンドウ。

ボリュームの統計ウィンドウは個別に。

システムのハードウェアコンポーネントを監視するためのインターフェイス。

ボリューム管理ページ。

ポート負荷監視ページ。

完全にカスタマイズ可能なメインの監視ページでは、アレイの状態に関する管理者にとって最も必要な情報を表示できます。

ロシアのこれらの腺

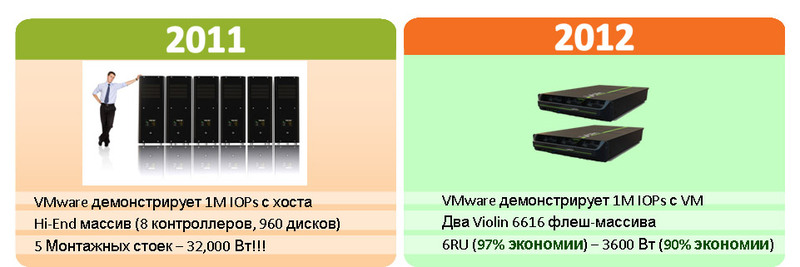

バイオリン自体はどのようにして生まれたのですか? すでに述べたように、それは非常に簡単です。SSDの容量では現代の問題を解決するのにまだ十分ではないことが明らかになり、ディスクのヒープにアプリケーションを広めることはクールなアイデアではなく、東芝とのパートナーシップを結び、低レベルでコントローラーソフトウェアの使用を開始しました、近い、プロセスの物理学に近い。 2005年にシステムの最初のラインを構築し、いかに優れているかを示し、さまざまなIT賞を受賞し、シリコンバレーで「今年のスタートアップ」となり、ストレージシステムの世界をひっくり返しました。 現在、サーバーソリューションおよびソフトウェアの多くの大手メーカーは、Violinソリューションを使用して、ベンチマーク(TPC-C、VMmarkなど)でプラットフォームの可能性を引き出しています。

ヴァイオリンは文字通り「昨日」だけロシアに来て、CROCは独占的な1年間のパートナーシップを受け取りました。 現在、私たちは現在、地元のスペアパーツ倉庫と訓練を受けたサービスエンジニアを提供しています。

実装に関しては 、最終世代の鉄と数個のすでに新しいものの大規模な統合が数十ありました。 たとえば、ある大企業では、数百万の顧客について毎月の請求レポートを72時間生成し、22時間しか生成しなくなりました。 VDIソリューションでは、応答時間が非常に短いため、ストレージシステムからの応答のダウンタイム(待機)を回避することができました。これにより、カーネルをロードできるようになり、コアあたりの古い10ユーザーの代わりに、同様のパフォーマンスでコアあたり25ユーザーが得られ、これによりライセンスとコンピューティングも節約されます機器。

ちなみに、バイオリンマーケティングのおかげです-ありがたいことに、彼らはあまり知名度の高い声明を出さず、ピークパラメーターではなく、標準的なものを示しています-私たちは結局はインテグレーターであり、他の誰かのマーケティングの天才に魅了されたクライアントがなぜ彼がすべてを持っているのか尋ねましたそうではありません。 このアプローチのおかげで、クライアントは予想以上のものを受け取ります。

それでも、多くの人はフラッシュシステムの素晴らしい速度を信じていないので、ヴァイオリンの場合は、鉄で指を突くことができるドライブをテストするだけでなく、計算と試行実装も行います。 たとえば、クライアントがVDIストレージインフラストラクチャを50,000 IOPで50TBのデータに対して50,000ユーザーに展開する必要がある場合、2つのオプションが考慮されました:2つの7 x 200GBキャッシュSSD 180 x 600GB SAS対Violin 6212、12TB RAW = 7Tb 「遅い」データを保存するためのデータと60 x 600GB SAS 18 x 3TB SATA その結果、生産性が5万IOPSから200,000 IOPSに向上する一方で、ほぼ2倍の節約になります。

発生の詳細に興味がある場合は、フラッシュストレージを使用して問題の解決策を計算し、 vbolotnov @ croc.ruに書き込みます。 念のため、そのようなプロジェクトを用意してテーブルに置くことをお勧めします-急に急加速する必要がある場合は、それを取得して計算を表示することができます。