最近、 コンピューターの設計に関する記事がありました。著者は最初にトランジスターからコンピューターを構築したいと考えていましたが、トランジスターでは複雑すぎて高価であると思われたため、7400シリーズのマイクロサーキットを続行することにしました。

最近、 コンピューターの設計に関する記事がありました。著者は最初にトランジスターからコンピューターを構築したいと考えていましたが、トランジスターでは複雑すぎて高価であると思われたため、7400シリーズのマイクロサーキットを続行することにしました。

過去3年間、同様のタスクに興味がありましたが、トランジスタを構築するという最初のアイデアをあきらめていませんでした。今、私の考えを伝え、現在の開発を示すことができます。コンピューター。 しかし、あなたはすぐに先の仕事が数年先であることに気づくはずです:-)

主な質問は、 FPGAとあらゆる種類のRaspberry Piがある場合に 、これらすべてがなぜ必要なのかということです。

答えは簡単です。

1)空き時間にこれを行うことに興味があり、

2)装飾コンピューター(装飾はコンピューターの外観の問題であり、外観ではありません)-それは装飾ペットのようなものです:パグは強盗に足を噛まないでしょうし、ペルシャ猫は戦いでメトロラットを倒しません。 しかし、彼らと遊んでゲストに見せることは興味深いです。たとえコンピューティング、警備、狩りの分野で、彼らが「戦闘」相手よりもはるかに劣っていても。

タスクの置換とアーキテクチャ

装飾コンピューターの要件は何ですか?- 自動アセンブリの開発。 5000の部品をコンピューターにはんだ付けする手-灰色に変えることができます。

- パフォーマンスは重要ではありません。主なことは、1秒あたり10万回の操作があることです(Radio-86RKのレベルで)。 10万op / sでさえ、多くの問題を解決します。

- 実践では、64 KiBのメモリが現実的な最小メモリ量であることを示しています。 1-4 KiBでは、ほとんどが適合しないため、アドレスバスを16ビット未満に削減する価値はありません。

- プログラミングはCで行われます。自由時間をアセンブラーに費やすことはできません(ただし、希望がある場合は、すべてのカードが手元にあります)。

- 基本モデルでは、プロセッサ自体のみがトランジスタで構成されています。 メモリとストラップ-超小型回路からのものです。 将来的に完全なトランジスタバージョンが可能になりますが、これはさらなる開発になります(制限付き-1-2 KiB以上のメモリを搭載することは困難です)

- プロセッサ内-無効化されたLEDは内部レジスターのステータスを表示します(IP、バッテリー、メモリからの書き込み/読み取り...)

- 高すぎない。 ストラッピングと自動インストールを備えた1つのトランジスタのコストはそれぞれ約2ルーブルであり、シリアル製品に1000個を超えるトランジスタを使用することはお勧めできません。 これは、16ビットアドレスバスの要件にもかかわらず、回路がi8080(4500トランジスタ)、i4004(2300トランジスタ)、 MT15 (〜3000トランジスタ)よりも単純であることを意味します。

- uCLinux? 仮想メモリがなくても、24〜32ビットが非常に望ましいでしょう。 もちろん、これにより関心が大幅に高まりますが、少なくともトランジスタ数を2倍にする(=価格を2倍にする)必要があります。 また、ビット深度が増加すると、シリアルコンピューターの速度も比例して低下します。

- 割り込みのハードウェアサポート-必要ありません。 それ自体(マイクロコード、ハードウェアスタックなど)を多く引き付けますが、それなしでも実行できます。

ユーザーインタラクション:従来の実装は、キーボード+テレビまたはVGAモニターへの出力です。 便利な「独自の」キーボードを作成するのは非常に困難です。標準のPS / 2またはUSBを使用する必要があります。 PS / 2キーボードはすでに珍しいものです-トランジスターコンピューターでUSBをサポートすることは、汚れたハック(マイクロコントローラーのような)を使用しないと困難です。

おそらく、最適で最も簡単なソリューションはターミナルインターフェースかもしれません-コンピューターがシリアルポート(RS232)を介して外部と通信する場合、プログラムは同じ方法でダウンロードできます。 つまり 最も単純な場合、トランジスタコンピューターはUSB <> COMアダプターを介してデスクトップコンピューター(または専用のターミナル)に接続され、任意のターミナルプログラム(Puttyなど)で操作できます。

また、GPIOピンを介して外部デバイスを接続する機能も必要です。

シリアルまたはパラレルALU? 8または16ビット?:トランジスタの数は非常に限られている(<1000)ため、パフォーマンスを犠牲にする必要があり、すべての操作は順番に実行する必要があります。 これにより、必要なトランジスタの数が大幅に削減されます。実際、1ビットロジックと16ビットシフトレジスタが必要です。 しかし、1 MHzのクロック周波数では、わずか62,000になります。 もちろん、1秒あたりの操作数を増やすことが望ましいです。

なぜなら いずれにせよ、16ビットのアドレスバスを持ち、8ビットのオペランドをサポートする必要があります。これは、命令システムを大幅に複雑にし、必要なレジスタの数を増やすことを意味します。 したがって、おそらくすべてが単純になります-16ビットアドレスバスと16ビットマシンワード。 8ビットデータで作業する可能性はありません。8ビットのみが必要な場合は、シフトで作業する必要があります。

プロセッサアーキテクチャ:もちろん、本格的なコンピュータはメモリにコードを書き込むことができる必要があります。 したがって、これを外部プロセッサストラッピングにシフトできる場合、ハーバードアーキテクチャ(コードとデータメモリを個別に使用)の実装がより簡単になり、動作がより高速になります。 ただし、プロセッサのストラップがトランジスタの場合、共有コードとデータメモリを使用する必要があります。 したがって、ここでの選択は記事の最後の投票に依存します:-)

プロセッサ自体はハードワイヤード(マイクロコードを操作するためのロジック、およびマイクロコード自体が多くのトランジスタを使用する可能性があります)であり、必然的に非常に単純な命令セット(バイナリロジック+加算、8および1ビットのシフト)、および最小数(6502のように)擬似レジスタとしてRAMを使用する機能を持つレジスタ(1-2)。 おそらく、最も単純なケースでは、すべてのコマンドは単一の厳格なスキームに従って実行されますax = mem [imm] = mem [imm] op ax +条件付き遷移ビット-これにより、プロセッサロジックが最小になり、比較的高速なRAMに最大限の作業が行われます。

ハードウェアスタックおよびハードウェア割り込み処理はありません。これはソフトウェアで実装することもできます。トランジスタよりも多くのメモリがあります。

供給電圧:3.3および5V? ほとんどの古いコンピューターは5Vを使用しており、最新の電子機器は外部接続用に3.3Vに長い間焦点を合わせてきました。 このコンピューターも3.3Vを使用しますが、低インピーダンスのプルアップ抵抗が消費するエネルギーは2.5倍少ないため、抵抗をさらに減らして速度を上げることができます。

トランジスタプロセッサのビルディングブロック

もちろん、1000個未満のトランジスタでプロセッサを作成するには、論理回路を構築する標準的なアプローチを使用しても(シリアルALUを考慮に入れても)動作しません-さまざまな回路の妥協とトリックを適用して、トランジスタの数を減らす必要があります。速度の問題も重要です-Habréの以前の記事とMT15の両方で-論理ブロックが機能するクロック周波数は非常に低いことが判明しました。 シリアルコンピューターの場合、この問題はホットな問題になりつつあります。

シンプルなロジック速度

判明したように、バイポーラトランジスタのロジックを大幅に高速化するいくつかの簡単なトリックがあります。これは、トランジスタが深い飽和状態になるのを防ぐためのショットキーダイオードの追加(出力が非常に遅く、最大200-500ns)、およびオプションで、25-50のコンデンサを追加することです回路の浮遊容量をすばやく再充電するために、ベース抵抗と並列のpF。 そして、もちろん、他の高速デジタル回路と同様に、消費者の近くでセラミックコンデンサで電源を分離する必要があり、場合によっては長いデジタルトラックを終端する必要があります。これらのトリックを適用すると、次の結果が得られます(両方の最適化がスキームの右側にあります)。

そして、波形上で非常に高速に動作します-100ns /除算、エッジ/ 10nsのオーダーの遅延:

また、ベースからグランドへの抵抗の抵抗を選択する-ロジックの伝達特性を制御して、スレッショルド電圧がほぼCMOSのようになり、約3.3 / 2 = 1.65Vになります。 このような変更は、ノイズ耐性に加えて、もう1つの重要な利点をもたらします。入力を緩やかに傾斜させたフロントは、ロジックを通過した後にシャープになります。 また、電気を節約する必要がない場合は、「上部」のトランジスタを捨てて、抵抗と交換することができます。 スキームは次のとおりです。

伝達特性:

3色の線-これは異なる温度(20、40、および60度)でのシミュレーションであり、バイポーラトランジスタのパラメータは温度とともに大きく変動するため、より複雑なスキームではこれを考慮する必要があります。

より複雑なロジック

Tトリガー -クロック信号のTトリガーは、その状態を反対に変更します。 並列命令カウンターを作成するために使用できますが、おそらく使用されません。 すべてが順番に機能します。 動作の原理は、短い負のクロックパルスによる双安定マルチバイブレータです。これは、抵抗R8とR9に並列のコンデンサにより、反対の状態に切り替わります。

回路は、インバータとともに「ハードウェアで」実装されました。 インバーターは予想される速度を示しました(つまり、10〜20 nsの前線)。 はんだ付けの品質に心配しないでください-基板はトランジスタ/パラメータの多くの実験とオプションを通過しました:

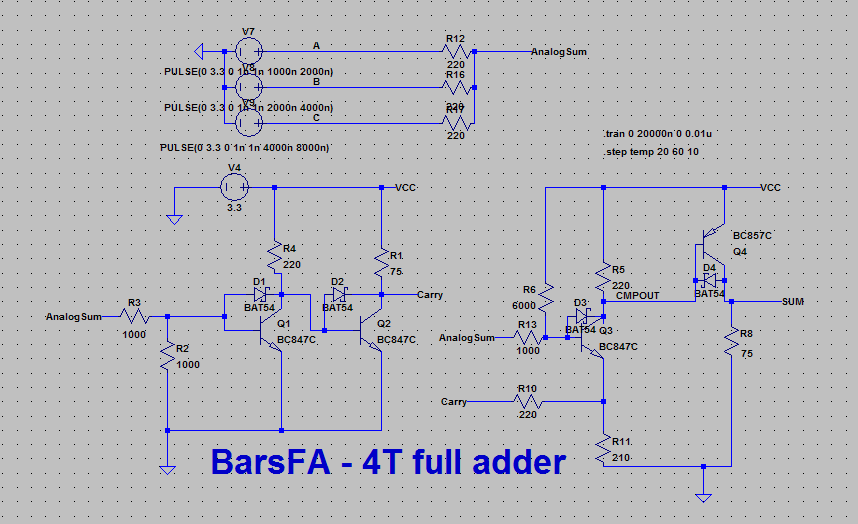

全加算器は、最も重要で複雑なデジタルユニットの1つです。 CMOS全加算器の標準的な実装-28個のトランジスタが必要です。

トランスミッションゲートとさまざまなトリックを使用した最新の実装-トランジスタの選択により厳しい要件を持つ8-11のトランジスタが必要ですが、これらの回路は個別のトランジスタから直接実装することはできません-4ピントランジスタ(まれですが)が必要であり、劣化のため論理レベル1には高い電源電圧が必要です(利用可能なディスクリート電界効果トランジスタのしきい値電圧は、集積トランジスタの0.5Vに対して1.5-2ボルトであるため)。

私が見なければならなかった非常に最小のものは、コンデンサを使用した6つのトランジスタのうちでした(しかし、信頼性は疑問を提起します)。 バイポーラトランジスタの既知の実装には、22個のトランジスタも必要です 。

しかし、たった4つのトランジスタでできるのでしょうか? 私は少し脳を手に入れたが、次のことがわかった。

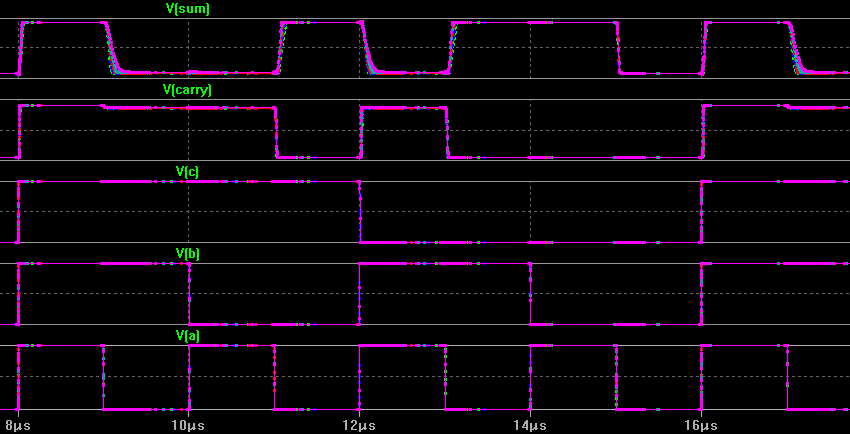

スケジュール:

LTspice IVのシミュレーションスキームはここからダウンロードできます 。

動作原理は次のとおりです。 項の順序は重要ではありません。それらを同様に単純に混合し、デュアルインバータのしきい値電圧を正確に選択することにより、すぐに転送が行われます。 次に、アナログの合計からトランジスタQ3の伝達を減算すると、合計が得られます。 もちろん、これにはすべて、応答レベルの正確な選択と、温度に基づくシミュレーションが必要です。 ショットキーダイオード-トランジスタが深い飽和状態になるのを防ぎ、作業速度を劇的に低下させます。

電界効果トランジスタの使用が可能であり、より優れた温度安定性を提供します。主なことは、それらが十分に低いしきい値電圧を持っていることです。

シフトレジスタは、このトランジスタコンピューターの最も重要な部分です。 同期Dフリップフロップの従来の実装-ビットごとに膨大な量のトランジスタが必要です。

次の機能を使用して、1ビットあたり2つのトランジスタに収まりました。

1)レジスタ-コンデンサに基づいており、「移動」されていない場合は、時間の経過とともにデータが消えます。 しかし、電界効果トランジスタでは、保存時間が非常に長くなります。

2)次のステージへのデータ転送-バイポーラトランジスタによる。 半分の場合、それは反対の非標準モードで動作します-ブレークダウン電圧ははるかに低く(しかし3.3Vを保持する必要があります)、ゲインは直接接続よりもはるかに低くなります(しかし、それで十分だと思います)。

3)次の各ステップ-信号を反転します。これは、シーケンシャルアクセスのみが必要な場合は問題になりません(たとえば、プロセッサレジスタの場合)。 非反転パラレル出力が必要な場合は、8個のインバーターを追加する必要があります(つまり、16ビットシフトレジスタには32個ではなく40個のトランジスタが必要です)。

4)バイポーラトランジスタの飽和には問題が残っています。

スケジュール:

これらのデジタル回路のコンパクトな実装により、1000個のトランジスタ内に収めることは非常に現実的だと思います。

今のところすべてです-途方もなく多くの仕事が私を待っています

そして今-読者へのいくつかの質問:どのオプションがあなたに受け入れられると思われますか?