導入部。 「ナポレオン計画」

ほぼ1年前、コンピューターがどのように機能するか、どのように機能するかを理解するというアイデアがありました。 そしてもちろん、基本的な論理要素(より正確には-トランジスタ)に独自の要素を作成したいという大きな要望がありました。

それから私は彼の仕事について少しだけ考えていました:すべてのデジタル電子機器が論理要素上に構築されていることは知っていました(私にとってはそれは仮定のようでした)が、プログラムがどのように実行され、数字が要約され、なぜ中断されたのか分かりませんでした...このリスト質問を続けることはできますが、今はそうではありません。

開発したコンピューターの特性を定義します。

- ロジックタイプ:バイナリロジック

- データバス解像度:32ビット

- アドレスバス幅:24ビット(16,777,216 32ビット数をアドレス指定できます)

- データの基本的な算術、論理、ビット演算、およびメモリセル(mov、xchg)の演算の実行

- メモリ割り当て機能の実装(4つのアセンブラー命令が提供されます)

- 直接およびポインターを使用したデータ処理

ソフトウェア

論理回路の設計には、多くのプログラムがあります。 しかし、大規模な設計とデバッグの場合、私の要件は2つのプログラムでしか満たされていません(おそらく要件が厳しすぎます)。

実際の要件:

- 直感的なインターフェース

- 大きなスキーマを作成する

- モジュラースキームを作成する機能(スキーム内のスキーム)

- パラメーターを編集する機能を備えたさまざまな基本ロジック要素

- 要素「RAM」および\または「ROM」の存在

- バイナリファイルをRAM \ ROMにロードし、RAMダンプをバイナリファイルに保存する機能

- 情報およびデバッグ回路(ボタン、定数、プローブ、クロックジェネレーター...)の入力/出力用の広範な要素ベースの存在

これ以降のすべての投稿では、論理回路を公開するときに、最近Ubuntuに切り替えたためLogisimを使用しますが、プロジェクト全体はLogic Circuitで行われます。

アクションプラン

理論のない実践は存在しないため、何かを作成するには理論的基礎が必要です。 したがって、今日

- すべてのデジタルエレクトロニクスの重要な要素はトランジスタです。

- 論理要素、そのタイプ。

- 電子回路を構築したり、トランジスタ上に論理素子を構築したりする技術。

- ド・モーガンの法則または門の数を減らす方法。

すべてのデジタルエレクトロニクスの重要な要素はトランジスタです

集積回路の基本要素はトランジスタです。

ウィキペディアの定義については、

トランジスタ-入力信号が電気回路の電流を制御できるようにする半導体材料の無線電子部品。トランジスタは論理要素で構成されています。 トリガー、加算器、論理ブロック、カウンターは論理要素から作成されます。 これらすべてを正しい方法で組み合わせることで、独自のコンピューター(またはEOM)を作成できます。

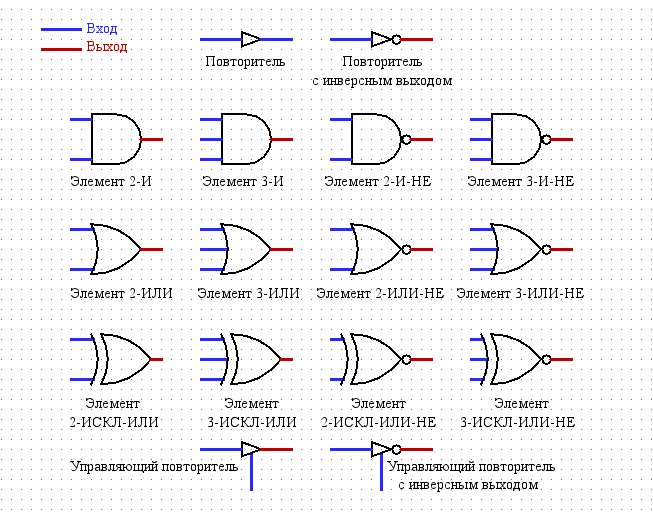

論理要素、そのタイプ

論理要素 -情報をデジタル形式で処理するように設計されたデバイス。

次の論理要素を使用して、任意の複雑な論理関数を設定できます。

- 要素はNOT(インバーター)です。 入力が「0」の場合にのみ、 出力は「1」になります。

- 要素And(接続詞)。 すべての入力が「1」の場合にのみ、出力は「1」になります。

- 要素OR(論理和)。 少なくとも1つの入力が「1」の場合、出力は「1」になります。

- 2を法とする加算要素(排他的OR)。 入力に奇数の 「1」がある場合にのみ、出力は「1」になります。

- リピーター

- リピーターを制御します。 複数の出力を1つの出力に接続するために使用されます。

Logisimのロジック要素:

トランジスタ上に電子回路を構築したり、ロジック要素を構築する技術

最初のアイデアは、 7400シリーズチップではなく、トランジスタ上にコンピューターを構築することでした。 そして、私は電子回路を構築するための技術を探し始めました。 次のものがあります。

- 抵抗-トランジスタロジック(RTL);

- ダイオードトランジスタロジック(DTL);

- エミッター関連ロジック(ESL)。

- 統合されたインジェクションロジック(IIL、I2L、I3L、I2L);

- CMOS(K-MOS、相補型金属酸化物半導体)。

次に、それぞれの長所/短所を読み、その中で抵抗-トランジスタロジックを選択しました。 このロジックは建設的な単純さと低コストであるという事実を考慮すると、選択は明白でした。 また、このロジックには、バイポーラSMDトランジスタとSMD抵抗の幅広い選択肢があります。 トランジスター私はBC847C npnとBC857C pnpを使いました。

すべての欠陥に目を閉じて、1か月間、トランジスタのロジック要素の数を調べました。 彼は、BC547Cトランジスタを使用してブレッドボード上にいくつかのテスト回路を作成しました。 理論的および実用的な部分の結果に満足しました。

レイアウト:

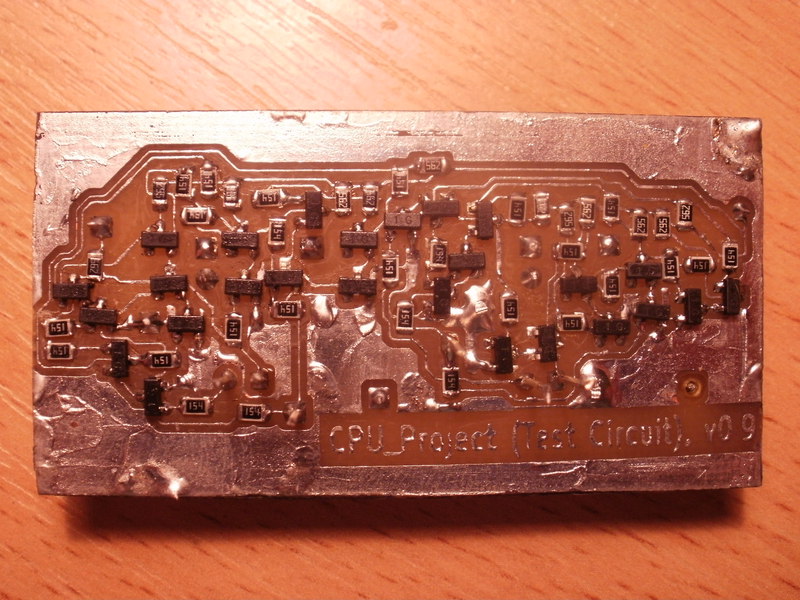

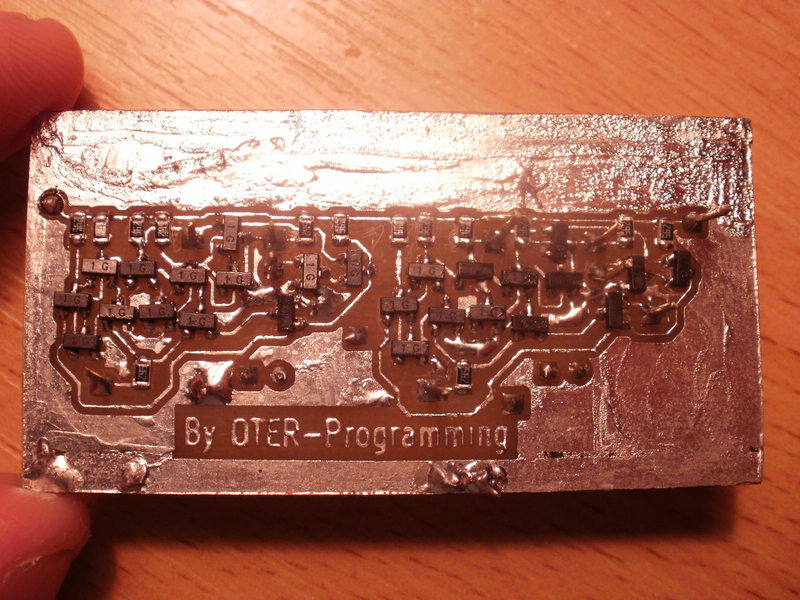

最後の段階-847トランジスタでの同期Tフリップフロップ回路の設計、操作性の確認、周波数特性の分析。 パフォーマンステストは非常に簡単です。論理「1」が入力「T」に供給され、ジェネレータからのクロックパルスが入力「C」に供給されます。 出力では、周波数が入力の半分のクロックパルスを取得する必要があります。 すべてが許容可能な頻度で機能する場合、コンピューター全体が機能します。

4つのTフリップフロップで構成される回路を設計しました。 私はプリント回路基板をフォトレジスト方式にし、簡単にはんだ付けし、最終的にはまさにそのような美しさを得ました(トラック幅-0.15 mm):

5ボルトの電源を回路に接続し、ジェネレーターを入力に、オシロスコープを出力に接続しました。 彼は1 MHzの周波数でテストを開始しましたが、回路は機能しませんでした。 それから彼はそれを20 kHzに下げました-出来上がり、回路は正しく動作しました。 供給電圧を操作すると、動作周波数を40 kHzに上げることができました...

残念ながら、私の期待の構想はうまくいきませんでした。 さらに、1つのTトリガーのみが最大40 kHzの周波数で正常に機能し、他のすべてのTトリガーは、内部RSトリガーが正常に機能していても、高から低に切り替えることができませんでした。

論理素子の構成について、電界効果トランジスタのみでさらに実験を行いました。 結果は満足のいくものでしたが、いくつかの問題が現れました。

- プロジェクトの高コスト(トランジスタのみで約1000ドル);

- 問題は、ウクライナでSMD電界効果トランジスタを入手することです。

- 問題は、RTLで7〜10,000個ではなく、CMOSロジックで15,000〜2万個のトランジスタをはんだ付けすることです。

私自身、私は良い結論を出しました :トランジスターにロジックエレメントを作るよりも、ロジックエレメントを備えた7400シリーズチップを購入する方が良いです。

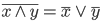

ド・モーガンの法則またはゲートの数を減らす方法

de Morganの法則は、論理否定を使用して論理演算子(論理和と論理積)をバインドする規則です。 正式なロジックでは、次のように記述できます。

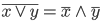

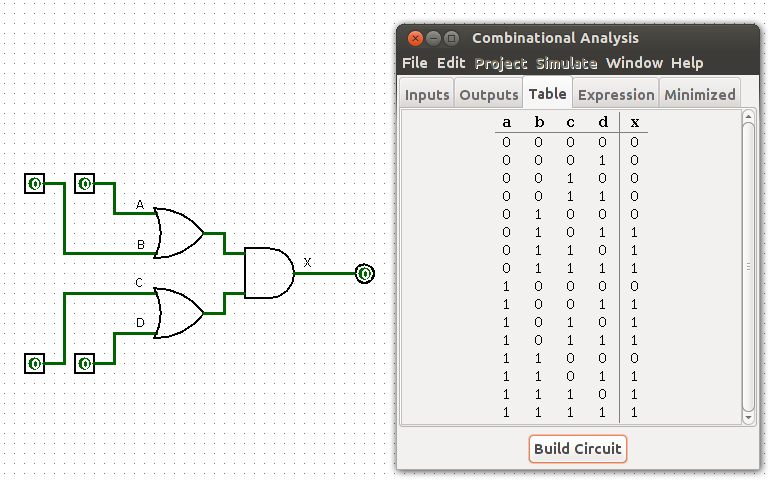

これらのルールを実際に使用する例を考えてみましょう。 このようなスキームがあるとします:

de Morganの法則を使用して、スキームをこれに再作成できます。

真理値表からわかるように、これらのスキームのロジックは同じです。

今、小さな仮定 :反転出力(たとえば、論理2I-NOT)を備えたCMOSロジックの論理要素(論理NOTを除く)には、非反転出力(たとえば、論理2I)を備えた論理要素よりも2つのトランジスタが必要です。

次に、最初の回路には18個のトランジスタが必要で、2番目の回路には12個のトランジスタが必要です。 さらに、2番目の回路は、使用されるバルブが少なく、信号が1桁速く通過するため、より高速に動作します。

今後の計画

次の投稿では、トリガーについて説明し、ALUの設計を開始します。