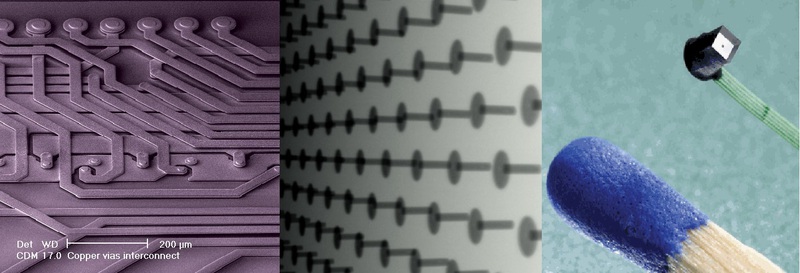

右側のKDPV-TSVを介して光学センサーに接続することにより可能になった小型カメラ(62.5千ピクセル)

前の投稿で 、3次元統合とは何か、この技術が3次元の成長によりシリコンエレクトロニクスの寿命を延ばす方法について話しました。 今回は、この技術について私が知っている問題を説明しようと思います。その理由は、現在および今後数年で、「多層」マイクロプロセッサと新世代のメモリが店舗に登場しないためです。 賞賛するよりも合理的に批判する方が常に簡単です:)。 だから...

手始めに、シリコンウェーハに穴を開けることについて。 リソグラフィに使用されるシリコンウェーハの厚さは、20〜800ミクロンです。 この場合、下層は通常、カテゴリ> 250μmで、残りはカテゴリ<60μmです。 機械的強度など、いくつかの理由があります。 そのため、深刻な問題は、シリコン層に20ミクロンの厚さの多数のきちんとした穴を作り、同時にウェーハ自体を損傷しないようにすることです(すでに3桁小さいトランジスタが含まれているか、含まれます)。 穴を開ける技術はいくつかあり、伝統的に精度と速度の間で選択肢があり、それは価格を意味します。 いくつかの画像を提供します。

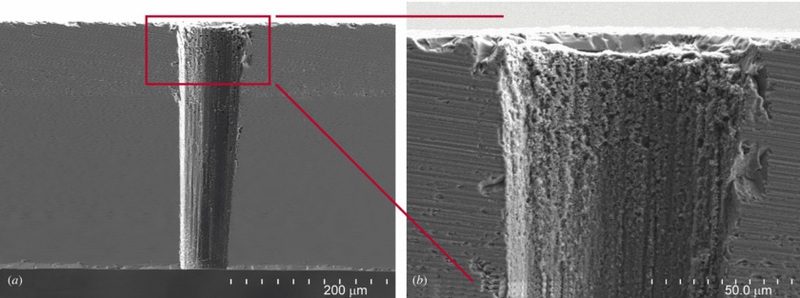

レーザーパルス(40ns、100KHz)穴(9400個/ 19分)

レーザーで切断した穴の化学エッチングの結果(20分/プレート)

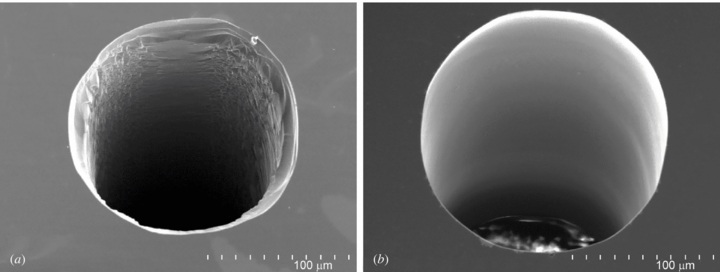

次のステップは、 穴のメッキです。 ここにも多くの問題があります。

まず、TSVとトランジスタの寸法は2〜3桁異なります。したがって、同じ量の金属を同じ方法で穴に移そうとすると、時間がかかります。 むしろ、長く、高価です。

2つ目は、金属を平らな表面に塗布してはならないという事実によりますが、穴の内壁には穴が「成長」する傾向があります。 つまり、金属は入口を完全に閉じ、壁を完全に覆うことなく、導電性の接続を作成しません。 この問題を解決するには、追加の努力が必要です。

操作の正確性とプレートの安全性の両方のカテゴリから、明らかな問題を伴う、金属ピンを穴に「差し込む」などの興味深いアプローチがあります。

次は、TSV(垂直ジョイント)を使用してシリコンウェーハのスタックを組み立てる問題です 。 3D統合は、主に大型デバイスにとって重要です。 単一の欠陥によって拒否されたシリコンウェーハの面積を減らすことにより、コストを大幅に削減できます。 しかし、代わりに、問題は変わりつつあります。1つのプレートを別のプレートに配置する場合、数百および数千のTSVコンタクトを相互に接続する必要があります。 これを初めて行う場合、2回目の試行はありません。 TSVサイズの単位または数十ミクロンの同様の演習は、独自の制限がある精密機械の分野にあります。 そして、エラーの代価は、プレートのスタック全体の結婚です。 それは価格にプラスの影響を与えません。

同時に、開発中のTSV付近では、「除外ゾーン」をトランジスタから解放する必要があります。 そうしないと、リスクが高すぎて、穴を開けたり、プレートのスタックを組み立てたりするプロセスで、この領域のロジックが破損します。 一方では、これは占有面積を増加させ、他方では、設計プロセス中にそのようなことを考慮する必要があります。

そのような製品の機械的強度は別の問題です。 それ自体に貫通穴が存在すると、プレートの強度が低下します。 さらに、負荷分散の理由から、穴を均等に配置することをお勧めします。 また、シリコンウェーハのこのような「サンドイッチ」は、熱膨張特性が不均一になります。 動作温度の違いにより、これによりTSV接続ポイントに大きな力が発生し、スタックが破壊される可能性があります。

しかし、もちろん、主な問題は温度体制を維持することです。 80度以下の温度を確保するためには、さまざまなトリックに行く必要があります。 たとえば、IBMの専門家は、シリコンウェーハと熱伝導率の高いウェーハを交互に使用して、表面に触れるよりも効率的に熱を除去する一種の「貫通ラジエーター」を作成することを提案しています。

理論的には、3D統合を使用して組み合わせることができるプレートの数に制限はありません。 ただし、熱放散の問題がそれほど深刻ではないメモリの場合でも、将来の計画は8層に制限されています。

温度条件は、業界内の他のいくつかの企業が積極的に開発して使用しようとしたにもかかわらず、3D統合テクノロジーがインテルの利益の範囲外であった理由でもあります。 比較的最近まで、モバイルデバイス市場は優先事項ではなく、すべての努力はデスクトップおよびサーバープロセッサの作成を目的としていました。 同時に、主な目標は、エネルギー消費を削減するのではなく、生産性を向上させることでした。 最大のメリットは、同じItaniumのような大きなチップに3D統合を適用することで得られます。 しかし、温度の問題はこれを積極的に妨げます。

いくつかのケースで興味深い問題は、そのようなデバイスのテストとデバッグです。 「個別のプロセッサ、個別のメモリ」としてではなく、各プレートが本格的なデバイスではなく、他のプレートとは別個に動作しない、より興味深いものにプレートに分割することを想像してください。 このような状況では、スタック前に各プレートの動作を確認する方法が問題になりますか? そのようなテストが中止された場合、プレートの接続エラーが原因で最終的なデバイスが機能しない確率は、プレートの1つが機能しない確率を追加します。

まあ、最後に、順番に、そして重要ではありません。 3D統合を使用したデバイスの開発には、設計自動化ツールによる適切なサポートが必要です。 多くの企業が長い間これに夢中になっており、特にシノプシスは少なくとも2009年からこの方向に取り組んでいます。 しかし、これは長いプロセスです。 ここでの努力は、開発者の工数に限定されるものではなく、やるべきことがたくさんあります。

これで終わります。 膨大な数のより具体的な問題は、一般の人々にはほとんど関心がありません。 そして、上記は3D統合が「特効薬」ではなく、その実現に向けて多くの問題があることを理解するのに十分なはずです。

おそらく、3D統合テクノロジーの多くのエキゾチックなアプリケーションに関する別の投稿があるでしょう。