その他のパーツ: パート2 。 パート3

コミュニケーションファクトリーに関するストーリーの継続は、私の制御が及ばない理由により延期されますが、別のトピックをカバーしたいと思います。

10月8日から12日にかけて、マイクロ電子システムとナノ電子システムの開発に関する問題に特化したロシア最大の会議がモスクワ地方で開催されました。 そして、会議自体はかなり否定的な印象を残しましたが、スピーチの1つは群衆から際立っていて、おそらく親愛なる読者にとって興味深いでしょう。 これは、分析レポート「暗闇での生活」「シリコン」です。 Mike Kishinevsky(Intel Corp.のStrategic CAD Labsのプリンシパルエンジニア)が代表する、将来のプラットフォームでの電力と期間の問題」。 会議資料とサードパーティのソースを使用して、このレポートの主なアイデアについてお話します。

「ダーク」シリコンとは

だから、誰もが知っているように、1965年に、Intel Corporationの創立者の1人であるGordon Mooreは、後に「ムーアの法則」と呼ばれる所見を定式化しました。 [1]この観察によれば、シリコン結晶に配置されたトランジスタの数は約2年ごとに2倍になります。 この傾向は、ますます複雑化するプロセスの出現のおかげで、45年以上にわたって続いています。 現在、22nmプロセス技術が積極的に使用されており、14nmは今後1〜2年で登場し、10nmも間近に迫っています。 [2]この傾向が続く場合、2022年までに1チップ内のトランジスタの数は1兆に達し、メタライゼーション層の数(トランジスタ間の接続を形成するために使用される)は14-18個に達します-これは、このような膨大な数のトランジスタを単一システムに効果的に組み合わせるために必要です。 [3]しかし、残念なことに、すべてがそれほど雲一つないというわけではありません。

デナードの法則として知られる依存関係によると、技術プロセスをS倍にスケーリングすると、(理想的な条件下で)計算能力はS 3として増加します。 さらに、このような増加は、追加のエネルギーオーバーヘッドなしで発生します。 これは、同じ領域に、有用な仕事をするトランジスタがS 2に多く配置され、そのようなトランジスタがより高いクロック周波数で動作できるという事実によって説明されます。 この場合、静電容量と動作電圧はS倍減少します。 [4]

実際には、プロセスが減少するにつれて、閉じたトランジスタを流れるリーク電流が増加します。これは、理想的なケースでは変化しないエネルギー消費の増加の主な要因です。 この成長の結果、一部のプロセッサーの2千回目の熱放散は原子炉の腸で観察できるものに近づき、エネルギー消費はハイテク機器ではなく溶接機に関連するようになりました。 [5]

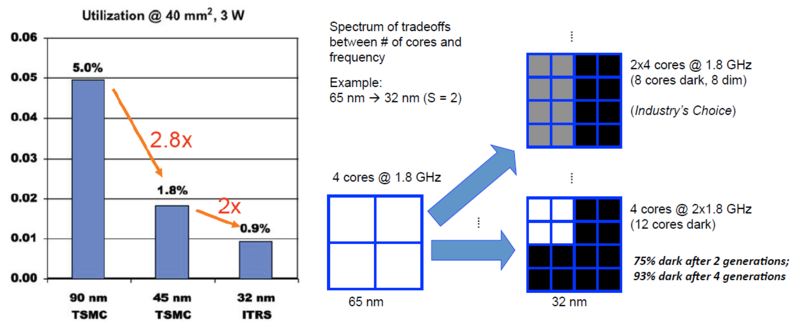

エネルギー消費の特定の制限内に留まる必要があるため、Utilization Wallと呼ばれる制限が出現しました。これにより、新しい技術プロセスごとに、根本的な技術変化がない場合、アクティブな作業に関与する結晶面積の割合(文字通り、トランジスタが切り替わる可能性がある)が指数関数的に減少します。 さらに、この面積は単位またはパーセント単位で測定されます。 [6]現在作業に関与していない水晶の残りの大部分は、「ダーク」シリコンと呼ばれていました。

利用壁

その結果、新しいマイクロプロセッサの開発者は、動作のどの瞬間でも、水晶の大部分が「暗い」または「鈍い」シリコンであることを確認する必要があります。

マイケルテイラーの記事「ダークシリコンは有用ですか? 暗闇のシリコン黙示録の4人の騎手を活用「[7]黙示録の4人のライダーに言及」-「暗黒」シリコンの時代にマイクロエレクトロニクスを繁栄させる4つの基本的なアプローチ。 これらのアプローチ:新しい技術の進歩、エネルギー効率の並列化、専門化、エネルギー管理を使用します。 さらに、システムレベルの最適化が重要な役割を果たします。 これらのアプローチについてはさらに説明します。

「Deus Ex Machina Horseman」またはプロセスの進行。

「MOSFETは根本的な問題です。 「

FinFets、Trigate、High-K、

ナノチューブ、3D、1回限りの改善、

しかし、持続可能なソリューションはありません

プロセス世代。

シリコン黙示録の4人のライダーの中で、これは間違いなく最も予測不可能です。 文学や演劇において、デウス・エクス・マキナは、主人公が完全に運命づけられているように見えるが、状況を救うためにどこからともなく完全に予想外で予測不可能な何かが出てくるプロットを指します。

ダークシリコンの場合、Deus Ex Machinaは半導体技術の科学的なブレークスルーになる可能性があります。 ただし、このようなブレークスルーは非常に基本的なものでなければなりません。 そして、おそらく、近い将来、このようなブレークスルーには、従来のMOSFET技術以外のトランジスタの使用が必要になるでしょう。 その理由は、漏れ電流は基本的な物理的原理によって決定されるためです。 FinFET / Tri-Gateトランジスタの発明やHigh-K誘電体の使用などの技術革新は、大きな成果を示しています。 ただし、それらはスケーラブルな変更ではなく、1回限りの改善である可能性が高くなります。 [8]トライゲートの利点については、 それらについて複数回書かれていました:)

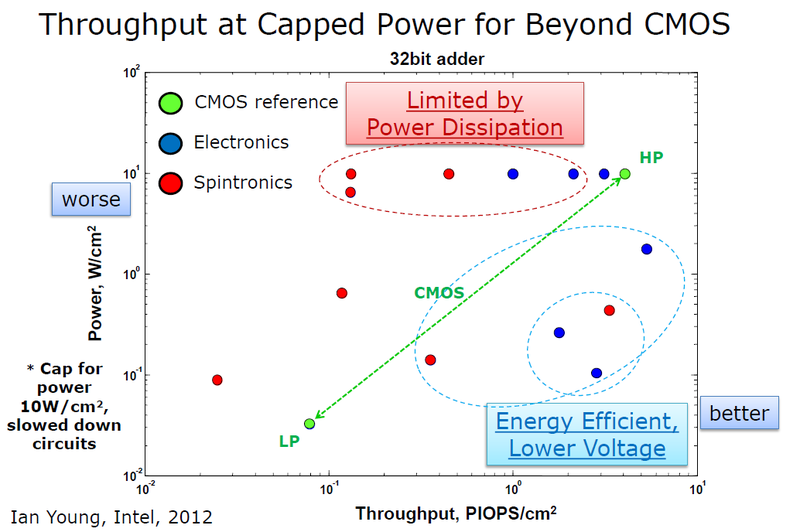

MOSFETに置き換わる技術の開発は長い間続いています。 2つの可能性と(現時点では)最も有望な候補:これらはTFETトランジスターとナノ電気機械スイッチです。 これらの技術の両方が現在使用されているソリューションと比較して桁違いに漏れ電流を減らすことができると信じる理由がありますが、同時に、それらはまだ産業使用から非常に遠いです。

画期的な技術の存在に関する楽観的な見方の1つは、人間の脳のパフォーマンス、エネルギー効率、密度です。 脳は、20ワット未満を消費することで機能する100兆個のシナプスを結合し、高度に並列であると同時にほとんど「暗」な計算の可能性の生きた証拠として機能します。

その結果、技術の進歩は依然として驚異的であり、現在、従来のMOSFET電子機器に代わる多くの興味深い代替品があります。 しかし、これらの選択肢がいつ産業的に使用されるようになるかを予測するために、さらには、新しいものの出現は不可能です。

シュリンクホースマンとエネルギー効率のための並列化

「面積は高価です。 チップ設計者は

持っているのではなく、小さなチップを作るだけ

デザインにダークシリコンを使用!”

(ダークシリコンの研究に取り組んでいる場合、これをよく耳にするでしょう...)

プロセスのスケーリングに伴うリーク電流の増加により、マルチコアマイクロプロセッサは、シングルコアが占有する結晶面積が減少するのと同じ方法でスケーリングできなくなりました。 同時に、「暗い」または「鈍い」シリコンは、エネルギー消費の観点から指数関数的に安価なリソースです。 これにより、エネルギー効率を「獲得」するために水晶の領域を「拡張」できるようにする建築ソリューションに目を向けることになります。 図に示されている例は、1つのコンパレータを2つに置き換えて、並列に動作しているが、周波数が半分の場合に、消費電力を2.5倍削減できることを示しています。 [9]実際には、すべてのノードを理想に近い方法で並列化できるわけではありませんが、エネルギー消費の面でのゲインは依然として顕著です。

トレードオフ領域とエネルギー消費

多くの開発者からのこのアプローチに対する即時の反応は、「水晶の領域は高価なリソースです。なぜ、マイクロプロセッサを使用する代わりに小型化しないのですか」暗い「シリコン」ですか?しかし、これは最も悲観的なシナリオです。 そして、最終的にすべてのチップの面積が縮小する可能性がありますが、この見方は決定的な役割を果たす多くの二次的な要因を見逃しています。

第一に、 「暗い」シリコンは、「空の」、「役に立たない」、または「未使用の」シリコンを意味するものではないことを言う価値があります。 CMOSテクノロジーの最高の時代でさえ、マイクロプロセッサやその他の回路は、一部のタスクにのみ使用されるダークロジックでいっぱいでした。 たとえば、x86 SSE命令実行ブロックは不規則な計算には使用されず、LLC(キャッシュの最後のレベル)を2倍にすると、タスクの範囲が狭い場合にのみゲインが得られます。

また、結晶の面積を縮小することの経済的側面も注目に値します。 より小さな結晶を生産する方がより有益であるという事実には、いくつかの真実があります。 最終的に、マイクロプロセッサの開発者は、フットプリントの手頃な予算に入るために多くの労力を費やします。 小型のプロセッサクリスタルは、線形(またはそれ以上)安価です。 さらに、生産の歩留まりが高くなります。 しかし、指数関数的に小さいプロセッサは、リソグラフィマスクの開発、製造、パッケージングなどのコストのために指数関数的に安くなることはありません。また、これらのコストも何らかの方法で償却する必要があり、シリコンの単位面積あたりのコストが増加します。 これにより、新しいプロセスへの移行の経済的魅力が低下し、ムーアの法則に対する不幸な経済的終結につながります。 競争経済の法律に基づいて、スペース削減が非常にありそうもないシナリオである理由を説明する他の多くの理由もありますが、技術読者にとってあまり興味のない詳細には触れません。

まあ、水晶の面積が減少したときに発生するパッキングと熱の放散に関連する問題に言及することは間違いありません。 面積の指数関数的な減少の重要な結果は、特定の電力消費の指数関数的な増加です。 マルチコアプロセッサチップの熱特性の分析に関する最近の研究[10]では、ホットスポット(ホットスポット)のピーク温度をTmax = TDP *(Rconv + k / A)としてモデル化できることが示されています。 ここで、TDPはプロセッサの冷却システムが設計される熱出力を示す値であり、Rconvはヒートシンクの特性(少ない方が良い)、kはマイクロプロセッサの特性の集合的特性、Aは占有面積です。 面積が指数関数的に減少すると、2番目の項が支配的になり、温度が指数関数的に増加します。 プロセッサを過熱から保護する必要があるため、パフォーマンスの一部を犠牲にする必要があります。

さらに、面積の縮小は、多くの実際的なエンジニアリングの問題も示します。 たとえば、ダイスタッキングなどの技術を使用したシリコンウェーハの垂直ボンディングには、シリコンのパッドとスロット(TSV)が必要ですが、そのサイズを簡単に縮小することはできません。 さらに、I / O接続領域もムーアの法則の速度でスケーリングしません。

写真の3D統合とTSV :)

その結果、マイクロプロセッサの領域はさらに減少し、おそらく減少しません(減少した場合、非常に遅くなります)。 しかし、プロセステクノロジーの新世代ごとにもたらされる追加のトランジスタを使用して生産性を高める(各世代で約1.4倍)場合は、今ではエネルギー消費を削減するために使用されます(各世代で約40%)

継続する 。

ソース

- ゴードン・ムーア(1965)。 「より多くのコンポーネントを集積回路に詰め込む」

- マークボーア、インテル、2011年

- Shekhar Borkar、Intel、2010年

- マークボーア(2007)「デナードのMOSFETスケーリングペーパーに関する30年の回顧展」

- Fred Pollack(1999)「次世代のCMOSプロセス技術における新しいマイクロアーキテクチャの課題」、Microの基調講演

- Ganesh Venkatesh et al、(2010)「保全コア:成熟した計算のエネルギーの削減」、ASPLOS 2010

- マイケル・テイラー、(2012)ダークシリコンは有用ですか? 登場するダークシリコンアポカリプスの4人の騎手を活用」、DAC 2012

- イアン・ヤング、インテル、2012

- Anantha Chandrakasan et al、(1992)「低電力CMOSデジタル設計」

- W. Huang et al、(2008)「熱の観点から見た多くのコア設計。」DAC 2008。