少し前まで、チップ8エミュレーターの作成に関する記事がHabréに掲載されました。これにより、エミュレーターの作成方法を少なくとも表面的に理解することができました。 エミュレーターを実装した後、さらに進んでいくように思われました。 選択は元のゲームボーイにかかった。 結局のところ、この選択は、より深刻なものを実装したい状況に理想的であり、エミュレーターの開発経験はほとんどありません。

エミュレーションに関しては、ゲームボーイは比較的単純ですが、それでもかなりの量の情報を調べる必要があります。 このため、Gameboyエミュレーターの開発に関する記事がいくつかあります。 最終結果は、他のエミュレーターにはないことが多いサウンドを含む、オリジナルのほぼすべての機能をサポートする、互換性の良いエミュレーターになります。 おまけとして、エミュレータはほとんどすべてのテストROMに合格しますが、それについては後で詳しく説明します。

これらの記事には、エミュレーター実装の完全な説明は含まれません。 これは大きすぎて、実装からの関心はすべて消えます。 まれな場合にのみ特定のコードに到達します。 実装の小さなヒントを使用して、より理論的な説明を行うというタスクを自分で設定します。理想的には、エミュレータを簡単に作成でき、同時に自分で作成したような気分になります。 必要に応じて、独自の実装を参照します-必要に応じて、大量のコード行を破ることなく適切なコードを見つけることができます。

この記事では、Gameboyを理解し、そのプロセッサとメモリをエミュレートすることから始めます。

ゲームボーイエミュレータの作成、パート1

ゲームボーイエミュレータの作成、パート2

ゲームボーイエミュレータの作成、パート3

目次

はじめに建築

CPU

中断

記憶

おわりに

はじめに

Gameboyは、1989年に発売された任天堂のハンドヘルドコンソールです。 それは元の白黒のゲームボーイについてです。 ガイドされるさまざまなドキュメントでは、ゲームボーイというコード名が使用されていることに注意してください-DMG(Dot Matrix Game)。 さらに使用します。

開始する前に、DMGの技術的特性を理解する必要があります。

| CPU | 4.19 MHzの周波数で動作する8ビットSharp LR35902 |

| RAM | 8 kB |

| ビデオメモリ | 8 kB |

| 画面解像度 | 160x144 |

| 垂直周波数 | 59.73 Hz |

| 音 | 4チャンネル、ステレオサウンド |

件名を確認したら、次のステップはドキュメントです。 必要な情報が大量にあるため、記事のすべてを完全に掲載することはできないため、事前にドキュメントを準備する必要があります。

Gameboy CPU ManualというDMGの素晴らしいドキュメントがあります。 著名な開発者からのいくつかの有名なドキュメントが含まれており、必要なほぼすべての情報が含まれています。 当然、これですべてではありませんが、この段階ではこれで十分です。

正式なものであっても、文書に誤りがあることをすぐに警告します。 この一連の記事の中で、私が見つけることができるさまざまな文書のすべての欠点に言及しようとします(覚えておいてください)。 また、多くのギャップを埋めようとします。 結論としては、DMGの包括的な説明はありません。 利用可能な資料は、多くのコンソールノードの作業についての表面的なアイデアのみを提供します。 プログラマーがそのような「落とし穴」を認識していない場合、エミュレーターの開発は思ったよりもはるかに複雑になります。 DMGは、信頼できる詳細な情報を手元に置いておくと簡単です。 そして問題は、多くの重要な詳細が他のエミュレーターのソースコードからしか学べないということです。しかし、それは私たちの仕事を容易にしません。 よく知られているエミュレーターのコードは、複雑すぎる(Gambatte)か、ひどく山ほどの低品質のコードです(Visual Boy Advance-涙なしにコードを見ることはできません)。

記事は私のエミュレーターに目を向けて書かれたものなので、Cookie ソースとCookie Cookieへのリンクをすぐに示します。

建築

将来のエミュレータのアーキテクチャから始めましょう。 DMGをエミュレートするには、互いにほぼ独立した多くのモジュールを実装する必要があります。 そのような状況では、すべてを1つのヒープに入れるのは愚かなことです(他のエミュレータでよく見られます。こんにちはVBA)。 よりエレガントなソリューションは、DMGの個々の部分を、鉄の部分をエミュレートする個別のクラスとして実装することです。これには理由があります-エミュレータの開発を始めたのは、すべてのコンポーネントが1つのスーパークラスになっているためです。 誰もがやるべきことだけをすれば、物事はずっと楽になることがすぐに明らかになりました。 このアプローチには明らかな複雑さがあることを認識する価値はありますが。 クラスの責任を正しく区別するには、DMGの内部構造を十分に理解する必要があります。

それでは始めましょう。

CPU

DMGには、4194304 Hzの周波数で動作する8ビットSharp LR35902プロセッサが含まれています(このような精度に驚かないでください。今後この番号が必要になります)。 Zilog Z80プロセッサの簡易バージョンと見なすことができます。これは、Intel 8080に基づいています。Z80と比較すると、一部のレジスタと命令セットが欠落しています。プロセッサには、8つの8ビットレジスタA、B、C、D、E、F、H、L、および2つの16ビット専用レジスタ(PCおよびSP)が含まれています。 一部の命令では、8ビットレジスタを組み合わせて16ビットレジスタとして使用できます。つまり、AF、BC、DE、HLです。 たとえば、BCレジスタは「接着」レジスタBおよびCであり、Cレジスタは下位バイトとして機能し、Bは上位バイトとして機能します。

レジスタA、B、C、D、E、H、Lは汎用レジスタです。 レジスタAもバッテリーです。 レジスタFにはプロセッサフラグが含まれており、直接アクセスできません。 以下はレジスタの概要です。 ビット0〜3は使用されません。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 旗 | Z | N | H | C | 0 | 0 | 0 | 0 |

フラグの目的:

- ゼロフラグ(Z)-最後の数学演算の結果がゼロまたは2つのオペランドが比較時に等しいことが判明した場合、フラグが設定されます(ビットは1)。

- 減算フラグ(N)-最後の操作が減算であった場合、フラグが設定されます。

- ハーフキャリーフラグ(H)-最後の数学的操作の結果として、下位ハーフバイトからの転送が発生した場合、フラグが設定されます。

- キャリーフラグ(C)-最後の数学的操作の結果として転送が発生した場合、フラグが設定されます。

ご想像のとおり、レジスタPC(プログラムカウンター)は命令カウンターであり、次の命令のアドレスが含まれています。

SPレジスタ(スタックポインター)は、それぞれ、スタックの最上部へのポインターです。 知識のない人にとっては、スタックは変数の値、戻りアドレスなどが書き込まれるメモリ領域です。 SPには、スタックの最上位のアドレスが含まれます-スタックは、高から低に成長します。 彼にとっては、常に少なくとも2つの操作があります。 PUSHを使用すると、特定の値を挿入できます。まず、SPレジスタが削減され、次に新しい値が挿入されます。 POPを使用すると、値を取得できます。まず、アドレスSPで値がメモリから取得され、次にSPが増加します。

プロセッサには、いわゆるIME(割り込みマスターイネーブル)も含まれています。これは、割り込み処理を許可するフラグです。 それぞれ、無効(0)と有効(1)の2つの値を取ります。

理論により、すべての実装を開始できます。 8ビットのレジスタと16ビットのペアの両方を使用する必要があるため、ビット操作を使用せずにこれらとレジスタの両方に同時にアクセスできるメカニズムを実装することをお勧めします。 これを行うには、次のタイプを宣言します。

union WordRegister { struct { BYTE L; BYTE H; } bytes; WORD word; };

プロセッサレジスタをペアとして保存し、WordRegisterアソシエーションのおかげで個々のパーツにアクセスできます。 ワードフィールドは、16ビットレジスタ全体へのアクセスを提供します。 「バイト」フィールドは、ペアの個々のレジスタへのアクセスを提供します。 唯一のことは、レジスタAとFを別々に保存することです。 レジスタAはバッテリーであるため、頻繁に使用されます。 レジスタFでの同様の状況-プロセッサフラグは、かなり頻繁に設定する必要があります。

プロセッサ自体の実装を開始しましょう-Cookieboy :: CPUクラスがこれを担当します。 命令の読み取りと実行は、通常の方法で実装されます-メモリからオペコードを読み取り、スイッチ構成を使用してデコードおよび実行します:

BYTE opcode = MMC.Read(PC); PC++; switch (opcode) { case 0x00: break; }

すべてのオペコードの長さは1バイトですが、一部の命令はいわゆるプレフィックスを使用します-最初のバイトは命令セットのプレフィックスです(私たちにとって唯一のプレフィックスは0xCBです)、2番目のバイトはこのセットのオペコードです。 実装は基本的です。0xCBに出会ったらすぐに、別のバイトを読み取り、ネストされたスイッチでデコードします。

このコードは、1つの呼び出しで1つのプロセッサ命令を実行し、他の必要な操作を実行するvoid Step()関数に配置されます。

当然、メモリの読み取りと書き込みには、別のクラス-Cookieboy :: Memoryが必要です。このオブジェクトは、上記の "MMC"という名前で見ることができます。 この段階では、基本的なメソッドを持つスタブで十分です。

class Memory { public: void Write(WORD addr, BYTE value); BYTE Read(WORD addr); };

DMGプロセッサにはかなり多数の命令があり、そのリストはGameboy CPUマニュアルに記載されています。 また、どのプロセッサフラグを設定する必要があるか、各命令に必要なクロックサイクル数も示します。 フラグの説明を注意深く読んでください-フラグの設定が正しく実装されていないと、しばしばゲームが動作しなくなり、デバッグが拷問に変わります。 しかし、私は少し安心します-プロセッサフラグ用のテストROMがありますが、ROMの実行にはまだ程遠いです。

対策といえば。 チップ8が十分に単純であり、そのエミュレーションが命令実行の長さを考慮する必要がなかった場合、DMGでは状況が異なります。 コンソールのコンポーネントは何とか機能しませんが、クロックジェネレーターを使用して同期されます。 私たちにとって、これは、エミュレータのすべてのコンポーネントの動作をプロセッサと同期する必要があることを意味します。

この問題を解決するのは非常に簡単です。 プロセッサは、エミュレータの中心的なリンクです。 指示に従って、すべてのコンポーネントを相互に同期させるためにプロセッサがサイクルで費やした時間を他のコンポーネントに転送します。 これを行うには、SYNC_WITH_CPUマクロ(clockDelta)を使用します。このマクロは、命令の実行にプロセッサーが費やした時間を転送します。 エミュレータの残りのコンポーネントの同期機能をすでに呼び出しています。 同期の問題の解決策は、プロセッサのクラスではなくても、プロセッサのクラスを超えて簡単に移動できます。

コンソールのコンポーネントは同時に動作し、プロセッサが命令の実行を完了するまで誰も待ちません。 一部の命令は実行に時間がかかり、その過程でデータがメモリに読み書きされます。 プロセッサは、ご想像のとおり、メモリの読み取り/書き込みに一定の時間を費やします(4クロックサイクル)。 これは、実行中にメモリの内容が変更される可能性があるという事実につながります。もちろん、これもエミュレートすることをお勧めします。

この場合、実行プロセスで同期マクロを数回使用する必要があります。これにより、読み取りまたは書き込み時に正しいデータがメモリ内にありました。 ほとんどの命令は、このような正確な同期を必要とせず、実行後に実行できるようにします。 その他には、同期機能とメモリの読み取り/書き込み操作の正確なシーケンスが必要です。

それにもかかわらず、異なる方法で行う方がより正確で美しいです。 1バイトのメモリからの各書き込みまたは読み取り操作には4クロックサイクルかかることが確実にわかっています。 補助的な読み取りおよび書き込み関数を追加するだけで十分であり、それら自体が同期関数を呼び出します。 これが実行されるとすぐに、実際の実行時間は読み取りおよび書き込み操作で構成されるため、ほとんどの命令はすぐに正しい期間を見つけます。 コマンドのオペコードの取得もここに適用されます。 これはまさにエミュレーターで行ったことで、手動の同期とタイミングからほぼ完全に解放されました。 私の介入が必要な指示はわずかでした。

次に、バーを使用して状況を明確にするために少し脱線しましょう。 さまざまなドキュメントに混乱があります。 たとえば、NOPの期間が4小節、その他の小節-1小節など、数字を記述するドキュメントもあります(たとえば、任天堂の公式ドキュメントに記載されています)。 理由を理解するには、理論に少し注意をそらす価値があります。

プロセッサ命令には、マシンサイクルと呼ばれる特定の期間があります。 1マシンサイクルで、プロセッサはオペコードの読み取り、デコード、コマンドの実行など、1つのアクションを実行できます。 メモリ内の値の読み取りまたは書き込み。 プロセッサは1つのマシンサイクルで複数の操作を実行できるため、マシンサイクルはマシンサイクルで構成されます。 そして、私たちはプロセッサに来ます。 NOPが4サイクル続くと言えば、マシンサイクルのことです。 NOPの1クロックサイクルについて話している場合、マシンサイクルについて話していることになります。 これはまさにDMGプロセッサーの仕組みです-そのマシンサイクルは4マシンサイクル続き、多くの命令には正確に4サイクルまたは1マシンサイクルがあります-DMGプロセッサーはメモリからオペコードを読み取り、デコードし、わずか4マシンサイクルで命令を実行できます。

以下では、より馴染みのあるマシンクロックを使用します。 これらは、クロックジェネレーターの1周期に対応します。つまり、これらはエミュレータにとって最小で分割できない時間単位です。 したがって、NOP操作は4メジャー続きます。

この段階では、すべてのプロセッサ命令を完全にエミュレートすることがすでに可能です。 それとは別に、それらのいくつかに言及する価値があります:

- HALTには、CPUマニュアル(2.7.3。低電力モード)で説明されている、かなり興味深い動作があります。 額を決定すると、HALT命令テストが失敗します。 ここでは、命令自体の実装と割り込みハンドラーの実装の両方に注意する必要があります(これについては後で説明します)。 命令の実装は、IMEがゼロで、現時点で処理する必要のある割り込みがない場合にのみ、実行を一時停止せずに言及されたバグにつながるようなものです(これについては後で説明します)-これはほとんどのドキュメントで省略されている最後のポイントです。 それ以外の場合、バグはなく、実行は中断されます。 当然、クロックジェネレーターと他のすべてのコンポーネントは作業を継続します。つまり、同期関数を呼び出し続け、4つのメジャーを引数として与える必要があります(このモードで1クロックサイクルをカウントすることは意味がありません)。 プロセッサがNOPを実行しているようです。

- POP AFでは、Fレジスタに未使用のビットがあるという事実を考慮する価値があります。 これを行うには、レジスタFの内容がスタックから削除された後、レジスタFの下位4ビットをリセットする必要があります。

- 命令RLCA、RLA、RRCA、RRAは、レジスタFのフラグZを常にリセットします。

これらの欠点に加えて、他にもあります。 CPUマニュアルには、命令の期間に関する不完全な説明が含まれています。 ご想像のとおり、条件分岐命令は、分岐が発生したかどうかに応じて異なる期間を持つ必要があります。 テストROMを使用することもできますが、これらの命令のために単独では正常に動作しないため、テストを開始しなくても不明なエラーが表示されます。 これらの指示の期間を示す表は次のとおりです。

| オペコード | 移行は発生しませんでした | 移行が発生しました |

| 0xC2、0xCA、0xD2、0xDA | 12 | 16 |

| 0x20,0x28,0x30,0x38 | 8 | 12 |

| 0xC4、0xCC、0xD4、0xDC | 12 | 24 |

| 0xC0,0xC8,0xD0,0xD8 | 8 | 20 |

また、命令RST n(オペコード0xC7、0xCF、0xD7、0xDF、0xE7、0xEF、0xF7、0xFF)の長さが間違っています。 正しい値は16メジャーです。

そのため、現時点では、「プロセッサ」はメモリから命令を読み取り、実行し、他のコンポーネントをそれ自体と同期できます(同期中、これらはすべてダミー関数です)。 その後、すべての作業が完了した後に中断があったかどうかを確認する必要があります。

中断

割り込みは、現在のプロセッサ命令の実行を一時停止し、制御を割り込みハンドラに転送するイベントです。 DMGはこの原則に基づいて機能します。同期中に、エミュレータの他のコンポーネントの同期メソッドを呼び出して、割り込みを要求する場合があります。 DMGでは、これは次のように行われます。 IF(割り込みフラグ)とIE(割り込みイネーブル)の2つのレジスタがあります(それらの場所については後で説明します)。 これらのビットには特定の目的があり、両方のレジスタで同じです。

| ビット | 中断 |

| 4 | ジョイパッド |

| 3 | シリアルI / O転送完了 |

| 2 | タイマーオーバーフロー |

| 1 | LCDC |

| 0 | Vブランク |

IFレジスタビットは、どの割り込みが要求されたかを示します。 ビットが設定されている場合、割り込みが要求されます。

IEレジスタビットは、割り込み処理を有効にします。 ビットが1に設定され、対応する割り込みが要求された場合、処理されます。 そうでない場合、割り込みは処理されません。

ご覧のとおり、ビットの同一の割り当ては非常に便利であり、論理演算ANDを使用して、どの割り込みを処理する必要があるかを見つけることができます。

重要な詳細の1つは、割り込みにより、HALTまたはSTOPの実行の結果として発生したシャットダウン状態からプロセッサが復帰することです。 そして、ここで割り込みレジスタがチェックされるアルゴリズムは非常に重要です。 アルゴリズムは次のとおりです。

- 処理する価値のある割り込みがあるかどうかを確認します。 これは、IEレジスタとIFレジスタ間の論理AND演算を使用して行われます。 また、最上位の3ビットは両方のレジスタで使用されないため、結果と数値0x1Fで論理AND演算を実行して、発生する可能性のあるゴミを削除する価値があります。

- そのような中断がなければ、関数を終了します。 もしそうなら、今すぐにプロセッサをシャットダウン状態から復帰させなければなりません。

- 現在、割り込みの処理を開始しています。 これを行うために、IMEフラグが処理を禁止しているかどうかを確認します。 そうでない場合:

- ゼロIME;

- PCレジスタをスタックにロードします。

- PCレジスタをメモリ内のハンドラーのアドレスに設定して、割り込みハンドラーを呼び出します。

- IFレジスタビットを処理済みの割り込みに設定します。

割り込みは一度に1つずつ、厳密に定義された順序で処理されます。 ハンドラーの優先順位とアドレスに関するすべての情報は、CPUマニュアルに示されています。

重要な詳細。 繰り返しになりますが、誰かが考えたかもしれません:割り込みの処理はプロシージャの呼び出しと非常に似ているため、時間がかかるはずです。 これは事実であり、20の対策が必要です。 何らかの理由で、DMGを説明するドキュメントではこの点は省略されています。

次に、実装を開始します。 cookieboy :: Interruptsクラスが対処します。 IEおよびIFレジスタを配置し、これらのレジスタにアクセスする関数を宣言します(後で必要になります)。また、特定の割り込みを要求できる関数(何らかの割り込みを要求するたびにビットを操作する必要はありません) 。 また、処理する価値のある割り込みをチェックする関数も必要です。 この関数の呼び出しをプロセッサのステップ関数の最後に配置し、さらにコンポーネントを同期します。

割り込み要求について少し。 これは、IFレジスタの対応するビットを設定することにより行われます。 インストール前に、IEケースの検証は必要ありません。 その中のビットが特定の割り込みを禁止している場合でも、この割り込みのためにIFレジスタのビットを設定します。

Cookieboy :: Interruptsの実装のソースコードを見ると、使用されていないすべてのビットを1に設定した後(値0xE0とのOR演算)、IEおよびIFレジスタの値を返していることに気付くかもしれません。 私には理由があります。 I / Oポートの多くのレジスタ(以下で詳しく説明します)はすべてのビットを使用するわけではありませんが、他のレジスタは一部のビットまたはレジスタ全体への読み取りアクセスを一度に制限します。 これも考慮に入れる必要があります。このため、未使用で読み取り禁止のビットを返す前に1に設定する必要があります。

まとめると。 エミュレータはプロセッサ命令を実行し、エミュレータのすべてのコンポーネントを相互に同期させ、割り込みを処理します。 確かに、これまでのところはすべて言葉だけです。 本当に機能するエミュレーターを取得するには、DMGメモリをエミュレートする必要があります。

記憶

事前に1つの用語-メモリバンクを定義します。 これにより、厳密に定義されたサイズのメモリ領域を意味します。 バンクには2つのタイプがあります-長さが0x4000バイトのROMバンクと長さが0x2000のRAMバンク(16進数システムに慣れれば、私にとってもあなたにとっても簡単になります)。 なぜこれが必要なのですか? DMGプロセッサは16ビットアドレスを処理できます。つまり、アドレススペースは0x10000バイトに制限されています。 これらのうち、ゲームのイメージ用に予約されているのは0x8000バイトのみです。 ほとんどの場合、これでは十分ではなく、メモリバンクが機能します。メモリバンクなしでアドレス0x4000-0x7FFFに目を向けると、ゲームのイメージでこのアドレスに到達します。 メモリバンクを使用して、画像をバンクに分割するように設定でき、アドレス0x4000-0x7FFFで選択したバンクが表示されます。 したがって、この領域のある時点では2番目の銀行、別の時点では10番目です。 私たちが望むように、一般的に。 したがって、仮想アドレスと物理アドレスに到達します。 0x4000-0x7FFFは、物理アドレスと一致する必要のない仮想アドレスです。 物理アドレスは、メモリセルがアクセスされる実際のアドレスです。

これはすべて、DMGが0x8000バイトだけでなく、アドレス空間全体をはるかに超えるゲームイメージで動作できるようにするために必要です。 言葉で言えば、これはすべて複雑すぎるように思えるかもしれませんが、実装中に、これらは説明するよりも実装が簡単で高速な非常に基本的なものであることは明らかです。

RAMにも同じことが当てはまります。 バンクを使用すると、カートリッジにマイクロサーキットを配置することにより、ボリュームを拡張できます。 さらに、この方法で、カートリッジに内蔵されたバッテリーを使用してRAMに電力を供給する本格的なストレージシステムを実装できます。

仮想アドレスを物理アドレスに変換するタスクは、カートリッジ内にあるMBCコントローラーにあります。 ROM領域でのすべての読み取りおよび書き込み操作は、それを通過します。 外部RAMに関連付けられた操作もここにリダイレクトされます。

当然、ROMの内容を変更することはできません。 書き込み操作は、MBCの制御コマンドとして使用されます。 CPUマニュアルでは、どのアドレスがどの機能を担当しているのかを読むことができます。 したがって、特定のアドレスに番号9を書き込んだので、バンク9を選択したいと言います。その後、0x4000-0x7FFFに連絡してその内容を読み取ることができます。

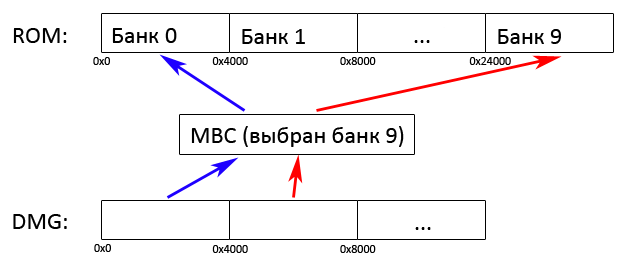

次の図は、最も単純なMBC操作スキームを示しています。 ここでは、一部の実際のコントローラーと同様に、領域0x0000-0x3FFFは常にバンク0にリダイレクトされますが、領域0x4000-0x7FFFは現在のバンクにリダイレクトされます。

DMGアドレス空間スキームを検討してください。

| 記憶部 | 開始アドレス | 終了住所 |

| ROMバンク0 | 0x0000 | 0x3FFF |

| 切り替え可能なROMバンク | 0x4000 | 0x7FFF |

| ビデオラム | 0x8000 | 0x9FFF |

| 切り替え可能なラムバンク | 0xA000 | 0xBFFF |

| 内蔵RAM 1 | 0xC000 | 0xDFFF |

| 内蔵RAM 1のエコー | 0xE000 | 0xFDFF |

| オーム | 0xFE00 | 0xFE9F |

| 未使用 | 0xFEA0 | 0xFEFF |

| I / Oポート | 0xFF00 | 0xFF4B |

| 未使用 | 0xFF4C | 0xFF7F |

| 内蔵RAM 2 | 0xFF80 | 0xFFFE |

| 割り込み許可レジスタ | 0xFFFF | 0xFFFF |

各セクションの詳細:

- ROMバンク0。切り替え可能なROMバンク。 これらの領域はすでに検討済みです。

- ビデオRAM。 グラフィックスを実装するときは、詳細を検討します。

- 内部RAM 1. DMG内のRAM。

- 内部RAM 1のエコー。これは、内部RAM 1の内容を複製します。

- OAM これは、スプライトの説明が保存される場所です。

- I / Oポート。 ここで、他のDMGコンポーネントのレジスタにアクセスできます。

- 内部RAM 2. DMG内のRAM。

- 割り込みイネーブルレジスタ。 このレジスタは、特定の割り込みの処理を有効にするフラグを格納します。 これは、すでに説明したものと同じIEレジスタです。

エミュレータのアーキテクチャは各DMGコンポーネントが独自のクラスを持っていることを前提としているため、メモリをエミュレートするCookieboy :: Memoryクラスには、ROMバンク、内部RAM 1、内部RAM 1のエコー、切り替え可能なRAMバンク、内部RAMのみが含まれます2.他のすべての領域にアクセスすると、対応するクラスのアクセスメソッドが呼び出されます。

メモリ内の読み取りおよび書き込み操作から始めましょう。 すべてが非常に簡単です-アドレスを見て、対応するメモリ領域に操作をリダイレクトします。 私は次のようにしました。 ご覧のとおり、多くのメモリ領域が適切に配置されているため、スイッチと論理演算を使用してすべてを実装できます。 これは次のようなものです。

switch (addr & 0xF000) { case 0x8000: case 0x9000: // break; }

そして、かさばる条件構造はありません。 現時点では、メモリの一部の領域はまだ実装されていない他のクラス(ビデオメモリなど)にあるため、空白のままにすることができます。 Cookieboy :: Memoryにあるものだけを実装できます。 ここでは、ROMバンクと切り替え可能RAMバンクに注意する価値があります。

ROMを取り外したカートリッジにMBCコントローラーが含まれていた場合、これらのメモリー領域にこれらのコントローラーのロジックを実装する必要があります。 これは非常に簡単に実行できます。これらの領域へのアクセスは、対応するMBCコントローラーによって実装されるクラスにリダイレクトされ、どこで、どのように、何を決定できるようになります。 MBC 2とMMM01の2つの例を見てみましょう。 最初の例は、残りの実装を可能にする例です。 MMM01はかなり奇妙なMBCです。 , MBC. DMG.

MBC. :

const int ROMBankSize = 0x4000; const int RAMBankSize = 0x2000; class MBC { public: virtual void Write(WORD addr, BYTE value) = 0; virtual BYTE Read(WORD addr) = 0; virtual bool SaveRAM(const char *path, DWORD RAMSize); virtual bool LoadRAM(const char *path, DWORD RAMSize); protected: MBC(BYTE *ROM, DWORD ROMSize, BYTE *RAMBanks, DWORD RAMSize) : ROM(ROM), ROMSize(ROMSize), RAMBanks(RAMBanks), RAMSize(RAMSize) {} BYTE *ROM; BYTE *RAMBanks; DWORD ROMOffset; DWORD RAMOffset; DWORD ROMSize; DWORD RAMSize; };

, – Cookieboy::Memory. RAM. , . – RAMBanks , . :

- ROM. .

- RAMBanks. .

- RAMOffset ROMOffset. , .

- ROMSize RAMSize, , . , .

, , MBC2. , , :

class MBC2 : public MBC { public: MBC2(BYTE *ROM, DWORD ROMSize, BYTE *RAMBanks, DWORD RAMSize) : MBC(ROM, ROMSize, RAMBanks, RAMSize) { ROMOffset = ROMBankSize; RAMOffset = 0; } virtual void Write(WORD addr, BYTE value) { switch (addr & 0xF000) { //ROM bank switching case 0x2000: case 0x3000: ROMOffset = value & 0xF; ROMOffset %= ROMSize; if (ROMOffset == 0) { ROMOffset = 1; } ROMOffset *= ROMBankSize; break; //RAM bank 0 case 0xA000: case 0xB000: RAMBanks[addr - 0xA000] = value & 0xF; break; } } virtual BYTE Read(WORD addr) { switch (addr & 0xF000) { //ROM bank 0 case 0x0000: case 0x1000: case 0x2000: case 0x3000: return ROM[addr]; //ROM bank 1 case 0x4000: case 0x5000: case 0x6000: case 0x7000: return ROM[ROMOffset + (addr - 0x4000)]; //RAM bank 0 case 0xA000: case 0xB000: return RAMBanks[addr - 0xA000] & 0xF; } return 0xFF; } };

. ROMOffset ROM. . MBC2 512 4- RAM. , , 512 , 4 .

. MBC. MBC2 ROM. 4 0x2000-0x3FFF. , .. 0x0000-0x3FFF. ROM. , . , , . , . WordZap. ( DMG , , ), .

, 0xFF – DMG , .

, MMM01. , , . コード:

class MBC_MMM01 : public MBC { public: enum MMM01ModesEnum { MMM01MODE_ROMONLY = 0, MMM01MODE_BANKING = 1 }; MBC_MMM01(BYTE *ROM, DWORD ROMSize, BYTE *RAMBanks, DWORD RAMSize) : MBC(ROM, ROMSize, RAMBanks, RAMSize) { ROMOffset = ROMBankSize; RAMOffset = 0; RAMEnabled = false; Mode = MMM01MODE_ROMONLY; ROMBase = 0x0; } virtual void Write(WORD addr, BYTE value) { switch (addr & 0xF000) { //Modes switching case 0x0000: case 0x1000: if (Mode == MMM01MODE_ROMONLY) { Mode = MMM01MODE_BANKING; } else { RAMEnabled = (value & 0x0F) == 0x0A; } break; //ROM bank switching case 0x2000: case 0x3000: if (Mode == MMM01MODE_ROMONLY) { ROMBase = value & 0x3F; ROMBase %= ROMSize - 2; ROMBase *= ROMBankSize; } else { if (value + ROMBase / ROMBankSize > ROMSize - 3) { value = (ROMSize - 3 - ROMBase / ROMBankSize) & 0xFF; } ROMOffset = value * ROMBankSize; } break; //RAM bank switching in banking mode case 0x4000: case 0x5000: if (Mode == MMM01MODE_BANKING) { value %= RAMSize; RAMOffset = value * RAMBankSize; } break; //Switchable RAM bank case 0xA000: case 0xB000: if (RAMEnabled) { RAMBanks[RAMOffset + (addr - 0xA000)] = value; } break; } } virtual BYTE Read(WORD addr) { if (Mode == MMM01MODE_ROMONLY) { switch (addr & 0xF000) { //ROM bank 0 case 0x0000: case 0x1000: case 0x2000: case 0x3000: //ROM bank 1 case 0x4000: case 0x5000: case 0x6000: case 0x7000: return ROM[addr]; //Switchable RAM bank case 0xA000: case 0xB000: if (RAMEnabled) { return RAMBanks[RAMOffset + (addr - 0xA000)]; } } } else { switch (addr & 0xF000) { //ROM bank 0 case 0x0000: case 0x1000: case 0x2000: case 0x3000: return ROM[ROMBankSize * 2 + ROMBase + addr]; //ROM bank 1 case 0x4000: case 0x5000: case 0x6000: case 0x7000: return ROM[ROMBankSize * 2 + ROMBase + ROMOffset + (addr - 0x4000)]; //Switchable RAM bank case 0xA000: case 0xB000: if (RAMEnabled) { return RAMBanks[RAMOffset + (addr - 0xA000)]; } } } return 0xFF; } private: bool RAMEnabled; MMM01ModesEnum Mode; DWORD ROMBase; };

, . – , , . , MMM01 2 , .

, I/O ports. なぜなら DMG , - . I/O ports DMG: , , , .. , , Cookieboy::Memory . CPU Manual. . , – IF. , Cookieboy::Interrupts. , .. .

– ROM . , DMG.

Bootstrap ROM', DMG. Cookieboy::Memory. , Nintendo. 256 , 0 – .. PC . , 0xFF50. , , – Bootstrap ROM' . , . , .

. Bootstrap ROM , . , ROM, .

, DMG . , . – . , . , . .

, . . PC 0x100 – . , I/O ports , Bootstrap ROM – CPU Manual. , , , Bootstrap ROM. EmulateBIOS, .

, . , . ( MBC-) . CPU Manual. , Bootstrap ROM. , DMG. – Nintendo. ROM Nintendo, Bootstrap ROM. . – CPU Manual. . :

BYTE Complement = 0; for (int i = 0x134; i <= 0x14C; i++) { Complement = Complement - ROM[i] - 1; } if (Complement != ROM[0x14D]) { // }

, MBC .

, , «», . MB, , , .

, .